IMEC对EUV工艺未来的思考

2019-08-22

14:41:53

来源: 互联网

点击

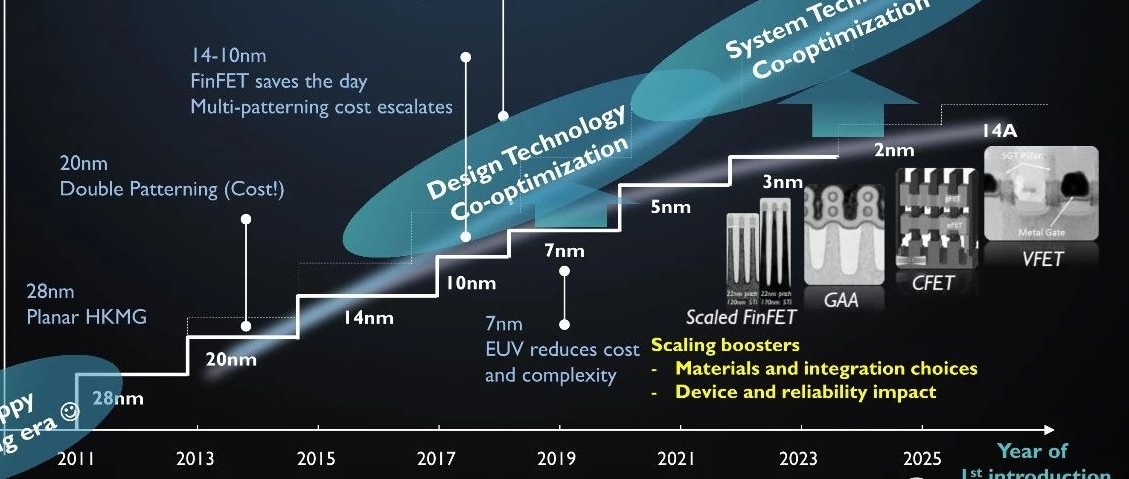

2019年,EUV光刻(EUVL)将达到一个重要的里程碑。经过多年的等待,先进光刻技术终于进入大批量生产。EUVL将率先用于7nm节点(IMEC N8或代工厂N7)逻辑后段(BEOL)的最关键金属层和通孔。与此同时,研究中心正在探索未来技术节点的选择,这些节点将逐步纳入更多的EUVL印刷结构。在本文的第一部分,imec的干法蚀刻研发工程师Stefan Decoster比较了在N3及更先进技术节点下,不同的多重图形化方案的优缺点。

在后段引入EUV多重显影

从EUV单次显影到EUVL多重显影

IMEC N5技术节点的多重显影方案

IMEC N5以下:16 nm节距的图形化方案

三种图形化flow可实现16nm节距图形(自上而下的SEM图):(顶部)基于EUV的SADP,(中)基于EUV的SAQP和(底部)193iSAOP。所有三个选项的LER均在8nm line和space的情况下测得。

(左)展示阻值状态和允许的变化范围;(右)MTJ的X-SEM截面图。

(左)展示阻值状态和允许的变化范围;(右)MTJ的X-SEM截面图。

tone反转过程的图示:(左)用正toneCAR光刻胶获得的孔和(右)在tone反转后获得的柱。

tone反转过程的图示:(左)用正toneCAR光刻胶获得的孔和(右)在tone反转后获得的柱。

与过去相比,研究人员现在已经将EUVL作为存储器关键结构的图形化工艺的一个选项,例如DRAM的柱体结构及STT-MRAM的MTJ。在本文的第二部分,IMEC的研发工程师Murat Pak提出了几种STT-MRAM关键结构的图形化方案。

在后段引入EUV多重显影

今年,一些主要的代工厂将首次在其大批量生产线中使用EUVL来处理逻辑7nm(N7)芯片。它们将EUVL引入BEOL的最关键金属层(local M0至M3),以及互连这些金属层的过孔中。在这些层中,线和沟槽具有36-40nm量级的节距。沟槽与沟槽的隔断相互垂直,以便在连续沟槽中产生隔断。下一个技术节点N5会运用到28到32nm之间的金属节距。

“2017年,我们已经证明这些32nm节距线可以在一次曝光中直接用EUVL进行图形化,”Stefan Decoster补充道。“或者,可以使用混合选项,其中基于193i的SAQP与EUV block相结合。”

图示采用193nm浸入式SAQP图形化的32nm节距M2层,以及直接由EUV图形化制作的隔断(block)。

从EUV单次显影到EUVL多重显影

同时,很明显,EUVL单次曝光已经达到了32纳米到30纳米节距的极限。StefanDecoster:“超过30nm节距,使用当前的EUVL技术(即0.33数值孔径(NA))需要采用多重图形化技术,进一步缩小尺寸。这些技术通常涉及将芯片图案分成两个或更多个更简单的掩模,并且可以以不同的风格存在。EUV多重显影将比原先想象的更早推出, 主要是由于存在随机失效。“这些失效在极小的特征尺寸下开始变得更加明显,并且限制了EUV单次曝光的实际分辨率。

IMEC N5技术节点的多重显影方案

在实践中,这意味着IMEC N5(或代工厂N3)技术节点具有21nm的金属节距,这需要EUVLmulti-patterning,例如SADP或LELE,当然,IMEC还提供了另外两种方案,即193iSAQP,193i SAOP,仍然可以实现这些尺寸的线和沟槽。在成本,光刻质量和工艺流程的复杂性方面,这些技术中的每一种都具有其自身的优点和缺点。

“然而,EUVL single patterning 并不止步于此,”Stefan Decoster澄清道。“我们预计更松弛的金属层(例如M4至M7层)和关键过孔仍然可以利用EUVL单次曝光来实现。此外,IMEC和ASML正在开发下一代high-NAEUVL系统(NA =0.55),以进一步提高单次曝光的分辨率。”

IMEC N5以下:16 nm节距的图形化方案

IMEC的研究人员探索了四种不同的图形化方案,用于制作20nm节距以下的图形:基于193i的SAOP方案,基于EUV的SADP方案,基于EUV的SAQP方案和EUV SALELE方案。Stefan Decoster:“这四种方案都可以制作16nm节距的线。然而,它们在流程复杂性,成本,可扩展性和设计自由度方面存在差异,这些都是行业的重要考虑因素。我们还发现,线边缘粗糙度(LER)仍然是主要关注点。”

193nm 浸没式光刻仍然可以完成这项工作

在这些激进的节距下,193nm浸没式光刻只能与SAOP结合使用 ,从128nm节距开始经历三次图形倍增最终达到16nm节距。Stefan Decoster指出,193i SAOP的优点是线条边缘粗糙度(LER)小,但一个固有的缺点是极其漫长而复杂的工艺流程,这给过程控制和成本带来了挑战。

使用EUVL multi-patterning可以使flow变短

“出于这个原因,我们还探索了'较短的'基于EUVL的图形化方案,即EUV的SADP”,StefanDecoster补充道,“为了实现这种图形化方法,EUV光刻的起始节距必须为32nm。虽然目前的EUVL技术仍然能够制作32nm节距线,但是所得到的线宽不能小于16nm。因此,我们不得不应用额外的trim技术来实现在32nm节距下8nm的线宽(mandrel)。采用SADP技术,这种间距可以成功地降低到16nm。”16 nm节距的图形也可以采用更具可扩展性的EUVL SAQP方法,从更宽松的64nm节距开始。然而,对于这些基于EUV的多重图形化方法,线边缘粗糙度(LER)仍然是一个重要问题。该团队认为,这种LER可以进一步降低,例如通过选择恰当的光刻胶材料和改善光刻胶平滑性。

三种图形化flow可实现16nm节距图形(自上而下的SEM图):(顶部)基于EUV的SADP,(中)基于EUV的SAQP和(底部)193iSAOP。所有三个选项的LER均在8nm line和space的情况下测得。

eSALELE:一种全新的工艺整合方案

前面三种多图案化方法都有一个共同点:首先,制作线和沟槽,然后添加隔断(block,例如使用自对准隔断方法)。IMEC团队还研究了一种使用EUVL的不同方法 ,称为eSALELE,其中线和隔断在整个相同的流程中定义。除了相对较高的LER之外,这种方法的另一个缺点是使用四个EUV掩模(两个用于线,两个用于隔断),这使得这个方案非常昂贵。Stefan Decoster说:“但eSALELE方法的主要优点是设计灵活,可以避免'虚设'(dummy)金属线(版图中并不真正需要的金属线)。避免这些线的出现有利于RC延迟和后段功耗的降低。

EUVL单次曝光与存储器:STT-MRAM的情况

由于其高写入和读取速度,STT-MRAM最近成为取代基于SRAM的最后一级高速缓存存储器的可能选项。STT-MRAM器件的核心结构是柱状MTJ,其中绝缘层夹在两个薄的铁磁层之间,所述铁磁层分别是钉扎层和自由层。MTJ可以以两种不同的电阻状态存在:低阻态(LRS,两个磁层的磁化平行)和高阻态(HRS,磁化处于反平行状态)。通过利用注入磁隧道结的电流切换自由磁层的磁化来执行存储单元的写入。读取操作依赖于隧道磁阻(TMR),其是两个阻值状态之间的电阻差的函数。

从193i到EUVL单次曝光

到目前为止,MTJ已经用193i图形化实现了200nm节距,当然之后的100nm节距也是。IMEC的研发工程师Murat Pak说:“但是为了满足未来存储器的高密度要求,我们需要更紧密的节距,例如50nm或更小,MTJ直径约为20nm。193i无法实现这么激进的节距,这凸显了引入EUVL单次曝光的必要性。“

LCDU会是最关键的指标

然而,在这么小的尺寸下,粗糙度和随机失效的影响不可以被忽略,因此需要改进的图形化方案。“对于这种存储器而言,最关键的参数结果是局部CD均匀性(LCDU),这是柱粗糙度的一种度量,”Murat Pak解释说。“这种LCDU显然会影响电阻值,从而影响STT-MRAM单元的读取性能。因此,确保良好的LCDU对于STT-MRAM制造至关重要。”

(左)展示阻值状态和允许的变化范围;(右)MTJ的X-SEM截面图。

(左)展示阻值状态和允许的变化范围;(右)MTJ的X-SEM截面图。 为了优化MTJ的LCDU,已经提出并比较了不同的EUV光刻方案。MuratPak:“首先,我们考虑了不同的光刻胶,包括众所周知的化学放大胶(CAR),以及两种不同的MCR(含金属)光刻胶。其次,我们的团队筛选了不同的底层包括旋涂碳(SOC)和旋涂玻璃(SOG),并研究了它们对光刻胶性能的影响。最后,我们研究了不同的tonalites(相当于正胶和负胶的区别,编者注),特别是CAR光刻胶(做柱)和positive tone光刻胶加上tone反转工艺(将孔变成柱)。“该团队还研究了光刻胶上的LCDU的改进是否会转移到了蚀刻之后。以上所有实验中的EUV都使用ASMLTWINSCAN NXE:3300B进行曝光。

tone反转过程的图示:(左)用正toneCAR光刻胶获得的孔和(右)在tone反转后获得的柱。

tone反转过程的图示:(左)用正toneCAR光刻胶获得的孔和(右)在tone反转后获得的柱。三种有可能的方案(如下图,由编者添加)

其中一支MCR光刻胶搭配SOC和SOG均获得了相对较好的LCDU结果。第三种方案是tone反转工艺 ,最终也表现良好。“对于所有这三种方法,我们获得了超过20%的LCDU的改进,”Murat Pak补充道。“这是整个工艺流程朝向1.55nm LCDU目标的重要一步。”对于这些有前景的光刻工艺方案,其他性能指标,如工艺窗口分析,柱圆度和尺寸均匀性均已通过验证。

总结

在本文中,已经针对未来的逻辑和存储器件(即,SST-MRAM)应用提出了各种EUVL图形化方法。对于逻辑,基于EUV的SADP,基于EUV的SAQP和基于EUV的SALELE与基于193i的SAOP的性能进行了比较。所有选项都有可能用于制作如16nm节距这样具有挑战性的金属线。但是,必须在工艺复杂性,成本,设计自由度和线边粗糙度方面进行权衡。

对于SST-MRAM,已经确定了三种不同的基于EUV的制作50nm节距的MTJ柱的方法,并且具有足够好的LCDU。

责任编辑:sophie

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 探索智慧实践,洞见AI未来!星宸科技2024开发者大会暨产品发布会成功举办

- 2 在这个平台上,硬件创新跑出了“中国速度”

- 3 国产EDA突破,关键一步

- 4 思尔芯第八代原型验证S8-100全系已获客户部署,双倍容量加速创新