这项新存储技术正在挑战 SRAM

来源:内容编译自semiengineering,谢谢。

SOT-MRAM技术的主要优势是可以实现更快的写入速度和更长的耐用性。与任何新技术一样,在成本和复杂性方面存在挑战,而且看起来很有吸引力的技术仍然可能无法实现大规模采用。但随着研究的继续,当技术商业化时,其中一些缺点可能会得到解决。

“使用 SOT-MRAM,由于它使用了不同的机制,其写入性能是上一代 STT-MRAM 的 10 倍,” Synopsys嵌入式存储器技术营销经理 Mingchi Liu 说。“而且它将在寿命可靠性方面具有优势。”

MRAM是当今进入商业生产的众多非易失性存储器技术之一。早期版本,称为切换 MRAM,已经存在了一段时间,最新的商用选项是自旋转移扭矩,或STT-MRAM。

MRAM 加入了其他技术的行列,将闪存从其NVM基座上敲下来。到目前为止,闪存仍然提供最低的每比特成本——对任何新手来说都是一个障碍——但它有一些缺点,例如编程时间长以及需要一次编程和擦除大块数据。后者使闪存管理更加复杂。在对单元进行编程时也消耗大量能量,并且很难嵌入逻辑。

与闪存相比,STT-MRAM 承诺更低的功耗和更快的写入时间。但这需要在速度和耐用性之间进行权衡,这表明不同的设备可能更适合不同的市场,其中一些设备针对性能进行了调整,而其他设备针对需要许多写入周期的应用程序进行了调整。

SOT-MRAM 有望消除这种折衷。“使用 STT,您必须放弃保留或持久性,”Antaios 创始人兼首席执行官 Jean-Pierre Nozières 说。“在这里你可以获得耐力、保持力和高速。”

当然,更换SRAM是一项艰巨的挑战。“SRAM 可以在任何逻辑芯片上实现,无需任何额外的处理步骤,它是最快的存储器之一,可以在运行中实现高能效(如果有泄漏),”DDR、HBM、闪存产品营销集团总监 Marc Greenberg 说Cadence的 /storage 和 MIPI IP 。“但它也是面积效率最低的之一,而且不稳定。”

SOT-MRAM 应该提供一些区域缓解并增加波动性。虽然它不能取代最快的 SRAM,但它可能有助于使用速度较慢的 SRAM 的更大阵列。

了解 SOT-MRAM 如何应对这些挑战需要讨论基本位单元的工作原理——更重要的是,它是如何编程的。

现代 MRAM 器件采用所谓的磁隧道结 (MTJ)。它可以简化为具有三层——固定或“钉扎”磁性层、隧道电介质和自由磁性层。

在对设备进行编程时,将自由层的磁场设置为与固定层的磁场平行或反平行。这个想法是,固定层有效地过滤了通过它的电流的自旋方向。当该电流撞击另一个磁性层时,如果它的方向相同,则可以通过更多电流。如果方向相反,则通过的电流更少。

图 1:读取电流的大小取决于两个磁性层的相对方向,从而确定了电池的状态。 资料来源:Bryon Moyer/Semiconductor Engineering

在 STT-MRAM MTJ 中通过运行大电流通过 MTJ 对单元进行编程。方向决定了自由层的编程方式。更新的程序“更难”,从而实现更快的访问时间。但它也会对细胞造成损害,从而导致磨损。如果需要更高的耐用性,则写入电流必须更低,从而减慢该过程。

“目前的缺点是它的写入速度比读取速度慢 10 倍,”刘说。“因为性能慢,要替换 SRAM 会很困难。”

图 2:使用大于流经 MTJ 的读取电流的写入电流对 STT-MRAM 单元进行编程,这会对单元造成长期损坏。 资料来源:Bryon Moyer/Semiconductor Engineering

SOT-MRAM 具有不同的写入路径,电流沿 MTJ 底部(平面内)流动,而不是通过它。这将编程与读取路径分离,并消除了 STT-MRAM 编程可能发生的损坏。这需要一个新层,通常称为带,编程电流将流过该层。

图 3:SOT-MRAM 单元使用沿条带流动的电流进行编程,消除了 MTJ 损坏。在这种情况下,自由层往往位于底部以靠近表带。 资料来源:Bryon Moyer/Semiconductor Engineering

SOT 技术存在两个基本挑战,仍然是许多研究和开发的主题。第一个处理写入时对外部磁场的需求。第二个与位单元的大小有关。

无磁场切换

第一个挑战与如何设置确定性磁场方向有关。从最纯粹的意义上说,编程机制涉及一些随机因素,对于给定的磁畴,很难控制磁场的走向。

至少有两种方法可以完成这种控制。一种是制作不对称形状的表带,但这会影响细胞面积。另一种是外加磁场,缺点很明显。

虽然外部场方法的商业发展一直在向前发展,但研究人员已经确定了执行所谓的“无场”切换的潜在方法。对于那些不熟悉材料、表面状态、自旋指数、 Dzyaloshinskii-Moriya 效应、Rashba 效应和许多论文中出现的其他奥秘的人来说,新兴的解决方案很难理解。

但是研究人员 [1,2] 发现,通过将正确的金属与铁电或铁电材料的正确组合以及正确的自旋指数关系夹在中间,可以打破磁对称性以驱动所需的方向。

普遍的期望似乎是,当商业设备出现时,它们将能够进行无场切换。

减小位单元尺寸

一个更具挑战性的问题是,虽然 STT 单元有两个终端供读取和写入电流共享,但 SOT 单元有三个终端,因为写入电流有自己的路径。这意味着另一个选择晶体管。这是默认配置,它比 STT 拥有更大的位单元。额外的晶体管是更大尺寸的主要原因。

“除了一个非常重要的因素——面积成本外,SOT 在任何地方都优于 STT,”Nozières 说。“我们的目标是实现 SRAM 一半的面积。您可以通过零泄漏和更简单的外围设备做到这一点,因为不需要睡眠和唤醒模式等。”

图 4:STT 使用一个两端单元,而 SOT 需要一个额外的端子来提供写入电流。 资料来源:Bryon Moyer/Semiconductor Engineering

STT 和 SOT 位单元之间的差异可能没有人们想象的那么大。Antaios 的董事会成员兼顾问 Barry Hoberman 说,事实上,这还不到人们可能直觉假设的 50% 的增长。

使用 STT,写入路径由选择晶体管和高电阻 MTJ 组成。在 SOT 中,它是选择晶体管和低电阻带。因此,对于 STT,晶体管面临着降低电阻的压力——这意味着它需要更宽。

SOT 晶体管没有相同的压力,因此它的尺寸可以更小——足以减少位单元尺寸差异。具体大小和当前数字仍然是专有的。

尽管如此,SOT 单元仍然比 STT 单元大,因此正在努力减少这种影响。论文中提出了电路技术和更复杂的想法,展示了消除其中一个端子的方法,我们将讨论其中的几个示例。在这一点上,这些似乎只是想法,尚不清楚它们是否会商业化。

来自 CEA Tech、艾克斯马赛大学、格勒诺布尔阿尔卑斯大学和 CEA Leti 的 2018 年论文 [3] 展示了两种可能的电路方法,其中一种涉及通过 MTJ 的一些泄漏。这些并没有消除第三个端子,但它们将选择晶体管的数量分别减少到 1 和 0。

图 5:两个提议的电路,它们消除了一个或两个选择晶体管以减小位单元尺寸。左侧,读写路径共享,写入时有小电流流过MTJ;大部分电流通过选择晶体管,因为它具有较低的电阻。在右边,有单独的读写路径,没有选择晶体管。(论文中有些细节不清楚。) 来源:Bryon Moyer/Semiconductor Engineering 基于源文件。[3]

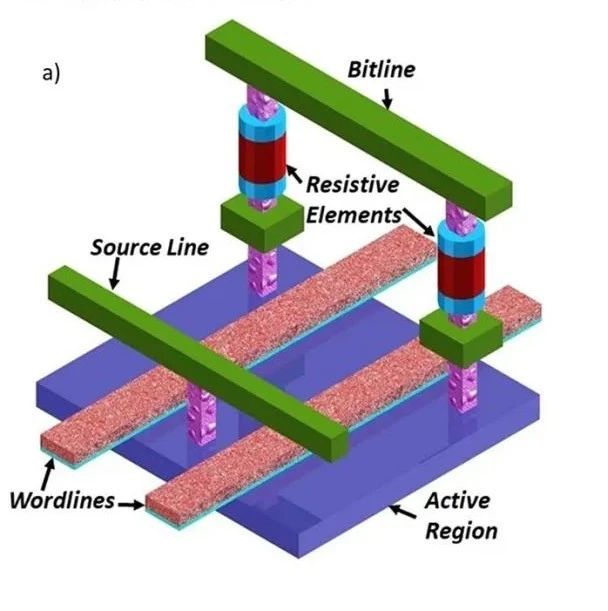

新加坡国立大学、印度理工学院和高丽大学 [4] 也开展了工作,提出了一种共享单行中所有单元的写入终端的方法,从而无需每个单元都有它自己的写终端。

该机制很微妙,涉及磁性叠层上方的栅极材料,该材料可以从自由层中积累或去除氧离子。这些离子的存在与否决定了带和自由层界面处自旋积累的极性。以这种方式,使用一个方向的电流加上每个单元的栅极电压——这不占用存取晶体管所需的面积——线上的每个单元都可以被编程到它自己的状态。

图 6:氧化钆层包含氧原子(黄色圆圈),在正电压的影响下,氧原子可以迁移到钴中,在钴/铂界面处建立一个自旋极性。负电压将氧气拉回,从而产生相反的界面极性。 资料来源:Bryon Moyer/Semiconductor Engineering 基于源文件。[4]

此时的挑战是这些离子的迁移时间很长,会影响写入访问时间,所以目前这是概念性的。它是否可以演变成一种商业上可行的机制来缩小比特单元还有待观察。

从长远来看,还有其他想法。“更激进的方法走得更远,使 SOT 尺寸小于 STT,但这需要时间,而且还没有真正出现,”Nozières 说。

访问时间对称性

另一个问题是读取和写入位单元的访问时间。SOT 技术改变了写入机制,可以在不损害耐力的情况下快速写入。“我们相信我们可以在 3 到 10 ns 之间的任何时间运行这个东西,”Nozières 说。

但读取机制保持不变。因此,虽然现在 SOT 的写入时间比 STT 更快,但读取时间并没有变化。

虽然原则上更快的写入可能听起来不错,但尚不清楚写入时间比读取时间快是否有价值。平均而言,记忆的阅读次数要比写入次数多得多。因此,提高读取速度比提高写入速度对整体性能的影响更大。

一些人认为最好的安排是对称的,即读写时间相同。Nozières 同意:“实际上,您希望阅读时间是对称的。”

这最终可能会放弃 SOT 技术带来的一些写入速度增益,但对称性旨在提供“足够好”的写入时间。

测试磁场

最近也有一些测试设备公告支持 SOT-MRAM。必要的发展与外部磁场和写入时间有关。今天可用的设备更多地专注于开发而不是商业大批量生产,因此它需要能够完成生产测试仪中可能需要或不需要的事情。

其中一项能力涉及外部磁场。今天,应用该领域的能力是必要的。但是,即使无场编程成为商业现实,仍然需要这个场来进行表征甚至全面测试。

与任何其他参数一样,给定位单元的磁特性会受到制造变化的影响。必须测量位单元的固有磁特性,并且这是通过外部场完成的。事实上,在存在外部场的情况下测试阵列的稳定性意味着确定矫顽场——即,编程状态对其他附近场的支持程度。

“通过 STT,我们改变了 MTJ 顶部的磁场,然后我们可以翻转设备的状态,”Hprobe 的首席技术官兼联合创始人 Siamak Salimy 说。“从中我们提取矫顽力场,然后是各向异性场。我们对 SOT 做同样的事情,但我们需要一个 2D 磁场,而 STT 只需要 1D。”

Nozières 解释了磁各向异性的概念。“这是磁化想要的首选方向,”他说。“希望是单轴的,这可以实现两种状态,具体取决于沿该轴的方向。它代表磁铁的“刚度”。矫顽力是克服各向异性并从一个方向切换到另一个方向所需的磁场值。在理想世界中,它与各向异性相同。然而,材料有缺陷,矫顽力总是低于各向异性,有时甚至远低于各向异性。”

因此,测试人员可能需要能够以精确和快速的方式应用和调整本地字段。精确地获得已知场是困难的,因为场可能因位置而异——尤其是在使用探针卡时。

ISI 总裁兼首席执行官 Henry Patland 解释说:“探针在接触焊盘时会进行一些擦洗,因此接触点会因位置而异。” “而且晶圆本身并不是完全平坦的。我们将磁铁与探针卡集成在一起,因此在定位晶圆期间,当我们接触探针卡时,我们在一个均匀的磁场中工作。”

ISI 副总裁兼首席运营官 Wade Ogle 说:“我们通常将自己限制在 1 毫米左右的均匀场。” “我们可以并行测量多达 8 个设备,并且仍然在统一场内。”

高速测试脉冲

测试头上的模拟电路也必须改进。必须生成短至 200 ps 的编程脉冲,至少目前是这样,因为在启动之前对位单元进行了评估和改进。这比过去所需的时间要短。

但是还有一个更难的附带功能。SOT 器件的重点是使用平面内电流而不是垂直电流进行编程的能力。在测试和表征设备时,需要确保所有编程都通过该平面内路径进行。必须抑制通常用于 STT 的垂直路径,以确保没有任何编程来自任何杂散 STT 电流。

“我们希望通过 SOT 最大限度地实现器件的切换,并尽量避免电流流过 STT 通道,”Salimy 说。“为此,我们需要应用极其同步的脉冲,以确保当脉冲位于 MTJ 柱的底部时,我们在另一侧具有完全相同的幅度。”

在测试环境中生成这些类型的脉冲可能特别困难。“我们正在通过一根 1 米长的电缆将 500 ps 脉冲发送到未端接的高阻抗设备中,”Patland 说道。他们脉冲 MTJ 的方式似乎有点不同,但想法是一样的——消除通过 MTJ 的任何电流。

因此,在测试芯片上,测试仪必须能够在两个信号上生成准确的脉冲,并在 10 皮秒内使它们同步。在商业电路上,这些脉冲将在内部产生。此外,一些技术使用“STT 辅助”,其中小的 STT 电流支持 SOT 机制,从而降低整体写入电流。但是晶圆验收测试的测试结构可能仍然需要这种能力。

最大的问题是 SOT-MRAM 可以在哪些方面获得关注。仅仅基于成本,它或任何新的 NVM 都很难与 NAND 闪存或 DRAM 竞争。

“尽管 DRAM 和 NAND 已经高度优化,可能无法以相同的新存储器速度取得新的进展,但它们受益于一些全球最大的半导体公司在一个销售数百亿芯片的市场上进行了数十年的技术投资。每年每项技术的产品价值,”格林伯格警告说。“已经花费了大量资金来优化 DRAM 和 NAND,达到今天的水平。因此,即使一项新技术每年进步 20%,要赶上 DRAM 和 NAND 仍有很长的路要走。”

在一两件事上做得更好可能会有所帮助,但总的来说,闪存和 DRAM 的成熟度以及它们不断发展的事实可能会使专用 MRAM 芯片超出经济范围。

格林伯格补充说:“在某些指标上,新奇的记忆要击败既定的记忆还不够好。” “它几乎必须在带宽、延迟、容量、成本、功率和耐用性等所有关键指标上击败 DRAM 或 NAND。”

安泰奥斯似乎对此没有任何幻想。“就像今天的技术一样,专用芯片似乎遥不可及,因为在成本方面它永远无法与 DRAM 竞争。”

然而,作为嵌入式存储器,情况有所不同。嵌入式闪存和 DRAM 都很困难,需要许多额外的处理步骤。MRAM 需要更少的额外步骤,并且在很大程度上与 CMOS 逻辑工艺兼容。

CyberOptics总裁兼首席执行官 Subodh Kulkarni 表示:“有些商业芯片使用 MRAM 来实现其独特的价值主张,尽管功能比 DRAM 或 NAND 更大。”

从处理的角度来看,SOT 不需要 STT 不需要的任何东西,但有一个例外,因此运行 STT 的代工厂也应该能够运行 SOT。那个例外是可能提供无场编程的金属层。有些人认为它与已知的晶圆厂友好金属足够接近,因此不会成为问题。但它是一种新材料,因此有可能在那里进行一些额外的限定。

作为嵌入式存储器,SOT 可能会也可能不会直接与 STT 竞争。“我很确定,首先,SOT 将补充 STT,”Nozières 说。“制造环境、材料、工艺、设备都是一样的。没有什么能阻止代工厂向所有客户提供 MRAM 的 A 类和 B 类。”

在这种情况下,它更有可能与 SRAM 竞争。SOT-MRAM 和 SRAM 的能耗大致相当。但是 SRAM 在速度上仍然具有优势,因此 SOT-MRAM 可能仍然无法实现第一级缓存。

“第一层缓存将它们置于 300 ps 的周期时间范围内,”Hoberman 说。“这完全是 MOS 的领域——而且可能会持续很长时间。”

最后一层缓存似乎是一个机会,而密度对于该应用程序来说是一个好处。如果能够以所需的写入速度实现耐用性,STT-MRAM 理论上可以在那里发挥作用。但是系统设计人员已经习惯了 SRAM 的无限耐用性,因此即使不得不考虑耐用性也会成为负面因素。“有了 SRAM,没有人会质疑它的寿命,”刘说。

已经讨论了 STT 的简单刷新功能以换取较低的数据保留。这可能使其适用于最后一级缓存,因为那里的数据生命周期相对较短。

“如果您想使用嵌入式 MRAM 替换 SRAM,您是否关心数据保留?” 刘问。“如果它可以保存一天的数据,就足够了吗?其实,一天太长了。也许仅仅一小时就足够了。而且系统每分钟都会完全刷新。”

以这种方式,STT 和 SOT 可能会相互竞争,因为刷新的复杂性会与较小的位单元大小进行权衡。再说一次,如果刷新以易于使用的方式完成,并且不会过多增加裸片成本,那么它可以像今天的 DRAM 刷新那样被容忍。

物联网设备将是另一回事。“[STT with refresh] 绝对不适合需要保留数据的物联网,”Liu 指出。

他们还需要尽可能降低功率,因为其中许多都使用小型电池。“SOT 的每比特写入能量大约比 STT 低一个数量级,”Hoberman 说。非易失性也是一个优点,因为系统状态可以在电源循环中存活。这有可能加快启动时间。

EDA进入中国的意义还有几年时间

这些好处是否会在某些应用中支持 SRAM,暂时还不得而知。SOT-MRAM 开发仍在继续,但需要一些时间。“我认为该技术不会在 2024 年之前为客户提供样品,”Nozières 说。

根据一些估计,这是一个乐观的时间表。

备注:

1.“通过竞争自旋电流切换垂直铁磁层”,Ma 等人,约翰霍普金斯大学

2.“具有垂直成分梯度的亚铁磁层中的无场自旋轨道转矩引起的垂直磁化切换”,郑等人,北京航空航天大学。

3.“ MRAM:从 STT 到 SOT,用于安全性和内存,”Kharbouche-Harrari 等人,CEA 等人。

4.“用于高密度自旋轨道扭矩磁随机存取存储器的基于共享写入通道的设备”,Mishra 等人,IIT 德里

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2921内容,欢迎关注。

推荐阅读

★ 成熟制程闹翻天

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 江波龙全球最小尺寸eMMC,为AI穿戴设备“减负”

- 2 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 3 Solidigm宣布与博通拓展大容量SSD控制器在AI领域的应用合作

- 4 英伟达,又挖了一道护城河