汽车电子架构升级:汽车级IP助力ADAS和IVI融合

2024-04-17

14:03:00

来源: 互联网

点击

汽车行业正经历着向集中式电气/电子(EE)架构的重大转变,这将深刻影响汽车制造商、一级和二级供应商在未来10年内的战略布局和产品研发。产业链上下游都在研究并尝试在单个 SoC 或多芯片设计上实现高度集成的功能。早在 2021 年,采埃孚电子/ ADAS 产品执行副总裁 Christophe Marnat 就表示:"集中化的趋势已经出现,我们看到所有的原始设备制造商现在都在研究这个问题。”博世和高通最近也宣布,将在单个 SoC 上提供一个中央车载计算模块,用于托管数字驾驶舱(或 IVI)和 ADAS 应用。博世的数字驾驶舱和 ADAS 集成平台采用了 Snapdragon Ride Flex SoC。而高通的 SoC 专为支持混合临界工作负载而设计,可同时执行数字驾驶舱和 ADAS 功能。

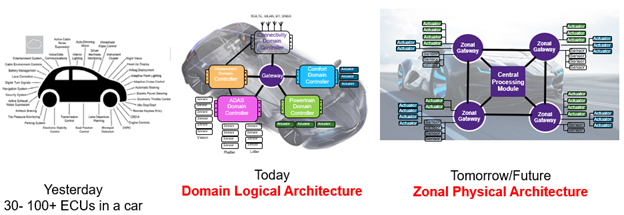

从分布式 ECU 和基于域的架构向集中式 EE架构 (基于区域的系统)的过渡对汽车行业产生了重大影响。在这一发展过程中,采用汽车级接口和处理器 IP 的集中式计算 SoC 以集成高级驾驶辅助系统(ADAS)和信息娱乐系统(IVI)应用,已成为一项关键的趋势。

集中式架构催生下一代 SoC:集成、智能、高效

如图 1 所示,汽车行业正在从传统的分布式 ECU 和基于域的系统架构向集中式区域架构过渡。向新分区架构的转变将改变硬件系统和相关软件堆栈。在这一新架构中,中心是一个集中计算模块,负责处理多种功能,包括高级驾驶辅助系统(ADAS)、高度自动驾驶(HAD)、信息娱乐系统、底盘/车身控制和动力总成等。各种应用将在该模块内的多个独立硬件板上运行,这为多个独立硬件板集成和 SoC 提供了更多机会。

新的集中式 EE 架构正在创造新一代系统级芯片 (SoC),其集成度更高、性能更强、人工智能数量更多,可承载更多的组合应用。

图1 电气/电子 (EE) 系统架构的演变

在单个 SoC 中集成多个汽车应用的优势有很多。将 ADAS 和数字驾驶舱(IVI)功能相结合,需要同时执行 ADAS 应用(如自动紧急制动 (AEB)、自适应巡航控制和车道保持辅助系统 (LKA))和数字驾驶舱应用(如柱间高分辨率显示屏)。对此,汽车行业可能会采用多种不同的混合方法来集成应用。例如,远程信息处理功能可以与 ADAS 功能合并,或者不同应用可以集成到多个不同的混合平台中。这种整合可为硬件和软件供应商创造新的机遇。

采用集中式计算模块的分区架构将对承载合并应用的计算 SoC 产生影响。运行多个应用的新一代中央计算 SoC 需要更高水平的人工智能处理、更多的高速缓存一致性多核 64 位主处理器以及更高水平的显示处理。由于实现计算 SoC 的高性能和复杂性,需要先进的半导体 FinFET 工艺。将多种功能集成到中央计算 SoC 中将降低成本并最大限度地减少复杂性,从而使汽车制造商、一级和二级供应商实现差异化。

对中央计算SoC提出更高要求

中央计算 SoC 是未来汽车电子系统架构的关键组成部分。新一代汽车中央计算 SoC 将具有共同的标准,包括沿车载网络传输的大量传感器数据和使用最新人工智能算法的大量人工智能数据。

对安全至关重要的 ADAS 应用来说,大量的传感器数据必须得到持续的实时处理。来自雷达、激光雷达、超声波和摄像头等传感器的数据必须以最低的延迟持续到达。数据流量和协议不得超出车载网络线束的负荷。大多数车载网络使用汽车级以太网、用于图像传感器的直接连接 MIPI 链路和传统 CAN 网络的组合。由于通过汽车级以太网运行的雷达/激光雷达数据量巨大,因此需要使用 IEEE 以太网时间敏感网络 (TSN) 协议为以太网链路提供多个 10G 以太网数据流。通过使用以太网 TSN 协议,可根据网络策略传输高优先级的安全关键型数据包,以确保后座娱乐等低优先级数据不会干扰安全关键型应用。对于成像数据,每个高分辨率图像传感器可产生超过 10G 的实时未压缩数据,这将使传输雷达/激光雷达数据的以太网网络超载。因此,大多数成像数据都使用单独的 MIPI 接口传输。

为了在车内恶劣的信道条件下传输基于 MIPI 的成像数据,业界开发了几种专有协议。除了专有数据通道外,MIPI 联盟还开发了新的 15m 汽车 A-PHY 协议,用于将图像数据传输到中央计算模块。作为一种车载数据传输协议,MIPI A-PHY 正变得越来越流行。

新一代集中式计算 SoC 必须同时执行实时应用。由于多个实时应用同时运行,集中式计算模块中使用的处理 SoC 必须支持类似于高性能数据中心服务器处理器的虚拟化。由于 SoC 必须支持多个实时应用,因此需要针对基于 RISC-V 的新一代高性能汽车处理器对应用的 SW 栈进行优化。提前规划应用 SW 将使汽车制造商能够设计未来的软件定义汽车 (SDV),并引入新的特定应用商业模式。但是,对于以分区集中计算为目标的高性能 SoC,处理器必须包含专门的功能,以满足运行实时应用所需的性能。

集中式计算 SoC 的一个关键设计特点是可扩展的异构多核处理器,SoC 中最多可集成 12 个 64 位应用处理器。实现高效的软件首次开发是包括 SoC 供应商在内的汽车 SDV 供应商的主要目标。为了建立汽车级 RISC-V 处理器的单一来源,实现基于 RISC-V 的兼容产品并提供参考架构,博世、英飞凌、北欧半导体、恩智浦和高通等行业供应商成立了一家名为 Quintauris 的合资公司。Quintauris旨在通过推动汽车RISC-V部署的采用,实现下一代兼容SDV的硬件开发。

为了执行对安全至关重要的 ADAS 应用以及驾驶员监控系统 (DMS) 和乘员监控系统 (OMS) 等人工智能基础 IVI 应用所需的人工智能算法,SoC 需要额外的深度学习人工智能加速器。新增的生成式人工智能使 IVI 供应商能够提供自然语言数字助理,从而为中央计算模块带来额外的人工智能工作负载。原始设备制造商正在将人工智能用于 ADAS/HAD 的多种应用,如路径规划、物体/场景检测和识别以及基于人工智能的决策制定。前面提到的 ADAS/HAD 应用,如自动紧急制动、车道保持辅助和自适应巡航控制,都是基于人工智能的。

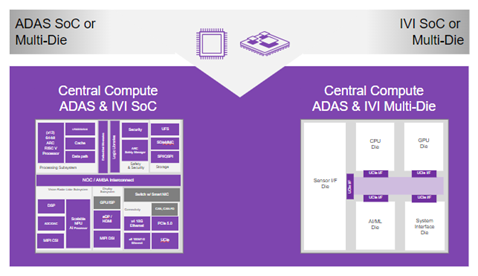

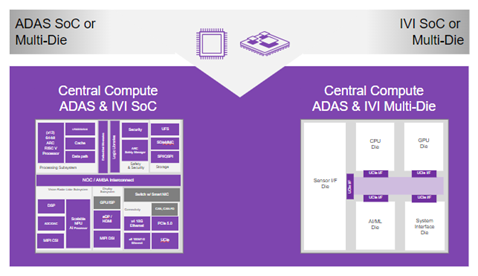

图2显示了用于合并ADAS和IVI应用程序的中央计算SoC的一般示例。左边显示的分立SoC包含多达12个64位应用处理器和一个基于AI的视觉子系统,用于基于相机的AI应用。除了所需的处理性能外,SoC还包含一个独立的ISO 26262功能安全管理器和一个独立的安全子系统,以最大限度地减少安全漏洞。包括汽车级以太网TSN在内的一套完整的连接接口提供了多个通道,将SoC连接到车内区域网络,以及附加的点对点协议(如MIPI)。中央计算SoC包含PCI Express (PCIe)接口,通过添加单独的SoC加速器来扩展SoC的处理性能,从而实现多SoC性能。PCI Express是连接多个SoC的主要外设协议,它添加了AI算法加速器以提高SoC性能。

图2 中央计算处理器 SoC

考虑到托管合并的 ADAS/IVI 应用所需的虚拟化应用处理、人工智能加速和 DSP 处理量,中央计算模块需要先进的半导体制造工艺来实现 SoC。为实现功能、集成和性能目标,需要先进的 FinFET 级半导体制造工艺,如汽车级 5 纳米工艺。行业领导者已经在规划采用汽车级 3 纳米代工工艺的战略,以实现 ADAS/IVI 合并计算 SoC。

右侧显示的是使用基于 UCIe 的多芯片解决方案的替代实施方案。使用 UCIe 链接的多芯片设计将各种异构芯片连接起来,为合并的 ADAS/IVI 中央计算模块提供了诸多优势。基于 UCIe 的多芯片设计能够为每个功能芯片选择最佳的技术节点和设计风格。混合搭配芯片的机会为产品管理提供了灵活性,并缩短了产品上市时间。由于 UCIe 协议是行业标准,因此可确保每个芯片接口都具有互操作性,并能以最小的风险取得成功。

总结

为了满足下一代汽车电子架构对高性能、安全性和低功耗的苛刻要求,开发者正致力于将ADAS和IVI应用融合到新的分区架构中,并采用汽车级IP进行集成。而业界领先的基于64位RISC-V的处理器和接口IP(如PCI Express、LPDDR、MIPI和以太网)为SoC设计提供了强大的支持。这些IP经过严格测试和验证,符合ISO 26262功能安全标准,并支持TSN功能,可满足下一代集中式EE架构对SoC计算的严格要求。

原文链接

1.Qualcomm and Bosch Showcase New Central Vehicle Computer for Digital Cockpit and Driver Assistance Functions at CES 2024, January, 2024

2.Christophe Marnat, EVP ZF Electronics/ADAS, May, 2021

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 2 TSN芯片,上车!

- 3 汽车芯片需求激增,南芯科技加速推进“第二增长曲线”

- 4 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来