RISC—V助力开源GPU发展

来源:内容

翻译自

tomshardware

,

谢谢。

开源GPU的时代可能会到来。众所周知,RISC-V架构使小型公司无需支付专利使用费即可开发专用的处理器和微控制器。基于RISC-V的片上系统(SoC),有许多免费和商业IP构建模块,但是产品组合缺少图形选项。随着一群发烧友开始开发基于RISC-V架构的开源GPU,这种情况将在几年后改变。

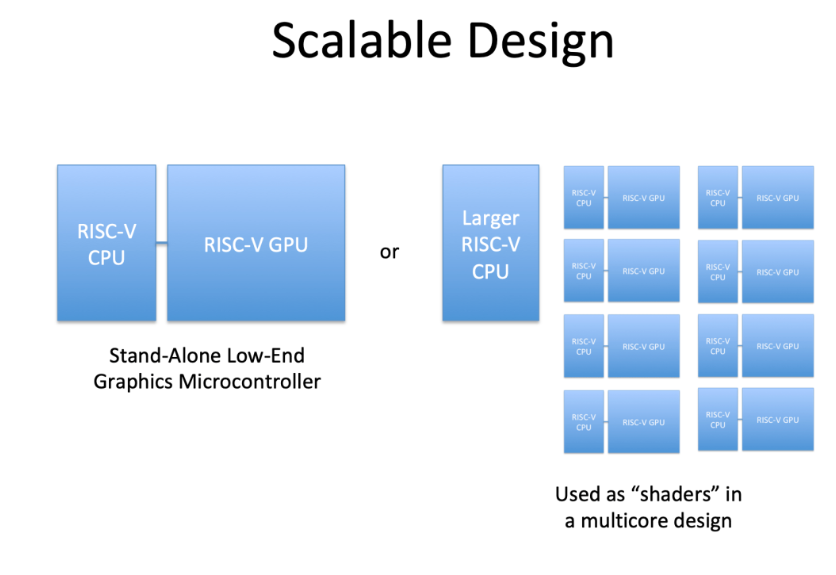

目前,还没有计划在可预见的未来与AMD、Arm、Imagination和Nvidia竞争。有消息显示,现在有一些团队正在计划开发一种可扩展的融合CPU-GPU ISA,它可以从简单的微控制器扩展到支持光线追踪、机器学习和计算机视觉应用的高级GPU,并可以通过定制来实现硬件扩展。

在较高级别,RV64X设计的GPU使用基本的RV32I或RV64I内核,这些内核支持基于基本向量指令集的新指令。Jon Peddie写道:最初,它将使用RV32I内核,但是最终,将由RV64I内核取代,因为其目标是创建具有自定义可编程性和可扩展性的可用于CPU,GPU和VPU的区域高效设计。

为了正确处理图形,基本的RISC-V内核将支持特定于新图形和机器学习的RV32X数据类型,包括标量(8、16、24和32位固定和浮点数,向量(RV32-V)和矩阵) (2x2、3x3和4x4);矢量/数学指令;像素/纹理指令;帧缓冲区指令;特殊寄存器集(具有可配置的136位矢量寄存器);以及一些图形专用指令。最初,图形核心将 支持Vulkan API,但该小组致力于使其兼容DirectX(着色器模型5)和OpenGL / ES。

RV64X小组表示,其图形处理器将以微代码实现标准图形流水线,但也将能够添加自定义光栅化器(样条,SubDiv表面,补丁)和自定义流水线阶段,以支持商用GPU设计不支持的功能。。

hardware luxx报告说,该小组提出了一种RV32X参考实现,该实现具有hardware texture单元、特殊功能单元、32KB L1缓存、8K uCode SRAM缓存和四个32位dsp / alu(可以处理FP32和INT32数据)。参考设计将很可能使用FPGA实现。

Jon Peddie Research总裁Jon Peddie认为,RV64X项目尚处于开发的初期阶段,至少需要几年时间才能最终确定规格并实现任何硬件实现。实际上,即使是规范也会根据利益相关者和社区的意见而更改,因此现在讨论性能或任何其他问题还为时过早。

该小组自称为RV64X,因为其计划是开发64位通用ISA,由Pixilica的Atif Zafar,GOWIN Semiconductor的Grant Jennings和CHIPS Alliance and Western Digital的Ted Marena领导。

最初,由于成本方面的考虑,RV64X设计的图形控制器将用于非常简单的微控制器,这些微控制器需要非常小的单元。但是随着设计的发展,从最初的实施开始,它的后代就可以满足更多苛刻的应用需求。

点击下方阅读原文,获取原文链接

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2571内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆| 设备 |射频|封测|美国|三星|华为|汽车芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 首次!芯联集成2024年度毛利率转正

- 3 摩尔斯微电子推出MM8108:全球体积最小、速度最快、功耗最低、传输距离最远的Wi-Fi芯片

- 4 收藏,半导体一些术语的中英文对照