[原创] 走向MCU的新型存储

2021-01-30

14:00:02

来源: 半导体行业观察

今天我们来聊下新兴的非易失性存储器(eNVM)的进展,在谈eNVM之前,就不得不先谈起嵌入式闪存(eFlash)。

现在几乎所有的MCU细分市场现在都使用eFlash解决方案。什么是嵌入式闪存?内置微控制器、SoC等元件的闪存一般为称为“嵌入式闪存”。它与独立式(Standalone)存储器的最大区别在于是否将CMOS 逻辑作为平台。

摩尔定律的趋势要求晶体管不断的向更小尺寸微缩,但嵌入式闪存的微缩化正在逼近极限。这主要是因为闪存的微缩化步伐赶不上CMOS 逻辑的微缩化。我们都知道,当下CMOS 逻辑量产的最先进技术节点为5纳米,而闪存微控制器的量产代际还停留在40纳米节点,加工尺寸的差距为8倍,技术代际的差距也至少有四代(假设代际区间为:7纳米时代、14纳米时代、28纳米时代)。

与普通的逻辑半导体相比,由于嵌入式闪存的存储单元采用具有特殊构造的晶体管,在读写方面需要较高的电压,理论上来讲不易实现微缩化。此外,22纳米世代以后CMOS 逻辑的晶体管全部立体化,为FinFET。用于嵌入式闪存的晶体管的研发技术极其困难。

于是,人们正在积极研发能够替换嵌入式闪存的非易失性存储技术(eNVM技术),包括相变存储器(PCM),自旋转移转矩随机存取存储器(STT-RAM)、电阻式随机存取存储器(RRAM),以及英特尔的Optane等等。嵌入式非易失性存储半导体(eNVM)技术的优势主要有两点:首先,在生产多层线路时就将存储元件埋入,不受晶体管技术的限制。其次,与闪存相比,读写所需电压较低。因此,就28纳米以后的技术世代而言,eNVM技术有望代替eFlash技术。

eNVM技术的最有力后补技术为STT-MRAM技术。而几大晶圆厂也在积极拥抱eMRAM技术。在ISSCC 2020上,台积电介绍了其32Mb MRAM的进展;2020年3月,晶圆大厂格芯宣布,其22nmFD-SOI 平台的嵌入式eMRAM已投入生产;2019年3月,三星推出首款商用eMRAM产品;英特尔也发布过关于MRAM研究的新论文。

按说STT-MRAM技术应是各大MCU厂商的头道菜,因为eMRAM比eFlash更快,更省电。不同于eFlash是一种前端技术,eMRAM的磁性存储元件搭建于后端金属层上,这就利于将其集成逻辑制程,FD-SOI不会对前端晶体管造成影响。但是,事情的发展却不是如此!ePCM技术却率先登上MCU舞台。

根据pc.watch的报道,令人意外的是,在28纳米世代以后的生产技术中,微控制器厂家率先发布的eNVM技术并不是STT-MRAM,而是ePCM(ePCM,Phase Change Memory)。微控制器厂家巨头意法半导体在2018年12月发布称,研发了一项车载嵌入式相变化存储半导体,可代替28纳米逻辑。

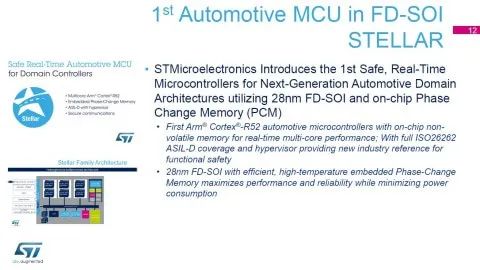

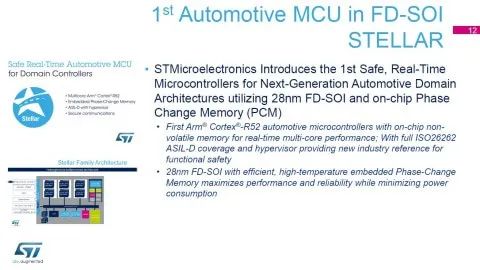

后来在2019年2月,意法半导体又宣称,开始量产28纳米世代的32bit微控制—-“Stellar”系列。“Stellar”系列不采用嵌入式闪存,作为42MB的微控制器,可内置容量极大的嵌入式PCM。首代产品内置了16MB的大容量PCM,内置了6核Arm Cortex-R52(最大作业周波数400MHz)、8MB的RAM。工作温度范围:-40℃~+165℃,满足车载信赖性要求“0”(Auto Grade 0)。工艺技术采用28纳米世代的FD-SOI CMOS技术。

车载32bit微控制器“Stellar”系列的概要。(图片出自:意法半导体公示资料。)

通过pc.watch的报道我们发现,ePCM技术的优势在于存储元件的结构较简单。仅包含上下电极、且层数在五层以下。然而,STT-MRAM技术下的存储元件结构复杂、层数至少在10层左右。以上这种差异会直接影响产量。

此外,从外部施加磁性(用途为电机控制方向)时,ePCM技术不需要防护罩(Shield)。STT-MRAM技术下,仅靠硅片的话,抗磁性较弱。在电机控制方面,有些使用场景下会需要使用磁性防护层的封装模式。这会增加封装的成本。

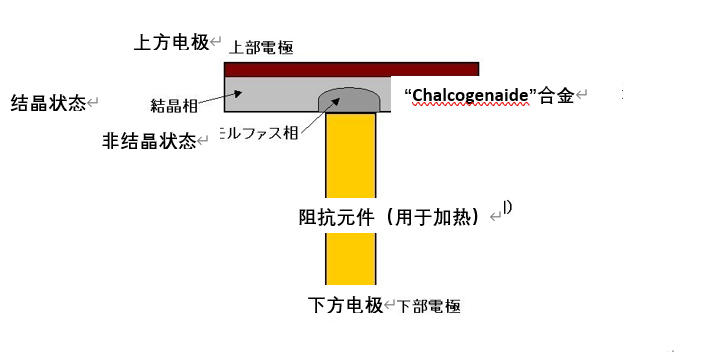

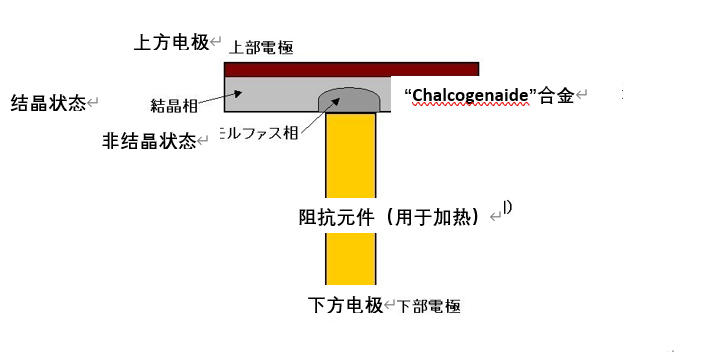

一直以来人们普遍认为PCM技术不适用于车载半导体。PCM是利用被称为“Chalcogenaide”的化合物(合金)在结晶状态和非结晶状态(Amorphous)时巨大的导电性差异来存储数据的。

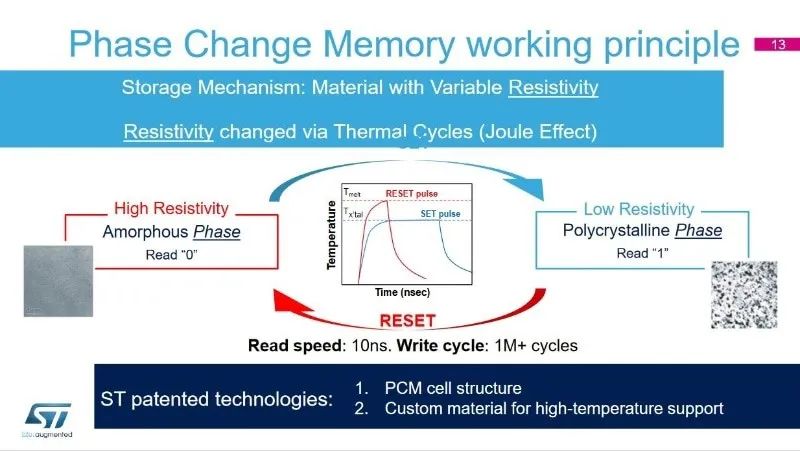

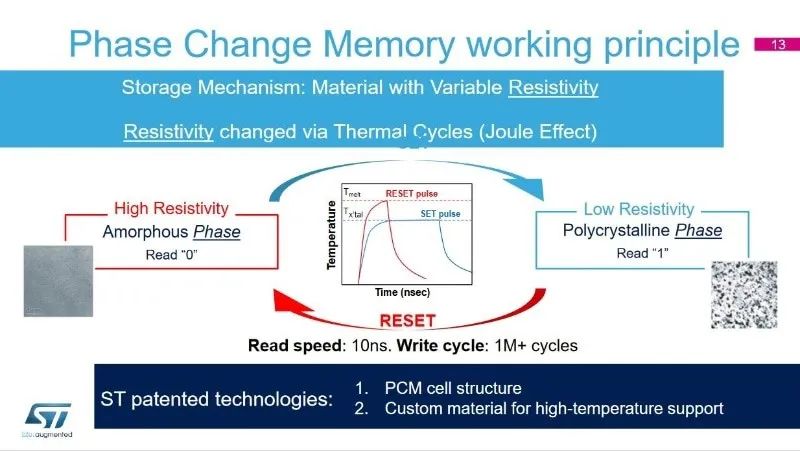

通过控制加热和冷却来改变化合物的状态变化。转为非结晶状态(数字“0”)的动作被称为“重启(Reset)”。在“重启(Reset)”动作下,在极短的时间内对“Chalcogenaide”合金进行迅速高温加热、并在极短的时间内迅速使其冷却。转为结晶状态(数字“1”)的动作被称为“启动(Set)”。在“启动(Set)”动作下,对“Chalcogenaide”合金以稍长的时间、较低的温度进行加热,且以稍长的时间慢慢使其冷却(此处的时间和温度是相对于“重启”的)。

相变化存储半导体(PCM)的存储结构(概念图)。“Chalcogenaide”化合物的薄膜与加热器的金属膜通过上下电极连接。“Chalcogenaide”合金在结晶状态下电阻低、在非结晶状态下的电阻较高。(图片出自:pc.watch)

相变化存储半导体(PCM)的存储原理。通过控制加热&冷却的温度和时间,反复循环非结晶状态(左侧)和结晶状态(右侧)。(图片出自:意法半导体公开资料。)

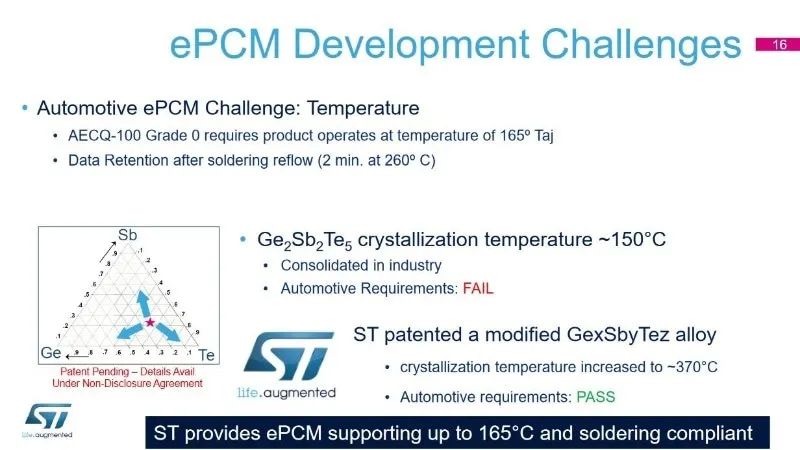

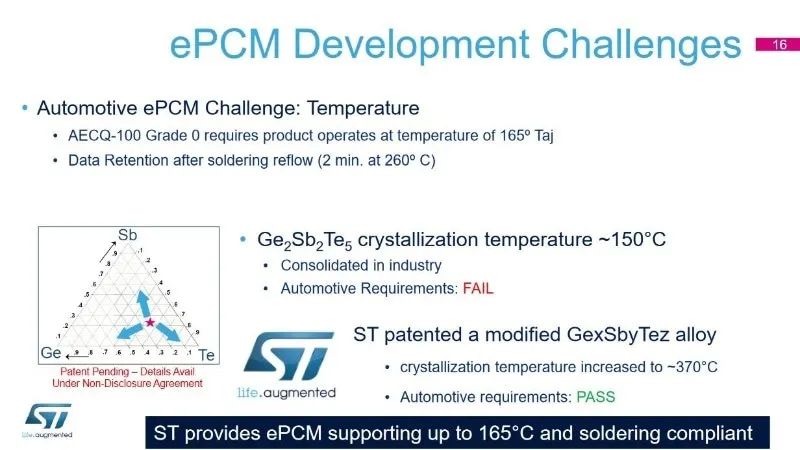

标准情况下,PCM中采用的“Chalcogenaide”化合物为Ge2Sb2Te5,且Ge(锗)、sb(锑)、Te(碲)以2:2:5的比例混合。多被表示为“GST-225”、“GST225”。“GST-225”的相变化需要的时间极短,为数十ns(纳秒),相变化次数为100万甚至更多。

GST-225的结晶温度较低,为150度,那么采用了GST-225的PCM的使用温度上限则为+100度左右。因此,可用于消费类电子(因为其温度的使用上限为+70度或85度),但是,很难应用于上限温度为+105度的工业领域。更无法应用于上限温度为+125度、+150度的车载方面。以上是关于PCM的常识。

超耐热PCM材料的发明颠覆了PCM的以上常识。意法半导体研发了一款结晶温度更高的GST材料,此款材料具有较高的Ge(与GST-225相比)含量,并应用到了嵌入式PCM(意法半导体内部称之为“Ge Rich GST”或者“T合金”)。“Ge Rich GST”的结晶温度高达+370度。运用此次研发成果,使满足车规半导体信赖性级别“0”(Auto Grade 0)的PCM内置微微控制器的量产得以实现。

满足车载半导体信赖性级别“0”的嵌入式PCM材料(e PCM)的概要。(图片出自:意法半导体公示资料。)

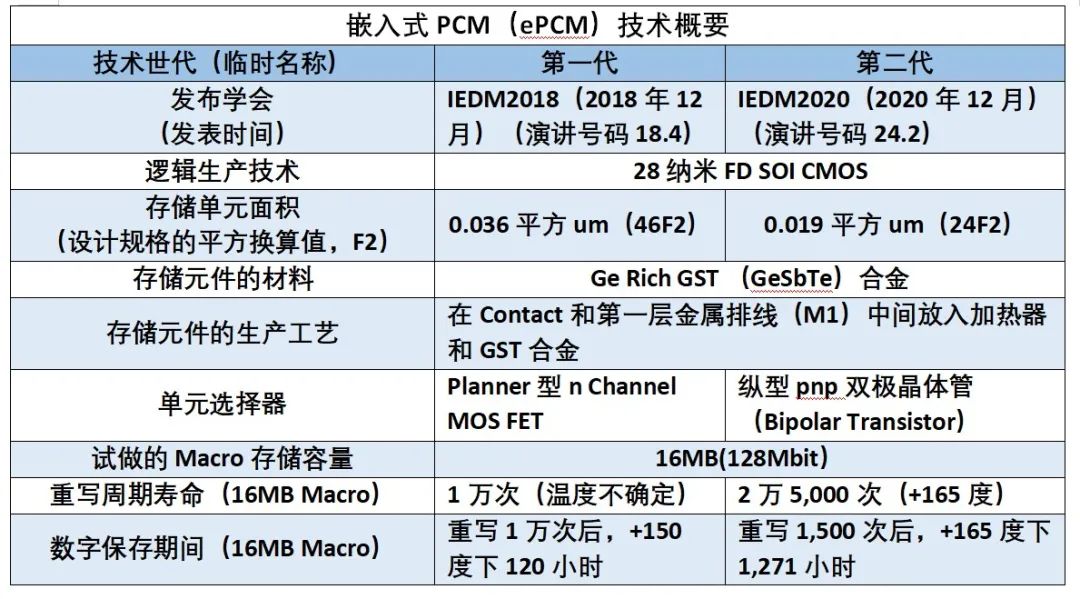

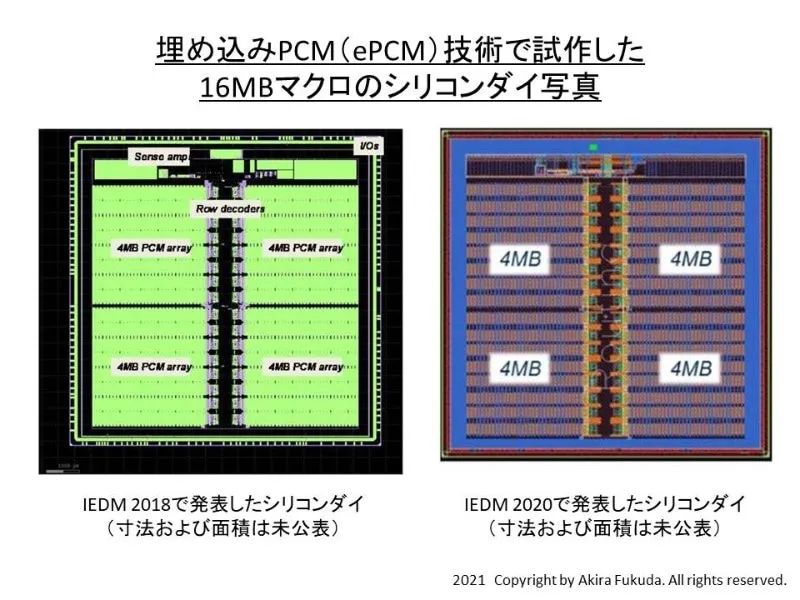

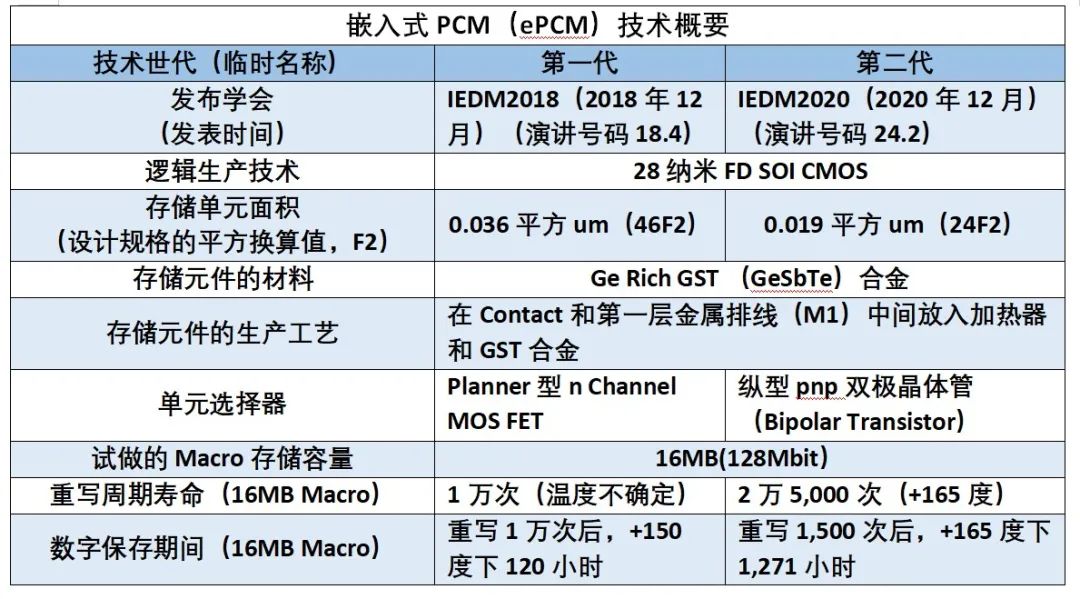

此外,意法半导体还在2020年12月召开的国际学会---IEDM 2020上公布了将存储单元格面积减半的嵌入式PCM技术(ePCM)。意法半导体在2018年12月召开的IEDM 2018上公布的第一代ePCM技术,其存储单元格的面积是0.037²um。

在2020年12月的IEDM上发布的ePCM技术(姑且称之为“第二代”)的存储单元格面积极小,为0.019²um。在以往的国际学会、学会论文中公布的所有嵌入式非易失性存储半导体中(包含嵌入式闪存),0.019²um是面积最小的。二代存储单元格的面积仅为第一代的53%。CMOS 逻辑虽然也采用了同样的生产技术(28纳米世代的FC SOI CMOS 工艺),但ePCM技术下的存储单元格面积减小了几乎一半。

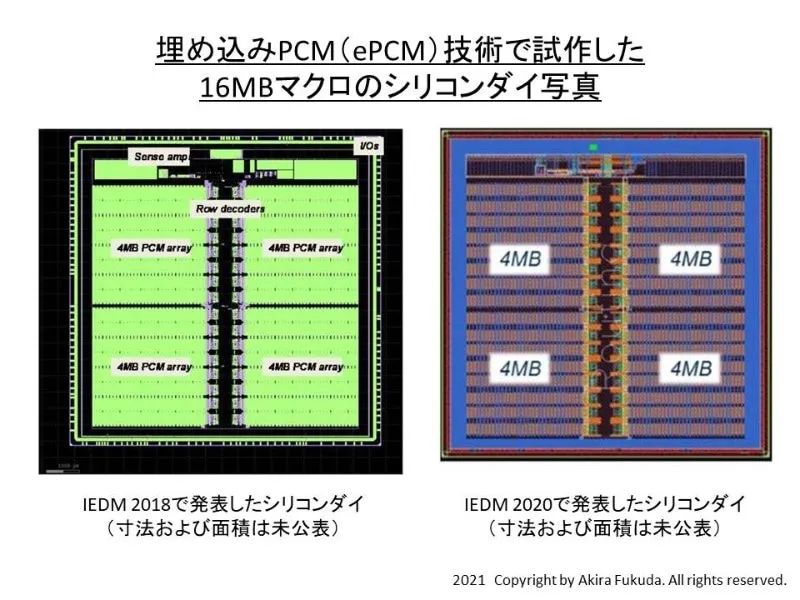

上图是存储容量达16MB(128Mbit)的嵌入式PCM micro硅片图片。左侧是IEDM 2018上发布的第一代产品、右侧是IEDM 2020上发布的第二代产品。二者都出自IEDM论文。但是,左右两图的缩小比例不一致。

第一代和第二代的最大区别在于单元选择器和选择器的分离。第一代的选择器为n 型channel MOS FET。由于是FD SOI,因此即使施加Back Body Bias,存储单元选择器还是标准的。

在第二代中,由于存储单元选择器较小,因此单元选择器为纵型pnp 双极晶体管(Bipolar Transistor)。FD SOI的p阱(Well)为集电极(Colletcor)、n阱为基极(Base)、p型扩散层为发射极(Emitter)。为了能够与CMOS Logic进行工艺互换,留下了与n Channel MOS同样的虚拟栅极(Dummy Gate)。

此外,采用极其浅的沟槽(被称为SSTI,Super-Shallow Trench Isolation)来分离位线(BitLine)间的元件,因此缩短了位线间的距离。每4根位线汇集在一起,且通过SSTI与其他位线相分离。就字线的元件分离而言,与之前一样,采用STI(Shallow Trench Isolation)。通过以上努力,大幅度缩短了存储单元的面积。

意法半导体研发的嵌入式PCM(ePCM)技术比较。(表格出自:笔者根据IEDM上发布的论文、演讲内容制作了此表。)

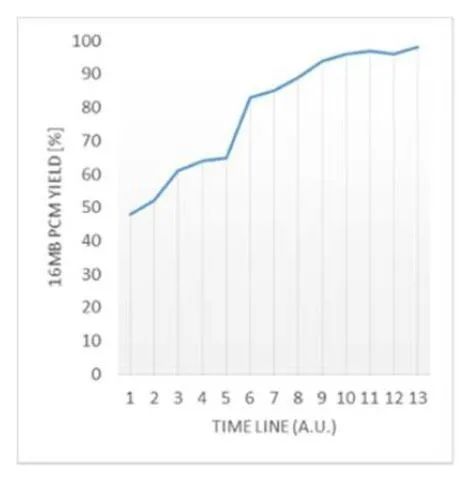

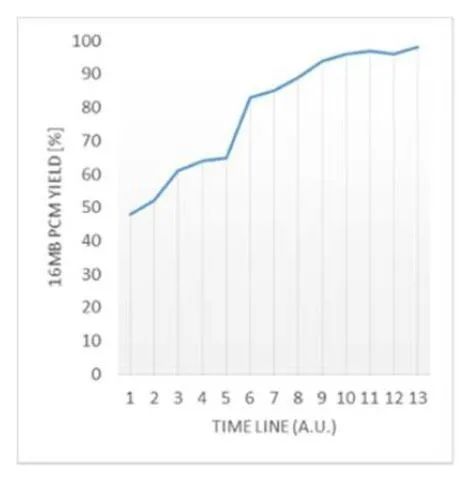

在IEDM 2020上,有论文和演讲中提到了16MB Macro的生产良率随时间的变化情况,良率已经几乎接近100%。即,在ePCM的生产中,在CMOS 逻辑上追加的薄膜仅有两片。

运用第二代ePCM技术生产的16MBMacro的良率推移表,可以看出良率几乎接近100%。(图片出自:IEDM 2020发布论文。)

虽然ePCM技术确实取得了一定的进展,包括在材料以及面积上等等,但是,要将ePCM技术推广到半导体市场上,还有一些不确定因素。意法半导体尽管在从事着28纳米世代的FD SOI CMOS逻辑的代工业务,但不确定其是否会提供ePCM技术。

另一方面,如上文所提到的,由于已经有多家经验丰富的Foundry企业同时提供28纳米世代和22纳米世代的逻辑半导体,因此从微控制器厂家、半导体控制器厂家的立场来看,嵌入式STT-MRAM技术使用起来更容易些。

所以,目前,尚不清楚哪种存储技术将成为这场战斗的赢家,因为一项技术的推动需要芯片制造商、技术许可方、晶圆代工厂,工具和设备制造商等多个产业链的支持才行。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2570内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|设备

|射频|封测|美国|三星|华为|汽车芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie