来源:内容由半导体行业观察(ID:icbank)编译自「

thenextplatform

」,谢谢。

除了负责芯片蚀刻工艺开发的人和实施该工艺的代工厂之外,英特尔面能力的最困难工作是什么?我们认为是该公司正在运营的分散的网络业务。这是一个竞争非常激烈的市场,且竞争将愈演愈烈。因为现有的和新贵的公司在网络接口卡,交换,硅光子学和其他领域都与英特尔展开激烈竞争。

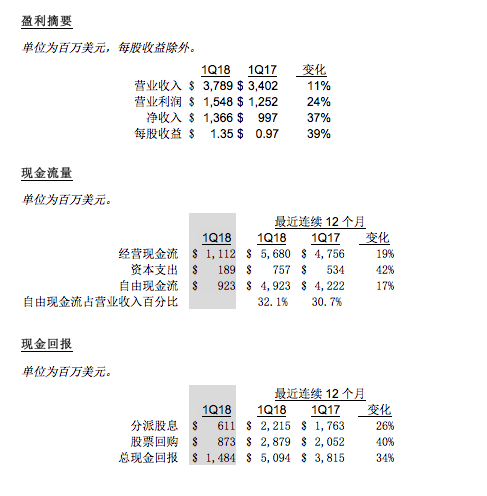

Hong Hou是英特尔连接部门的新任总经理,该部门是数据中心部门的子部分之一,在过去的十二个月中,DCG部门的收入达到277.1亿美元,占公司收入的三分之一以上,在利润方面更是贡献了公司的一半以上的整体利润。

我们不知道这个数据中心集团业务中究竟有多少种形式的联网,但是我们怀疑它在一定程度上反映了整个行业,然后偏向于右侧,向计算转移,远离联网和存储。很难猜测网络业务的总收入是多少,因为我们没有足够的数据,而这取决于您如何削减数据。Intel的网络接口卡业务可与Nvidia的Mellanox部门相媲美,而交换机业务如果将Barefoot和Omni-Path包括在内,则可能与Mellanox相当。硅光子学尚未带来很多收入,但用于网络电缆的收发器可能会带来很多收入。

没有简单的方法可以量化在Xeon iron上运行多少软件定义的网络软件,从技术上讲,这应该算作Connectivity Group的收入,或者由其Data Plane Development Kit和其他系统软件支持多少网络,或其(以前是Altera)FPGA的销售量中有多少用于网络用例。但是英特尔正在尝试基于各种SDK,操作系统和抽象层以及运行在其各种网络硬件上的控制平面来构建网络软件堆栈。

可以这么说,尽管面临挑战,且英特尔并不是互连网的领导者,但它还是互连领域的一个重要参与者。无论如何,就创新的步伐和创新成本而言,这种优势通常无法很好地为市场服务。因此,这也不是理想的状态。但是,毫无疑问的是,我们必须让Intel参与网络业务,并把对数据中心的了解带给我。

Hou担任一个正在经历巨大变化的连通性小组。英特尔在2011年和2012年打造了一个HPC类型网络的军火库,当中包括QLogic的InfiniBand的业务和Cray“Gemini” XT和“Aries” XC互连,其谋求合并成一个超级互联称为Omni-Path,但它刚刚剥离出来成立了Cornelis Networks,初始团队包括了一些以前的Intel和QLogic员工。

与许多使用惠普公司的Cray 200 Gb /秒Slingshot HPC和其余使用200 Gb / sec HDR Quantum InfiniBand的公司一样,英特尔让Omni-Path进入历史记录也就不足为奇了。更令人惊讶的是,Cornelis Networks希望采用InfiniBand和Aries互连的思想,并朝着自己的方向发展。

2019年6月,该公司收购了Barefoot Networks以购买其可编程以太网交换机ASIC,并获得了对交换机的P4编程语言的更多控制权,从而使其与英特尔内部的Omni-Path紧密相连。英特尔对用于超大规模生产者和云构建者的可编程以太网交换和SmartNIC(越来越多地称为DPU)更感兴趣,随着技术的飞速发展,最终将被其他服务提供商和大型企业模仿。

现实是这样:公司将大量使用计算,我们通常指的是CPU,但越来越多的GPU和少量的FPGA已经被采用,而不是内存或网络,因为他们对前者更了解。这是另一个不能讨价还价的事实:数据中心网络中传送的数据量以每年25%的速度增长。但是预算不能以这种速度增长,而且由于对原始CPU计算的偏见投资(与构建平衡的系统以更充分地利用可用的计算能力相反),网络通常不超过分布式成本的10%系统,当它的确上升到15%左右时,就会有很多哭泣和咬牙切齿的感觉。

面对所有这些压力,英特尔必须创新并帮助改善网络。Hou说,集成将成为这些关键之一。

“对于英特尔,我们希望在一个灵活的网络中提供智能和可编程性,以应对新兴工作负载的复杂性,”Hou告诉The Next Platform。“我们的愿景是优化所有这些技术资产,以便为我们的客户提供支持的解决方案,我们不仅仅是一袋零件的供应商。在未来,以太网将从端点连接发展而来,而SmartNIC也将扮演重要角色,它们将承担一些关键工作负载并加速某些工作负载并为网络提供更强的性嗯那个。该SmartNIC将与CPU,GPU,FPGA集成在一起进行计算,并且可能还会有存储设备。我们看到了明显的趋势,我们正在共同努力发展。

稍后,我们将讨论基于FPGA的新产品版本。早在3月,我们宣布了将光学元件与开关一起封装,并且收到的好评。下一步将使用光学I / O技术提供更多的带宽密度。die到die的电气互连可能会走向极限,并且可能无法提供所需数据量的连接性。因此,我们需要光学I / O来支持数据流通。”

在某种程度上,硬件是最简单的部分。尽管互连行业近年来有所发展。回到十年前,当时出现了一些信号障碍,导致创新速度显着下降,而现在,我们可以预期每18至24个月就会出现交换ASIC和匹配的网络接口ASIC的节奏。Hong说,但是,数据中心内部的网络运营商希望创新的速度更快,并且他们希望在软件和硬件方面进行创新,因为他们已经能够在数据中心堆栈的计算部分中进行数十年了。因此,可编程性(以及P4)与您可以将多少个晶体管塞入开关或网络接口ASIC以及对其进行处理一样重要。

当谈到“ Tofino”系列的Barefoot 开关ASIC时,Hou表示,客户希望Intel能保持两年更新芯片的节奏。6.4 Tb / sec 的Tofino 1芯片于2016年6月Barefoot退出隐形市场时开始送样,随着2018年即将结束,他们推出了12.8 Tb / sec 的Tofino 2芯片,该设计采用小芯片设计打破了数据包中的SerDes处理引擎,并使用25 Gb /秒的本机信令和PAM-4编码来使每通道有效50 Gb /秒。最终的交换机可以以400 Gb /秒的速度驱动32个端口,或者降低速度并按比例增加端口数。

两年的节奏可能会有所延迟,这是由于英特尔的收购以及尚未做出的决定,即以25.6 Tb / sec的Tofino 3代(即32个端口)与Tofino ASIC进行光学封装的共同决定。速度为800 Gb /秒)或51.2 Tb /秒的Tofino 4代(32个端口,惊人的1.6 Tb /秒)。要达到这些速度,将需要112 Gb /秒的本地原始信号传输,再加上更密集的PAM编码或更多的端口通道,我们将很快看到结果,Hou也很有信心。他表示,英特尔可以在将来的某个时候将102.4 Tb / sec的Tofino 5投入生产。如果执行两年鞥新的节奏,则Tofino 2现在将在2021年开始提供样品,Tofino 3将在2022年开始提供2023年产品,Tofino 4将在2024年开始提供2025年产品,Tofino 5将在2025年提供产品。2026年有2027年的产品。伙计们,请发挥您的思维能力。

同时,除了新闻稿外,Hou在我们聊天时都没有提到,“他们是否将开源Tofino架构,以确保可编程分组处理器与CPU一样开放。”

首先,开源是什么?交换机ASIC中的指令集的实际芯片设计是什么?其次,“像CPU一样开放?” 英特尔的处理器都不是开放源代码,也不是AMD的处理器,基于Arm的技术只是可授权和可适应的。IBM也基于其用于网络处理器和BlueGene / Q超级计算机的PowerPC-A2架构开源了Power ISA和两个Power内核A2I和A2O。Sun Microsystems很早以前就开源了“ Niagara” T1多线程CPU。我们将尝试弄清楚英特尔在说什么。

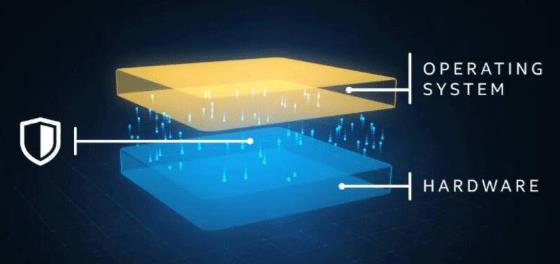

所有这些都以一种绕行的方式将我们带到SmartNIC或DPU,无论您想称呼它们如何。让我们先讲一下哲学。如果您实际上是在蚀刻一种新型的芯片,而该芯片实际上以与交换机或路由器ASIC或CPU或GPU不同的方式进行数据处理和处理,则DPU才是一个好名词。(FPGA可以假装为任何东西,因此您不能真正排除或包含该设备。)

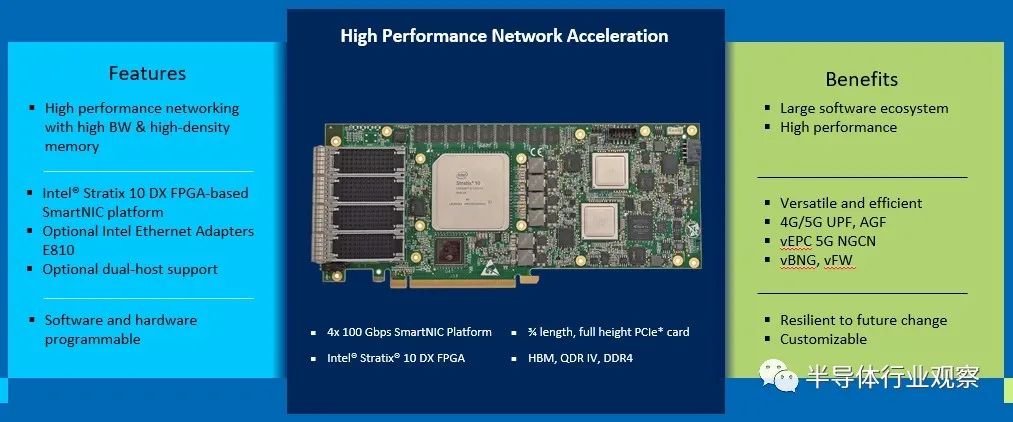

Fungible似乎正在创建一个真正的DPU,而Pensando似乎在做同样的事情。英特尔和Nvidia等公司正在创建将各种要素结合在一起的SmartNIC。对于Nvidia,它将Arm CPU与ConnectX网络接口芯片和Ampere GPU相结合。对于Intel而言,Hou向我们提供了预览版的最新SmartNIC,将CPU和FPGA结合在一起,并且在一种情况下,除非是拼写错误,否则可以将Tofino交换ASIC以及Intel 800系列网络接口芯片集成到复合计算中。复杂的人可以在最广泛的意义上称呼DPU。这是我们认为行业会做的,因为DPU听起来比SmartNIC更智能,更酷,更有价值。

这些新的FPGA通常针对云和通信服务提供商,我们在The Next Platform中将其分为三个部分:hyperscalers,云构建者以及其他电信和服务提供商,它们虽然规模不大,但是也不像制造,分销等传统企业。

有趣的是,新的Intel SmartNIC实际上不是由Intel制造的,而是由Inventec和Silicom制造的,前者对于hyperscalers和云构建者来说是日益重要的ODM,而后者则是过去二十年来的网络接口供应商。这些器件与纯FPGA加速卡(称为可编程加速卡)一起在节奏上,我们在2017年10月首次在Arria 10 FPGA上首次亮相以及2018年9月用Stratix 10 FPGA对其进行更新时就谈到了这些器件。这是英特尔认为的FPGA加速连续体:

用于云的SmartNIC C5020X类似于为Facebook制造的产品,每当您看到Xeon D时,都应该考虑Facebook,因为该芯片基本上是为社交网络设计并保持有效的,因此应将其称为Xeon F真的。话虽如此,微软也对这种特别的SmartNIC表示了祝福,因此也许他们俩都将使用它。

这是Inventec的SmartNIC C5020X的功能:

Stratix 10 DX 1100是该系列器件中的低端FPGA,在定点工作中具有超过130万个逻辑单元,数量级为10.4 TMACS(万亿次累加秒),而在64位浮点运算为4.1 teraflops。这不到更高级的DX 2800 FPGA的一半。Xeon D-1612具有四个以1.5 GHz为基数和2.5 GHz涡轮速度运行的内核。同样,这与英特尔拥有的最强大的至强D芯片相去甚远。

有趣的是Stratix 10具有两个8 GB的DRAM存储器块供其使用,并具有两个50 Gb /秒的以太网端口,并且FPGA和服务器通过PCI-Express 3.0的8条通道相互链接,这主要是因为Xeon D不支持PCI-Express 4.0。

Xeon D仅具有一个内存通道,而英业达则将16 GB存入其中。Xeon D的主板上焊接有一个32 GB的SSD闪存块。最后,整个复合系统使用8通道的PCI-Express 4.0链接到服务器,当前Intel处理器不支持,但Ice Lake可以支持即将在短期内交付,并于明年年初全面推出。

具有讽刺意味的是,该卡现在可以插入使用IBM的“ Nimbus” Power9或AMD的“ Rome Epyc 7002处理器”的计算机中。

有人指出,Silicom SmartNIC N5010上面装有Tofino的Switch ASIC,它在顶部的概览图中显示,但在我们看到的示意图中肯定没有。但是,如果人们放弃Open vSwitch软交换机,而在将来的SmartNIC或DPU中放弃实际的ASIC的实际小型实现,从而摆脱软件的缓慢速度,确实会非常有趣。只要baby Switch是可编程的,意味着可以在硬件上放置新协议-这是硬件和软件之间的良好区分,并且与FPGA相比,它更倾向于软件。

这是Silicom N5010 SmartNIC的功能:

框图显示,这两个由Intel ASIC驱动的以太网E810 NIC端口是可选的,每个端口以100 Gb / sec的速度运行,并且与Stratix 10 FPGA的PCI-Express 4.0通道无关。FPGA还驱动四个自己的100 Gb / sec端口,显然所有这些端口都将是相当大的I / O负载。该卡使用具有16条通道的双倍宽度但仅一个插槽的PCI-Express 4.0插槽连接回主机系统。

还有另一个PCI-Express 4.0 x16连接器,也许在这里连接了一个Switch ASIC,但这似乎不太可能。FPGA具有一个x16端口,可连接到144 MB的QDR SRAM存储器,32 GB的DDR4存储器和8 GB的HBM2堆叠存储器。那是很多内存,不包括FPGA模块固有的内存。

没有关于这两个SmartNIC的价格或总体可用性的消息。

最后一个想法:我们与十年前英特尔所倡导的网络负载模型相距千里之外,这将使越来越多的这项工作投入到CPU上。世界不同意,英特尔做出了反应。因此,offload 所有!

★ 点击文末

【阅读原文】

,可查看本文原链接。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2467期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

存储|晶圆

|

SiC|AMD|射频|台积电|美国|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!