来源:内容

由半导体行业观察(ID:icbank)

编译自「

tomshardware

」,谢谢。

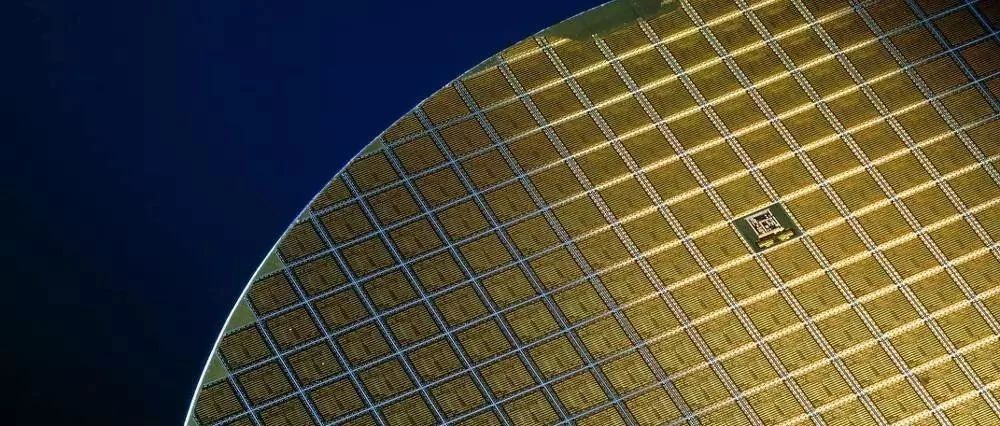

毫不奇怪,每一种新的制造技术的出现,都会让晶圆变得越来越昂贵,因为节点往往需要更多的资金。台积电最新的N5(5nm)制造工艺在每片晶圆上显得特别昂贵,因为它是新晶圆,但其晶体管密度使其特别适合具有高晶体管数量的芯片。

著名的半导体博客作者RetiredEngineer发布了一张表格,其中列出了台积电在2020年每个节点的假想芯片销售价格。。

该模型基于假想的5nm芯片,该芯片大小为Nvidia P100 GPU(610 平方毫米,907亿个晶体管,强度为148.2 MTr / mm2)。就每个图案化的300毫米晶圆的晶圆代工销售价格而言,该模型考虑了诸如CapEx,能耗,折旧,组装,测试和封装成本,晶圆代工营业利润率以及其他一些因素。同时,每个芯片的代工厂销售价格还包括设计成本,但是这个数字因公司而异,并且因节点而异(即,不同公司的610平方毫米的 5nm设计成本不同,并且610平方毫米芯片的实现方式也有所不同)由于设计规则和IP的不同,每个节点之间也是如此),因此应谨慎对待。

据估计,台积电使用N5技术处理的300mm晶圆售价约为16,988美元。相比之下,这家全球最大的半导体合同制造商对使用其N7节点图案化的300mm晶圆的价格约为9,346美元,对于使用16nm或12nm技术制造的300mm晶圆的价格为3,984美元。

有许多因素使台积电的N5节点如今使用起来如此昂贵。首先,台积电在几个月前开始生产5nm芯片,其晶圆厂及其使用的设备尚未贬值;其次,N5在很大程度上依赖于极紫外光刻技术的使用,并且最多可以在14层上使用。根据ASML的说法,每月每个大约45,000个晶圆的开始,一个EUV层就需要一个Twinscan NXE步进扫描系统。据信,每个EUV光刻机的成本约为1.2亿美元,而且这些扫描仪的运行成本也相当高。鉴于台积电的规模,其N5技术需要大量此类光刻机。因此,台积电要折旧N5所用的晶圆厂和设备将花费一些时间。

但是,即使按当前成本计算,由于其高晶体管密度和性能,对于高度复杂的芯片制造商来说,使用台积电的领先工艺也很有意义。根据提供的数字,使用N5制造610平方毫米芯片的成本为238美元,而使用N7生产相同芯片的成本为233美元。在16 / 12nm节点上,同一处理器将大得多,制造成本为331美元。与N7相比,在N5时,芯片不仅会相对较小(更精确地说为610平方毫米),而且在给定功率下运行速度也会快15%,在给定频率下功耗也会减少30%。

台积电(TSMC)表示,其N5的寿命同时具有比N7更低的缺陷密度,因此芯片设计人员可以预期,最终基于N5的芯片的产量通常会高于基于N7的IC。考虑到N5用EUV单图案替代DUV多图案的事实,后者是值得期待的。

在节点之间进行这种比较时要记住的一件事是,尽管它是基于台积电和整个半导体行业的数据,但台湾巨头从未确认过实际数字,因此它们可能不是100 %准确。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2436期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|设备

|

SiC|封装|射频|台积电|华为|EDA

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!