电力电子设备是将电力转换成不同形式的固态电子设备,并用于大量的日常应用中,从计算机到电池充电器,从空调到混合动力电动汽车,甚至是卫星。对越来越高效和更小功率电子设备的需求不断增长,意味着这些设备的功率密度(每单位体积的转换功率)已大大增加。随着电子功率器件的功率密度不断提高,传统的散热方法已经不能满足系统的需求。微流体冷却散热系统具有降低电子设备温度的巨大潜力,因为热量可以高效地传递到这些系统。

对于目前先进的液态冷却散热系统,主要有三种微流体冷却设计方案。第一种是通过液态冷却系统对芯片外围的金属保护外壳(Lid)进行散热。热量从芯片内部通过金属外壳,然后传递到嵌入有微流体通道的冷却板。对于这种技术方案,该封装结构主要包含两层热界面材料(TIM):一个在金属Lid和冷却板之间;另一个在金属Lid和半导体芯片的器件之间。

在第二种设计中,芯片没有外面的金属保护外壳Lid,因此热量会直接通过芯片的背面, 以及单个TIM层传递到微流体冷却板。但是,这两种方法的主要缺点是需要TIM层。尽管现在很多研究人员都在探索高热导率的热界面材料TIM,目前的TIM层由于其在半导体芯片与金属Lid,冷却板和lid之间的界面处仍会产生较高的热阻,因此成为该两种散热方案的主要散热瓶颈。

解决此问题的有效方法是使冷却剂直接与芯片背面接触“直接冷却”,这是第三种散热设计方案。例如,基于芯片背面的冲击射流冷却技术通过将液态冷却剂从微通道中的亚微米级喷嘴阵列直接喷洒到芯片的背面。这种方法由于没有使用TIM层,因此其冷却效率非常高,并且在芯片的制造过程中不需要对芯片的工艺进行任何更改。然而,这种微流体散热装置的制造及组装过程相对复杂,从而增加了工艺成本。研究人员已经通过3D打印技术开发了基于高分子聚合物的低成本冲击射流冷却装置,但是这种聚合物的制作工艺与现有的电子设备制造和组装工艺不兼容。

“直接冷却”的另一种方法是芯片背面的嵌入式微流体冷却沟道散热,该方案是通过在半导体芯片背面刻蚀出微米级/亚微米级的平行微流体沟道(SPMC),然后将冷却液体直接泵入到微流体沟道里面。这种方案通过将微流体冷却通道集成到芯片中,从而有效地将芯片的背面变成了散热器,使液态冷却剂和芯片发热源之间的距离大大缩小,已经成为提高电子系统性能非常有潜力的散热方法。

但是,与其他散热方案相比,该冷却装置需要很多额外的芯片加工工艺,例如背面光刻,刻蚀和键合。并且,SPMC的主要缺点是,冷却通道上的压降会随着沟道的长度的增加而急剧升高。微小宽度的微流体沟道可以提高芯片的散热面积,然而冷却器的压降却随之增加,这意味着需要大功率泵,从而增加了能耗和成本,并在半导体器件上产生潜在的破坏性机械应力。SPMC的另一个主要缺点是芯片上会产生高的温度梯度,这会引起热机械应力并导致薄芯片的局部翘曲。

与SPMC相比,被称为“嵌入式歧管微通道”(EMMC)的三维冷却系统在降低泵输送功率和芯片温度梯度方面具有巨大的潜力。在嵌入式歧管微通道系统中,这种3D分层歧管(一个具有多个用于分配冷却剂的端口的通道部件)为嵌入式微通道提供了多个入口和出口,从而将冷却剂传输路径分成多个平行部分。然而,目前最先进的多歧管微流体冷却系统主要是将微流体沟道和多歧管分流系统分开进行设计和制造,然后通过键合工艺来完成。这种集成键合方式极大地增加了制造芯片的复杂性,并潜在地增加了制造成本。

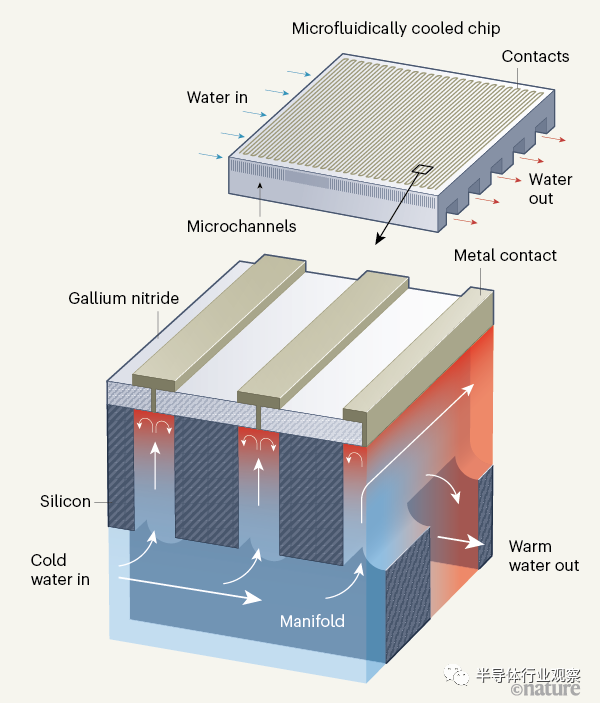

Elison Matioli 带领的研究团队开发了单片集成歧管微通道(mMMC)系统,该技术已经取得了突破。在该系统中,嵌入式3D歧管微通道可以在单个芯片中与芯片集成并共同制造。因此,液态冷却通道被嵌入到芯片有效区域的正下方,从而使冷却剂直接在热源下方通过(图1)。

单片集成歧管微通道散热器mMMC的制造过程主要包括三个步骤。首先,将窄缝蚀刻到涂有一层半导体氮化镓(GaN)的硅衬底中;狭缝的深度定义了将要产生的通道的深度。接下来,使用一种称为各向同性气体刻蚀的工艺将硅中的缝隙加宽到微流体通道的最终宽度;最后,微流体通道顶部的GaN层中的开口被铜密封,然后可以在GaN层中制造电子器件。与先前报道的制造歧管微通道的方法不同,该研究方法不需要在歧管和半导体芯片之间建立任何键合工艺。

该研究团队还将这种单片集成歧管微通道散热器,集成到了将交流电(a.c.)转换为直流电(d.c.)的功率电子模块上面。实验表明,仅使用0.57 W cm–2的泵浦功率就可以冷却超过1.7千瓦/平方厘米的热通量。其冷却性能系数与平行微通道SPMC相比增加了 50 倍。此外,由于消除了器件性能因为自热self-heating而引起的衰减,含有该液冷装置的功率模块的转换效率比未冷却的装置要高得多。

尽管该单片集成歧管微通道散热系统展示了非常高的冷却效率,但当前的几何优化研究仍然非常有限。歧管尺寸(宽度和厚度)和微通道(宽度和深度)的几何形状(例如歧管的数量,歧管厚度,通道厚度)还有大量的优化空间。我相信,通过系统地优化几何形状,在高传热系数和低泵浦功率的情况下,冷却性能可以实现更高的能源效率。

其次,这种嵌入式冷却解决方案实际上并不适用于当前的高性能处理器芯片,例如中央处理器CPU,图形处理器GPU或张量处理器TPU。对于基于硅通孔(TSV)的高性能三维集成系统,其主要的性能驱动力是高互连密度和高宽带传输,这使得芯片间的互连密度越来越高。但是,这种单片集成嵌入式歧管微通道冷却方案的局限性在于有源器件的源极(S)到漏极(D)间距的尺寸。在这项技术中,在S和D的位置刻蚀出一个大约1 微米的缝隙,然后进行第二步的各向异性的深硅刻蚀。这意味着,如果有源器件间距的尺寸越来越小(小于1微米),这项技术将变得非常困难。这种类型的解决方案适用于有源器件间距较大的高功率器件,例如基于GaN的功率器件。因此,该解决方案对电力电子设备最有意义,可用于电源和转换器,也可以广泛应用于数据中心,电动汽车转换器,核电系统以及RF功率放大器。这些冷却解决方案可用于通过功率电子设备冷却功率转换组件,例如前端AC-DC电源和DC-DC转换器模块,这些主要用于为数据中心中的服务器和IT负载供电。使用节能冷却解决方案,可以节省大量的电能和功率消耗。

另外,悬臂式的 GaN薄膜和铜密封层在器件长期服役工作条件下的可靠性需要研究。另一个问题是用于密封1微米切口沟槽的电镀层。光刻和电镀工艺的不完善会导致密封层质量下降。最后,该研究的集成芯片散热器和PCB的组装方法与行业中的电子封装和互连工艺并不兼容,如何在芯片/冷却器和PCB之间建立密封非常关键。

针对目前比较热门的三维封装集成技术,即芯片与芯片之间通过硅通孔(TSV)垂直集成,有源元件可以在芯片的两侧进行加工工艺。由于Elison Matioli 带领的研究团队所提出的单片嵌入式液体冷却装置具有间距的限制,将难以应用于三维封装集成系统。实际上,在过去的几年中,主要有三种解决方案来应对3D集成中的热挑战。第一种是“ICECool”的芯片间微沟道冷却方法,其中冷却剂以三维排列方式流过芯片之间的微间隙。第二种是DARPA提出的概念性“ICECool”在堆叠芯片间嵌入微流体沟道散热方法,其中冷却剂流过嵌入在半导体衬底的微沟道。第三个是基于芯片背面的冲击射流冷却技术,液态冷却剂可以直接对芯片背面的进行冲击射流散热,从而获得了很高的冷却效率。

尽管仍有许多挑战需要解决,但Matioli及其团队的研究工作朝着低成本,超紧凑和高能效的电力电子冷却系统迈出了很大的一步。他们的方法优于最先进的冷却技术,并且可能使产生高热通量的设备成为我们日常生活的一部分。

魏体伟目前是斯坦福大学机械工程系纳米传热研究组的博士后/研究员。他于2020年在欧洲微电子研究中心(imec)和比利时荷语鲁汶大学获得博士学位,专业方向为三维系统集成散热技术。他于2015年加入imec,致力于为高性能系统开发低成本、高效率的电子冷却解决方案。他在2020年获得了“ Imec优秀博士生奖”,并于2019年获得“比利时FWO奖学金”。他还获得了EPS / ECCC 2019 和ITherm 2019的Student Travel Grant,以及ICEPT2013优秀论文奖。他目前的研究兴趣包括用于高热通量应用的冲击射流冷却和嵌入式微通道冷却。

[1] Remco van Erp, et al., Nature (2020)

[2] Bose, Bimal K. IEEE Industrial Electronics Magazine, 2009, pp.7-11.

[3] T. Brunschwiler,et al., Journal of Electronic Packaging, 138(1), 2016.

[4] Hansson J, et al., Int. Mater. Rev., 2018, pp.22-45.

[5] T. Brunschwiler et al., ITHERM, 2006, pp. 196-203.

[6] E.N. Wang et al., IEEE J. Microelectromech. Sys., 2004, pp.833-842.

[7] T. Acikalin et al., IEEE ITherm, 2014, pp. 673-679.

[8] T.-W. Wei et al., IEDM 2017, pp. 32.5.1-32.5.4.

[9] D. B. Tuckerman et al., IEEE Electron Device Lett., 1981, pp.126–129.

[10] R. J. Phillips, Lincoln Lab. J., 1988, pp.31-48.

[11] G. M. Harpole, et al., IEEE Semi-Therm, 1991, pp. 59–63.

[12] Jung, K. W., et al., ITherm, 2017, pp. 98-104.

[13] Badaroglu, M. IRDS roadmap, 2017, pp.24.

[14] A. Bar-Cohen,et al., “DARPA Intra/Interchip Enhanced Cooling (ICECool) Program”, in CS ManTech Conference, United States, 2013, pp. 171–174.

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2430期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

IC设计|蓝牙

|

5G|封装|博通|台积电|中芯国际|EDA

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!