漫画芯片

2020-09-09

14:00:38

来源: 半导体行业观察

前言:

多年前,网上出现一组介绍集成电路(芯片)制造的漫画,而且有英文版。无论从专业角度还是漫画角度看,笔者认为漫画画的很棒!可惜网上漫画清晰度不高。笔者对这些漫画进行了清晰化,并配上了通俗的说明文字和示意图,整理成此文,试图以漫画为主、示意图和文字为辅,对芯片制造过程进行讲解。重点介绍在芯片上

集成

上百亿只

电路

元件的“

十八般武功”

,力求形象生动和便于理解。网上引用这组漫画的文章都未标出漫画原创作者,若读者有相关信息,请不吝赐教。笔者核实后,将在文中列出漫画原创作者。

小小芯片把人类带进信息化智能化世界,芯片和软件构成了信息化社会这座高楼大厦的基础。如果您对芯片还比较陌生,但近两年来,您已经知道了芯片超级重要后,一定想多了解一些芯片知识。下文将用漫画、示意图和说明等形式,通俗直观地对芯片及其制造过程进行介绍。

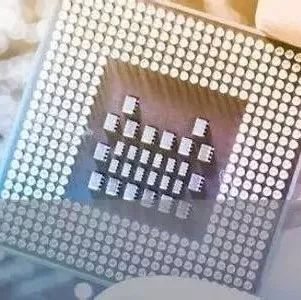

示意图1

带您认识一下用于制造芯片的

硅片

(晶圆),实现

芯片

功能的最小单元——

晶体管

,以及硅片、芯片和晶体管三者的关系。图中麒麟990是华为先进的5G智能手机芯片,采用7nm工艺制造,面积仅为113平方毫米(约1厘米见方,小手指甲大小),上面却集成了约103亿只晶体管。一只晶体管的三维(3D)结构如右上图所示。芯片制造厂采用的12英寸硅片的面积为70659平方毫米,用它大约可以生产600颗麒麟990芯片。

示意图2

左图是一张

芯片布图

(Layout)的局部,把它放大后,在其中找到了一个晶体管的布图,如红方框区域所示。一个晶体管在芯片中仅占头发丝横切面百分之一不到的面积,但它却是由复杂的电路结构组成。

晶体管从分布上看是平面的,但从横切面上看是立体的,

晶体管三维立体结构如上右图所示。芯片制造完成后,晶体管会“依托”硅片并“扎根”于硅片,上百亿只晶体管由纵横而不交错的金属线条连接起来,实现了芯片的功能。

如何在小手指甲大小的硅片上集成上百亿只晶体管等电路?在芯片制造时都用到了哪些高精尖的技术?下面就让机器人

小宝

带您走进芯片制造的微观世界,看看

集成电路制造

的神奇。

芯片制造过程大致分为四个阶段。下图中,1-2的工序是

芯片设计流程

,3-4-5-6的工序是

硅片制造流程

,7-8-9-10-11的工序是在硅片上制造电路元件的

电路制造流程

,12-13的工序是

收尾流程

。其中,硅片制造流程实际是芯片原材料加工过程,一般是在另外的专业工厂中完成。所以,硅片制造可以不包括在芯片制造过程中。本文为了让读者对芯片制造有全局了解,特把硅片制造也包含在芯片制造过程中。

(注:此漫画及后文所有漫画皆来源于网络文章,并经过了笔者加工整理。)

芯片设计流程

中包括了电路设计和光刻掩膜版制作。

电路设计

就是通常所说的集成电路设计(芯片设计),它是芯片产业链(设计、制造、封装、测试和应用)的首要环节,电路设计的结果是

芯片布图

(Layout)。

光刻掩膜版制作

是把芯片布图拆分成几十层~上百层用于制造芯片的图纸,并把每层图纸制作成

光刻掩膜版

(Mask),它们将在芯片制造过程中使用。假设一个芯片布图拆分为n层光刻掩膜版,硅片上的

电路制造流程

各项工序就要循环n次。

1.

电路设计

:

这是晶体管等电路元件摆放、连线和模拟的“设计功”。

设计人员要在图形工作站上,利用EDA软件,把上百亿只晶体管等电路元件合理

摆放

(Place)在设计区域,上下左右、纵横而不交错地准确

连接

(Route)起来,从而实现预想的电路功能。并且芯片布图在送去制造之前,要反复进行精确地电路功能

模拟

(Simulation),以保证芯片设计万无一失。

示意图3

是Intel公司2000年发布的奔腾P4 CPU的芯片布图,该芯片采用180nm的工艺制造,其上集成了4200万只晶体管,该芯片是台式计算机的CPU。20年后的今天,

华为手机CPU芯片麒麟990采用7nm工艺制造,集成了103亿只晶体管,规模是Intel P4的245倍,并且速度更快。

现在智能手机的处理能力比二十年前的台式计算机要强很多倍,芯片技术的快速发展功不可没。

2.

光刻掩膜版制作

:

这是把芯片布图拆分成光刻掩膜版的“分层功”。

这个工序是芯片制造前的准备工作,分层就是按照芯片制造的工艺要求,把芯片布图拆分成多达几十层的光刻掩膜图形,并制成一层层的光刻掩膜版。传统光刻掩膜版是在很薄很平整的石英玻璃上沉积一层厚约150nm的铬膜,并按光刻图形做出透光与不透光的图形。

示意图4

是一个晶体管(示意图2所示)的一套光刻掩膜版图,

如果芯片上集成上百亿只晶体管的话,光刻掩膜版上图形数量将是它一百多亿倍,复杂程度可想而知。

光刻掩膜版类似于传统照相底版,它上面的图形只有透光和不透光的分区,并精细的多。而照相底版有半透光的过渡性区域,而且精度无法和光刻掩膜版相提并论。

硅片制造流程包括了

单晶硅棒拉制

、

硅棒切片

、

硅片研磨

和

硅片氧化

共4个工序。硅片也叫晶圆,硅片制造也叫做硅晶圆制造。硅片制造一般是在另外的专业工厂完成,然后以原材料产品形式出售给芯片制造厂。硅片典型直径尺寸有4英寸(100mm)、6英寸(150mm)、8英寸(200mm)和12英寸(300mm)。

3.

单晶硅棒拉制

:

多晶硅到单晶硅的“单晶生长功”。

根据晶核排列是否同向,硅材料可分为单晶硅和多晶硅,半导体行业使用单晶硅,而且纯度要求为99.999999999%以上(业内简称 11N)。

单晶硅棒拉制

就是在多晶硅溶液中放入籽晶棒,在熔体温度、提拉速度、籽晶/石英坩埚的旋转速度等合适的条件下,随着籽晶棒边转动边缓缓地拉升,溶液中的晶核沿籽晶同向生长,一个以籽晶棒为中心的单晶硅棒就拉制出了。硅棒直径与条件控制和提拉速度有关。

4.

硅棒切片

:

硬碰硬地切片,要有切得很薄的“刀功”。

这道工序是把硅棒切割成硅片。由于硅棒直径和应用不同,硅棒切片的厚度也有差别。半导体用的硅片的切片厚度在450μm~750μm范围,太薄易脆裂不适合芯片制造。但太阳能用的硅片却是越薄越好,切片厚度仅为200μm左右(约2根头发丝的厚度),切割缝隙在120μm左右。由于硅棒非常坚硬,又要切的很薄,很考验设备的“刀功”。常见的硅棒切片方法为金刚线切割法和砂线切割法。

5.

硅片研磨

:

一丝不苟的“磨平功”。

成语中的“丝”如果是指头发丝的话,我这句话还应改为“万分之一丝不苟的‘磨平功’”。因为,半导体用的大硅片表面局部平整度(SFQD)要求小于设计线宽的2/3,如果大硅片用来制造14nm工艺的芯片,SFQD要求控制在10nm以内,即头发丝的万分之一。若选用7nm工艺,SFQD应小于5nm,硅片平整度要求更高。这道工序对研磨剂和研磨机都提出了很高的技术要求。

6.

硅片氧化

:

让半导体不导电的“绝缘功”。

半导体硅片可以经过加工变成导体,也可以经过加工变成绝缘体。这道工序是在硅片上生成一层很薄的氧化膜,使硅片表面成为绝缘体,为其后在硅片上制作电路元件做准备。氧化膜的成份是SiO2,具有良好的化学稳定性和电绝缘性,可用于晶体管栅极氧化膜、电绝缘层、电容器介质和屏蔽层等。硅片氧化工序还将在电路制造流程中多次应用,如果先做光刻再做氧化,将会在指定区域生成氧化膜,形成局部的绝缘保护。

准备好了硅片和光刻掩膜版,芯片制造就进入到了硅片表面电路制造的流程。该流程中包括了

光刻胶涂布

、

硅片表面上图形形成

、

刻蚀

、

氧化

、

扩散

、

CVD

、

粒子注入

和

平坦化

等工序。电路制造流程是一个循环流程,芯片成套的光刻掩膜版有多少层,这个流程就要循环多少次。每层光刻掩膜版表达的图形内容不同,流程中的个别工序也有可能被跳过。

7.

光刻胶涂布

:

在硅片上涂布光刻胶要有很好的“均匀功”。

一般旋转涂布光刻胶的厚度与光刻机曝光的光源波长有关(不同级别的曝光波长对应不同的光刻胶种类和分辨率)。厚度一般在200nm~500nm的范围。光刻胶是芯片制造的重要原材料,2019年7月日本为了抗议韩国法院对“韩国劳工”裁决,就用了光刻胶等原材料卡韩国的“脖子”,使韩国芯片产业一度困难。

示意图5

是一小块硅片上的硅片基底、氧化膜和感光胶的三层结构示意图。

8.

硅片表面图形形成

:

像传统照片洗印一样的“精准曝光功和洗印功”。

这道工序用来把光刻掩膜版上的图形投影到已涂布好的光刻胶上,进行精准曝光。这项工作由大名鼎鼎的

光刻机

来完成。在曝光之后,接下来要除去感光了的光刻胶,留下了未感光的光刻胶(假定使用了正性感光胶)。光刻掩膜版上的电路图形就精确地以光刻胶图形“做”在硅片的氧化膜上了。

示意图6

是光刻工艺中的曝光(上图)和除胶(下图)工序示意图,等同于传统照相过程中的曝光和洗印。感光胶有正负之分,感光的正性感光胶在显影除胶工序中被除去,保留了未被感光的部分。负性感光胶相反,未被感光的部分被除去,保留了被感光的部分。

9.

刻蚀

:

对光刻胶图形下的氧化膜进行“精准雕刻”。

这道工序用来把光刻胶覆盖的氧化膜保留,其它部分去掉。然后再把其余的光刻胶去除。这时,光刻掩膜版上的电路图形就精确地以氧化膜形式“做”在了硅片上。这项工作由

刻蚀机

来完成。工序7、8、9组成了芯片制造流程中最重要的

光刻工艺

(也称为

平面加工工艺

)。

示意图7

是把晶体管的第一张光刻掩膜版(示意图4)上的电路图形制作在氧化膜上的示意。同理,电路图形也可以制作在栅极多晶硅膜、绝缘钝化膜、蒸铝连线层上等。

10.

氧化、扩散、CVD和粒子注入

:

这是在硅片上“分区精加工的硬功”。

使用上述工序7、8、9的光刻工艺后,就可以在芯片的上指定区域进行多种

精加工

。

氧化

是在指定区域生成氧化膜;

扩散

是对指定区域定量掺入其它元素原子,改变该区域的电性能;

CVD

是在指定区域沉积一层氧化硅、碳化硅、多晶硅等半导体材料层;

离子注入

是向指定区域定量注入杂质的原子或粒子,使该区域的电性能发生变化。

示意图8

是制作晶体管的P型衬底(示意图2绿色区)的示意图。前道的光刻工艺在氧化膜上开了一个离子注入窗口,在这道

精加工

的工序中进行离子注入,使窗口下的硅片变为P型衬底。

11.

平坦化

:

电路图形表面“精确磨平功”。

在硅片上做了几层电路图形的“光刻”和“加工”循环(工序7、8、9、10)以后,有些地方刻蚀下去,有些地方生长上来,电路图形表面已变得凹凸不平。为了进行下一层的“光刻”和“加工”循环流程,首先要对电路图形表面进行平坦化。平坦化打磨要十分精确,打磨太深会损坏已做好的电路图形,打磨太浅电路图形表面依然不够平整。

平坦化工序完成后,跳回到工序7的光刻胶涂布,按照下一张光刻掩版开始下一循环的“光刻”和“精加工”过程。

示意图9

是高倍电子显微镜下看到的凹凸不平下层电路图形。

收尾流程

中包括了电极形成和硅片检查两道工序,这是芯片制造最后的收尾工序,之后就可以进行芯片封装了。

12.

电极形成

:

金属材料蒸发和淀积的“金属化功”。

在电路制造循环完成之后,还要完成一层晶体管等电路元件表层的铝金属连线,并要把芯片引出电信号的连接电极做好。把铝、铜等金属蒸发成气体,传送到芯片表面,并淀积生成一层金属薄膜叫做金属化工艺,金属化是一项难度很大的技术功夫。

13.

硅片检查

:

从批量芯片中找出不良芯片的“火眼金睛功”。

在芯片封装之前,要对硅片上成百上千的芯片进行检查,标记出不良的芯片,以便在后续的芯片封装时弃之不用。

芯片封装流程包括了硅片切割、芯片置放、引线键合、塑封模压、切筋成型、劣化试验、产品检验、激光打标八个工序,如下图所示。该封装流程封装的芯片都是四边引线的塑料封装(包括DIP、SOP、QFP、PQFP、LCC、PLCC等),这是传统的二维(2D)封装形式,本文对其中的每道工序不做详细介绍。

(注:此漫画来源于网络文章,并经过了笔者加工整理。)

示意图10

是目前芯片封装形式的全景图。分割线左侧是传统的2D塑料封装形式,右侧是更先进的新型封装形式,包括:以阵列引脚封装(PGA)、球栅阵列封装(BGA)、触点阵列封装(LGA)等为代表的球阵封装;晶圆级封装(WLP);系统级封装(SIP);堆叠封装(PoP);多芯片组封装(MCP)和芯片级封装(CSP)等。其中除了球阵封装外,其它都属于系统级或者三维(3D)先进封装。而且随着技术进步,新型封装技术将不断推陈出新,以满足各种新的应用需求。

(注:此图片来源于网络:今日半导体,并经过了笔者加工整理。)

结语:

芯片设计和硅片生产是芯片制造的前期准备,电路制造有三个重点内容要了解,

一是

硅片上的电路是按光刻掩膜版的顺序,一层层用光刻平面工艺循环加工而成,芯片上的电路元件是立体的。

二是

光刻工艺有4个步骤:涂胶、曝光、除胶、刻蚀,光刻是芯片技术的核心。

三是

每一循环加工都是由光刻和加工两个阶段组成,光刻指定了后续加工的范围、区域和窗口,后续加工是对硅片上材料真正的处理过程,包括氧化、扩散、CVD、离子注入、钝化等处理。

在芯片制造过程中,芯片设计阶段用到了电路元件摆放、连线和功能模拟的“设计功”、把芯片布图拆分成光刻掩膜版的“分层功”;硅片生产阶段用到了“单晶生长功”、“硅棒切片功”、“硅片磨平功”和“半导体绝缘功”;在电路制造阶段用到了光刻的“精准定位功”和“精细加工功”;在芯片封装阶段也有各种各样的真功夫。芯片制造中的真功夫是芯片高技术含量的具体体现。用漫画把这些真功夫都一一表达出来,其实是一件很难的事情。在此,笔者向文中所引用漫画原创作者致敬。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2427期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

IC设计|蓝牙

|

5G|封装|博通|台积电|中芯国际|EDA

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie