[原创] 一文看懂台积电的技术布局

2020-08-26

14:00:18

来源: 半导体行业观察

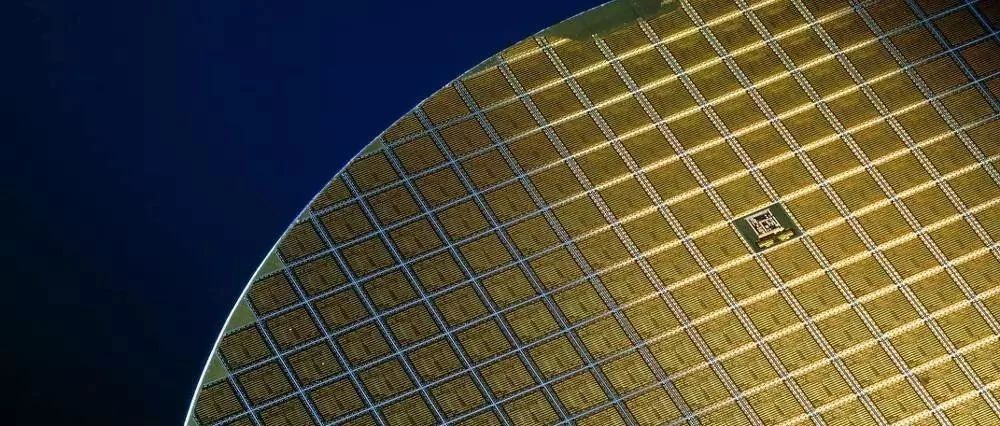

台积电是全球领先的晶圆代工厂,这是一个不争的事实。

根据集邦咨询的最新数据预测,受惠于5G建设持续部署、高效能运算和远程办公教学的CPU、GPU等强劲需求,台积电产能维持满载,二公司在2020年第三季的营收预计将增长21%,继续稳坐晶圆代工龙头的位置。从集邦咨询提供的数据可以看到,届时台积电的市场份额将高达52.9%,遥遥领先于排在后面的竞争对手。能获得这样的表现,与他们在技术方面的多维布局有莫大的关系。

日前,台积电举办了线上技术大会,揭开了公司多项技术布局和未来发展方向。半导体行业观察特此摘要,以飨读者。

在技术大会上,台积电资深副总裁,业务开发张晓强首先做了一个演讲,介绍了台积电技术的发展规划和对半导体技术未来的看法。

张晓强指出,半导体工艺的发展越来越复杂,台积电的研发也日益增加。在2019年,台积电的研发投入达到了30亿美金,只有这样持续的投入,才能保证我们的半导体技术能持续发展。张晓强同时还强调,台积电目前正在建设一个新的研发中心,在这个中心内将会有一个全球最先进的研发生产线。2021年,新的研发中心将容纳八千人的工程师,一起开发未来的半导体工艺。

接下来,我们来谈一下台积电的先进工艺。首先要谈的是7nm工艺。

张晓强表示,在2017年,台积电领先业界,首先进入7nm时代,这个工艺在今天也成为了AI和HPC的中坚节点。到目前为止,台积电已经在这个节点上获得了超过120个NTO,这些NTO很快将会投入量产,而到本年末,NTO数量将会突破两百个。截止到今天,台积电已经生产了超过10亿颗7nm芯片。在7nm时代,台积电还率先推出了使用EUV技术的7nm+工艺。台积电在这方面也有多年的研发经验,并成为业内第一个把EUV投入量产的企业。

在去年下半年,我们推出了6nm工艺,希望用更先进的工艺来实现更高的逻辑密度,这个平台的另一个特点就在于其与7nm工艺平台的兼容性,这样的话客户就很容易把7nm的设计移植到6nm。目前,这个工艺已经开始试产了。

2020年,台积电开发工艺的另一个里程碑是5nm的量产,与7nm相比,新工艺的速度提升了15%,功耗降低了30%,而逻辑密度则是前者的1.8倍。在良率方面,新工艺的进展也非常顺利。其D0已经超越了同时期的7nm。

与此同期,我们还推出了增强版的N5P工艺制程,把晶体管的速度了5%,还带来了10%的功耗降低,这将给HPC带来新的机会。

张晓强在会上表示,台积电还基于N5的平台推出了一个N4工艺,新工艺的速度、功耗和密度都有了改善。而其最大的优势同样是在于其与N5兼容的设计规则、SPICE和IP。这样的话,使用5nm工艺设计的产品能够轻易地转移到4nm的平台上来。这也能保证台积电客户在每一代的投资,都能获得更好的效益。N4试产将在2021年第四季度,而量产将会在2022年实现。

从张晓强的介绍我们得知,台积电目前最新的工艺是3nn工艺,在这代工艺上,台积电继续采用FinFET晶圆管。这主要是台积电基于两方面的考量,做出的决定:一方面,我们的研发团队通过不断创新,用新的方式把FinFET的性能提升到一个新的高度;另一方面,我们希望能够客户能够可以尽快升级其技术,获得更优的体验。

“基于这两点考量,我们在3nm工艺上,将继续使用FinFET,而这一点工艺将在性能、功耗和密度上也会有明显的提升”,张晓强说。如下图所说,与5nm相比,台积电的3nm的速度将提升10%到15%,功耗将提升25%到30%,逻辑密度将是前者的1.7倍,SRAM密度也将能提升20%,就连模拟密度也提升了10%。根据台积电规划,3nm工艺将在2022年下半年进行量产。

在讲述了台积电目前的规划和量产时间点后,张晓强分享了台积电对工艺技术未来发展的看法和他们的一些技术研究成果。

张晓强指出,晶体管是半导体技术的核心,是上世纪最伟大的发明之一。而经过过去数十年的演变,晶体管已经从平面走向了3D。他表示,虽然我们现在的芯片还被成为硅芯片,但现在已经有越来越多的半导体材料被住入到先进工艺的芯片中,以改善提高半导体的质量和稳定性。张晓强表示,在未来,一些新的2D材料和硫化物,以及NANO SHEET架构等选择,将会成为未来芯片性能提升的潜在解决方案。

来到台积电方面,据张晓强介绍,他们在nanosheet方面已经有超过15年的研发经验。从下图左图可以看到台积电目前能做到的nanosheet构造。这种设计能大大改善晶体管的质量,这在低电压的场景下,效果更为明显。“我们已经成功生产出了32 Mb nano-sheet的SRAM”,张晓强说。其在低电压上的表现,能为未来的低功耗因公提供广泛的支持。

来到2D材料方面,张晓强表示,台积电认为包括硫化钼和硫化钨在内的的一系列硫化材料显示出非常好的特性。能符合未来的小节点的沟道各种需求。从下图右可以看到,台积电基于硫化物2D材料获得了历史新高的On-current。

张晓强进一步指出,在芯片未来的设计,电源管理变得越来越重要,而在传统的设计中,一般会使用一个叫做Power Gating的晶体管来控制电流的开关,这个晶体管目前的设计是将其放置在硅衬底上,这就必然带来了极大的功耗浪费。而台积电的研发团队则成功的把碳纳米管嵌入到一个CMOS的设计中,用来实现Power Gating的作用,这成功解决了上述的问题。也给未来的应用带来了新的机会,缩小了面积,这将给未来的微缩提供新的思路。

在EUV方面,台积电已经进行了深入的研究,公司也跟ASML等多个公司合作,推进EUV的商用,目前公司在EUV的OPC、光罩和光阻等多个方面都有投入。

目前,台积电在EUV方面有了一个创举,通过他们的实现,获得了业界最小的mental pitch。这对于未来的晶体管的微缩,是非常重要的。

我们知道,现在的芯片越来越复杂,工艺的开发跟芯片设计的结合也变得越来越重要,为此台积电的工艺开发和设计队伍一起工作,推动DTCO的发展,台积电在这方面也获得了优越的成绩。这对推动未来芯片的发展同样重要。

张晓强指出,未来的半导体发展不应该只关注晶体管电流,在速度方面提升方面面临的挑战还来自电阻和电容,这两方面如果不能提升,将会影响晶体管的继续微缩,台积电在这方面也做了大量的研发工作。

先看晶体管方面,我们知道晶体管有一个重要的元件,叫做“gate t0 drain”,这部分变得非常重要。对晶体管的质量有重要的影响,台积电通过一个创新技术将其降低。

在未来的晶体管设计中,后端的RC delay变得非常重要,台积电在这方面也有深入的研究。而这些技术也都会微未来的晶体管微缩提供重要贡献。

“台积电未来将会持续从研发、投资和创新三方面入手,推动新技术的开发,把最先进的工艺和最领先的技术带给我们的客户,让我们的客户打造创新的产品。一起创造更美好的半导体未来”,张晓强最后说。

众所周知,因为受到硅材料本身和技术的限制,摩尔定律接近失效,而过去以微缩晶体,提高单位面积晶体管密度来提高芯片性能的方法以及逐渐失效。为此,台积电开发出了多项前段和后段的3D封装技术,以推动芯片性能的提升。在日前的技术大会上,台积电副总裁,研究发展余振华分享了台积电在先进封装上面的一些发展现状和未来规划。他首先指出,现在台积电推出了一个晶圆级系统集成平台技术。

在他看来,这是一个破坏式创新的技术平台,当中包含了CoWoS和InFo这两个被称为先进后段3D的技术。余振华指出,这个技术从推出到现在,已经被广泛应用到智能手机、数据中心、人工智能训练与超级电脑等超过一百种产品以上,实现了系统的创新;在这个平台上,还包括了一个相对比较新,但更具有弹性的SOIC 3D堆叠技术,这是在芯片制造的前端实现。通过这项技术,能够实现芯片之间更紧密的连接,协助摩尔定律的延续。

“受益于前段3D和后段3D的创新,台积电能够提供产业界最先进的异构系统整合平台,在满足当前应用发展需求,还能延续技术创新”,余振华表示。与此同时,台积电宣布了全新的3D Fabric,以其代表台积电先进的系统级晶圆集成平台。在余振华看来,新的命名能简单表达制程整合的次序。例如前段整合,分别展现了芯片堆叠在晶圆、或者晶圆堆叠在晶圆上面。而在过去的一年中,台积电在这些技术上面取得了长足的进展。

首先看SOIC方面,在这方面,台积电采用了自己研发的高性能技术,以最近的距离整合芯片,达到高频宽、高功效和紧密堆叠的效果。SOIC同时还能提供极具弹性的堆叠方式。如F2F、F2B,CoW、WoW、LoL以及LOM等等,这些堆叠方式不但能够满足广泛的应用需求,还能达到长期的技术演进目标。

余振华进一步指出,在我们进行3D堆叠时,对系统的散热会提出更高的需求,从下图我们可以看到相关散热效果对比.由此图可以看到爱几点SoIC技术在散热方面的优势。从台积电提供的数据可以看到,这个提升高达35%。

而在SoIC的验证部分,如下图所示,SOIC都能通过验证,且有良好的表现。

而在Design Rules的Roadmap方面,台积电对SoIC也有了不小的寄望。余振华表示,在每一代的SoIC技术上,公司都希望能达到70%的线性微缩率。

余振华在会上指出,SoIC的研发着眼于广泛的应用,其中之一是高频宽、高效率的逻辑与存储的堆叠,这对于未来的HPC和AI的应用非常重要。而台积电则在这方面提供了低温多层记忆体芯片堆叠在逻辑器件上的结果。据透露,台积电在其上面堆积了四层、八层和十二层的芯片。

如上图所示,有12层芯片堆叠在逻辑器件上,但其总厚度低于600μm,那就意味着这可以持续堆叠到16曾,甚至更多的层数。按照余振华所说,SoIC不但能用于主动器件之间的堆叠,还能实现主动器件到被动器件的堆叠,满足更多“More than Moore的应用”。

除了广泛的应用,我们希望SoIC能够满足 system scaling长期演进微缩的需求。如上图所示,这是一个里程碑式的成果,能够协助实现延续摩尔定律的目标。从图示也能看到,金属的结合、设备的良率与耐用性也能令人满意。

接下来我们看一下InFo技术在logic chilets整合方面的应用,其中,InFo-R的应用越来越多,这是因为InFo-R在带宽和Cycle time等多方面的优势。如下图所示,InFo-R能提供高密度RDL。在水平方向上,InFo-R能提供了最小线宽和线距仅为2μm的连线。在垂直方面,这个技术提供了40μm的micro bump和130μm的Cu Bump。随着HPC等应用的需求,台积电计划明年推出2.5倍InFo-R的验证。在余振华看来,行业需要110平方毫米的的基板来做整合。这不但代表了新的挑战,还带来了新的机会。

为了满足芯片间更高密度的RDL需求,台积电还提供了InFo-L制程,通过在InlFo-R中加入了loca silicon interconnect(LSI)来达到上述目的。InFo-L技术不但提供了更高密度来节省芯片面积,也提供了最小的线宽和线距。这个技术将在明年初完成相关验证。

综上所述,随着不停止的高速运算需求,基板面积与导线层数快速增加,但这种基板的绳产量率与耗电逐渐成为产业发展的瓶颈,为台积电提出新的解决方案InFo-SoIS。这个技术借助InFo技术来打造新的基板,在其中整合了超大尺寸的InFo,通过整块的基板来提供高良率和高可靠性。台积电也已经成功的以InFo-SoIS试产了91平方毫米尺寸的基板,且实现了超过90%的高良率。

除了高良率,InFo-SoIS也具有高性能和高效率的特点。如下图所示,与传统基板比较,In-FO-

SoIS基板的优势相对较为明显。

来到COWoS-S技术方面,据余振华介绍,台积电在十年前就与领先的客户推出了相关技术。并开 启了近代先进系统整合的年代。根据规划,到明年,台积电在这方面的技术能支撑在设计中整合逻辑和8个HBM。把reticle size提高到三倍。到2023年整合的HBM更将高达12个。

除了增加Silicon Interposer的Size以外,台积电还在三个关键领域增抢CoWoS-S的运算能力与效率。当中包括了引入iCap来增加PI(Power Integrity);引入下一代的Interconnect以增强SI(signal Integrity)和下一代的TSV。

余振华接下来介绍了全新的CoWOS-L技术。通过将Silicon Bridge和RDL技术与CoWoS技术结合,不但带来了更高的带宽,还能带来更好的成本控制。也能提供更强的灵活性。

为了缩短Time to Value的时间,台积电提供了新的标准架构STAR,它借助于CoWOS已有的良率和可靠性,带来更好的方案。

为了实现More Moore和Moore than Moore的高度整合,台积电开发了业界第一个前段3D与后段3D整合的方案。下图展现了SoIC与InFo的整合。达到了最佳的系统PPAC。

为了推出优化更好的系统,台积电开发了SoIC和CoWOS整合,以满足更强的芯片需求。

余振华指出,芯片间内部连接密度的持续增加,能够支持chiplet集成与异构整合技术的持续进步,为此台积电提出了一个新的3 ID Roadmap。台积电提议,3DID每两年增加两倍,以满足功能和功耗的目的。这个可视为摩尔定律的2.0版本,能够有效地引领产业界的研发。

“我们为半导体产业的演进提供了新的技术平台,以创新方式整合了前后3D技术,这将为客户提供最大的创新支持”,余振华最后说。

在讲述了公司在先进逻辑方面的布局,台积电资深总监、业务开发刘信生对台积电的特殊制程进入了深入的讲解,这是台积电技术里面极容易被忽略的一部分,但却在公司未来的发展中扮演了重要角色。

从刘信生的介绍我们得知,自2009年以来,台积电在这方面技术取得了杰出的成绩,其等效八英寸晶圆的年平均复合增长率也高达17%。据介绍,在2019年,台积电在这方面取得了1270万片等效八英寸晶圆的出货量。

而在这些工艺技术的投入方面,台积电也持续增长。如下图所示,自2014年以来,台积电在这个领域研发的平均年复合增长率同样达到17%。

据介绍,台积电能提供MEMS、图像传感器、嵌入式NVM,RF、模拟、高电压和BCD功率IC方面都有投入,这是业界最为广泛的产线。但与其他竞争对手不一样的,台积电希望用最先进的工艺,给客户提供最好、最优质的的服务。也能与先进工艺实现更好的集成,做出更好的应用。而台积电所有的这些技术都是建立在一个低功耗的平台上面。

刘信生指出,台积电在基本的逻辑技术基础上,会加上先进的ULL&SRAM、RF&Analog以及eNVM技术,实现低功耗以及模拟技术的提升。这是所有产品的基础,可以在此框架上实现整合。

特殊制程应用的最广泛的场景就是IoT,以致发展到AIoT。刘信生表示,以后的市场会往智能设备发展,而携带AI的设备才是智能设备。这么多装备上会展现出不同的性能以及不同的理解,这些都需要不同的技术来维持。台积电拥有从8寸到12寸的技术支持,具有很多投入。

单从低功耗来说,就有0.18um eLL、90nm ULP、55ULP等基础线。可以利用这些做最好的AI应用。同时,台积电还推出了最新的Finfet技术-N12e,可以打造高效高能的产品。

具体来说,N12e要取代的是22ULL,可带来76%的逻辑密度提升,给定功耗下49%的频率提升、给定性能下55%的功耗减少以及SRAM尺寸50%的缩减。

N12e支持的Vdd电压能够做到0.4V,可以说完美适配IoT设备。事实上台积电的规划就是,面向5G处理器、基带、无线耳机、智能手表、VR、可穿戴设备、入门级SoC等场景领域服务。

谈到RF方面,刘信生指出这其中目前最大的难题就是5G,其在能耗上比4G多了50%以上,该怎样处理这个问题?台积电在这方面也有特别的解决方案。

首先是N16 FinFET,其本身就是支持Sub-6GHz 频段的很重要的技术,目前已经量产。Sub-6GHz 频段是5G的主力。目前已经在28GHz毫米波频段上实现了5G上连接,其同样需要改善速度。台积电在N16上做了很多改善,最重要的就是在f

T

,f

MAX

上的改善。首先,f

T

在N16已经做到了超过300GHz的性能,f

MAX

则超过了400GHz。刘信生表示在N16对于RF来说将会有很长的适用时间。从Sub-6GHz的运用到毫米波的运用,N16 都可以给予市场想要的全新的需求。

接下来是N6,台积电也会继续推出Sub-6GHz收发器方案。主要的改善的方面是功耗。从28HPC、16FFC到N6RF,在P

Dc

方面,就能达到50%的提升。

台积电还在eNVM上进行投入,探索MCU等应用上将eFLASH代替。据介绍,他们的40nm RRAM在2018年上半年就风险试产了,而28nm/22 nm的RRAM也会在2019年下半年风险试产;他们同时还拥有比eflash还快三倍写速度的22nm MRAM,这个工艺也在2018年下半年就风险试产。

能获得上述成功,正如前文所说,台积电的庞大投入功不可没。据介绍,台积电近些年每年的研发投入都达到100亿美金。

台积电同样在eNVM上实现了创新,主要是在PRAM和MARM上。

至于Power IC方面 ,虽然这是最保守的产业,但新的应用也需要新的解决方案。台积电专注于Smart PMIC 。该解决方案具有高质量数字(>1M gates),适用于模拟&隔离,高效率以及高密度 eNVM等优势。

还有CIS领域,目前手机上携带镜头现在越来越多,技术也在继续进步。台积电的技术非常适合推进产品的发展。

台积电在Sensor,Stacking和ASIC(ISP)方面都在延续自己的技术。Sensor方面从N65BSI 一直到N65BSI,而Stacking方面,则是从BSI到ADvanced Pixel Level Stack,ASIC(ISP)方面则是从N90LP到N65LP。

Display方面,LCD屏幕发展了很多年,最近OLED诞生以后,整个产业与技术都在大幅成长。从8寸到12寸,台积电都有相关服务提供。其中最新的就是28HV技术。

这其中采用台积电非常成熟的工艺,具有超低功率以及对模拟设计非常友好。

在对台积电的技术平台进行了介绍之后,我们还要继续看一下台积电公司的路线图和产能布局,因为这是能维持台积电领先的根本。而台积电营运组织资深副总经理秦永沛也指出,台积电逻辑产能高居全球第一,大幅超过第二名公司逾3倍。

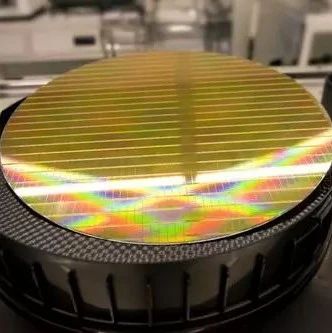

台积电的先进制程生产基地位居台湾北中南,7nm在中科,5、3nm位于南科,2nm制程将落脚在竹科,目前正在取得土地中。

秦永沛表示,持续不断投资新产能、扩充产能及提升制造能力,致力成为全球逻辑产品长期且最值得信赖的技术及产能提供者。

在产能方面,他指出,自2016年至2020年以来,台积电年复合成长率达28%的速度成长。

台积电2018年导入7nm量产,因客户需求非常强烈,快速提升7nm产能,估今年7nm产能将较2018年成长超过3.5倍。

今年第二季量产的5nm,秦永沛指出,位于南科的晶圆18厂1到3期是5nm量产基地。

其中,1、2期已开始量产,3期正在装机。他估计,2022年5nm产能将较今年成长超过3倍。

南科晶圆18厂的4到6期,规划为3nm量产基地,目前正兴建中,南科14厂区附近也将新建特殊制程与先进封装厂。

此外,秦永沛表示,台积电竹科研发中心已开始兴建R1,预计2021年完工,未来将是2nm及更先进技术的研发重镇,他也指出,2nm生产基地将位在竹科,目前正在取得土地中。

秦永沛强调,台积电每年投资逾100亿美元扩充产能,他引用统计指出,台积电提供的产能高居全球第一,大幅超过第2名公司的3倍以上。

台积电在5nm将全制程采用极紫外光(EUV)技术,秦永沛表示,台积电EUV机台占全球比重达50%,晶圆移动占全球比重更超过60%,预计透过累积更多成功经验,是台积电的竞争优势。

台积电也在积极增加特殊制程产能,秦永沛表示,台积电特殊制程产能持续成长,2015年占总产能约38%,今年特殊制程产能将较去年成长10%,占总产能比重将高达54%。

从上文我们可以看到,台积电能在过去多年里一直统治晶圆代工市场,且在近年来愈发强大,是公司持续投入研发的成果。展望未来,后来者想挑战台积电,相信不会是一件容易的事情。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2413期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|蓝牙

|

5G|EDA|华为|英伟达|封装|手机芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie