[原创] 英特尔的制造困境:从10nm谈起

2020-08-06

18:27:22

来源: Sophie

来源:内容编译自「

eetimes

」,谢谢。

如果一家企业是全球最大的半导体厂家,那么为了维护其自身在业界的地位、时刻领先于竞争对手,这家企业就要设定具有前瞻性的公司目标。英特尔把10纳米工艺技术设定为公司的前瞻目标,但是,由于10纳米节点技术的大幅度延迟,迫使英特尔不得不更改公司的技术蓝图(Road Map)。

英特尔甚至一度陷入了不得不讨论采用其他战略的困境,如今,英特尔虽然还在为10纳米工艺而进行研发,由于TSMC、三星电子在致力于7纳米、6纳米、5纳米以及更高级别工艺,那么,英特尔现时间点到底处于什么位置呢?

要研发一项新的工艺技术,企业需要对性能、电力、面积(PPA:Performance, Power, and Area)设定一定的目标。在英特尔的处理器、微架构(Microarchitecture)的“Tick-Tock模式(即嘀嗒模式,工艺年-构架年)”下,PPA所有内容都得以进步和发展。英特尔的目标是把10纳米(也被称为“Intel 1274”)晶体管的密度提高至14纳米的2.7倍,性能提高25%。

从近期公布的10纳米的特征来看,与TSMC第一代的7纳米工艺(N7)极其相似,英特尔曾计划在2016年(比TSMC的N7量产时间早两年左右)开始10纳米工艺。如果按照计划进行下去的话,英特尔在HPC(High Performance Computing)方面会远远超过竞争对手。

英特尔与TSMC的工艺比较。(图片出自:eetimes)

英特尔把“提高晶体管的密度”称为“Hyper Scaling(超级微缩)”,后来,由于良率低于预想、成本高于14纳米,导致英特尔不得不重新审视目标。另一方面,就10纳米工艺而言,为了维持“摩尔定律”、维持晶圆的较小尺寸(Die Size)、削减成本,相对其他工艺而言,10纳米工艺需要更多的微缩技术。

在英特尔的10纳米工艺中,使用了FinFET晶体管、13层的金属堆(Metal Stack)。作为一项促进“Hyper Scaling(超级微缩)”实现的主流技术,首先,需要COAG(Contact Over Active Gate)。由于最初的2层采用了Co(钴,Cobalt)Inter Connect(钴互连)技术,因此与W(钨,Tungsten)相比,单位面积的电阻削减了50%,此外,为了缩小以上这些互连(Inter Connect),电子迁移从5/1削减到了10/1。

此外,在前道工艺(FEOL ,Front End of Line)中要制成Fin,有SAQP(Self-Aligned Quadruple Patterning,自对准四重图案)、SADP(Self-Aligned Double Patterning,自对准双重图案)方法,后道工艺(BEOL, Back End of Line)也可用为制成特殊金属层的SAQP方法。此外,还有Single Dummy Gate等技术,最为流行的方法还是以上列举的。

由于现有的所有尖端工艺技术都依赖于多图案(Multi-patterning),因此要实现英特尔10纳米工艺的特定功能,就需要使用4x,5x,6x图案(Patterning)。

然而,为了获得某一项功能,需要对晶圆进行六次曝光,这才是最复杂的。就多图案(Multi-patterning)而言,生产周期长,而且缺陷较多,因此,产品良率低、成本高、收益低。可以说,为了获得“Hyper Scaling(超级微缩)”,在不使用EUV(极紫外光刻)的情况下,过多地使用多图案(Multi-patterning)是一种非常冒险的选择。

此外,英特尔是唯一一家为7纳米、10纳米的BEOL而采用SAQP的半导体厂家,因此有观点认为“是SAQP导致了产品的缺陷密度高”。

就在10纳米(以及更高代际)工艺中采用Co、Ru(Ruthenium,钌)而言,可以列举出很多理由,然而在英特尔当初致力于研发10纳米的时候,Co还是较新的材料,因此也有观点表示“产品缺陷密度高的原因在于Co”。后一种观点明显不是“嫁祸于人”,因为要采用Co,需要使用新的检查工具(采用了电子束)。

与现行的光学检查工具相比,单束(Single Beam)检查工具速度慢(Multi电子光束工具还处于研发阶段,速度也很慢)。但是,就光学检查工具而言,新的(或者研发中的)工艺的清晰度不够。因此,目前电子光束工具仅可用于工艺质量确认、校正(Calibration)等用途。

英特尔冒着风险、先于业界其他厂家采用新技术并不稀奇。但是,就10纳米的研发而言,已经远远超过了“改革”的框架,风险极高。

美国的市场调查公司Insight 64的调查员Nathan Brookwood表示:“据业内相关人员透露,回顾一下历史,再看看整个英特尔,无疑不让人觉得英特尔的确充斥着过激的攻击行为”。

英特尔最早公布10纳米工艺是在2015年7月。当时,英特尔指出此项工艺存在Multi-patterning缺陷密度高、良率低的问题。而且,10纳米(品名:Cannon Lake)的量产时间是在2017年的下半年,相对原计划晚了一年左右。

2018年年初,英特尔表示:“Cannon Lake已经开始小规模量产,2018年下半年计划开始量产”。但是,2018年4月,英特尔又公布说:“由于良率较低,10纳米工艺CPU的量产推迟到2019年”。后来,2019年量产了第二代10纳米工艺(注意,不要与10纳米+工艺混淆),与首代10纳米工艺技术相比,很多方面都有明显的优势。

英特尔本身应该在2015年(首次正式公布10纳米的时间)甚至之前就已经了解10纳米工艺的优缺点。在充分了解了风险的基础上,英特尔认识到必须要在未来数年内大批量生产与成本、性能、市场投入时间相匹配的CPU。

于是,在2016年年初,英特尔新发布了新的基本理念,目的是为了导入新工艺技术、微架构(Microarchitecture)。也就是说,延续了十年的“Tick-Tock模式(即嘀嗒模式,工艺年-构架年)”寿终正寝,新的“PAO(Process-Architecture-Optimization,制程-架构-优化)”开始上场。即,通过长期优化微架构(Microarchitecture),反复改善工艺技术、产品设计。

Brookwood指出,可以说,“Tick-Tock模式”是降低风险的战略之一,运用现有的微架构(Microarchitecture)、对新的工艺进行试错(Debug),然后在验证后的工艺中导入新的微架构,由此可以达到年度一次的性能改善。

某位英特尔的前员工曾明确表示,从市场的观点来看,“Tick-Tock”本身就是为了获得较高评价而诞生的一种模式,管理层进行审视这种模式的时候,也定期、有规律地推动了此种模式的实现。因此,毫无疑问,大家都朝着目标努力,而且,大家都忘记了这个模式到底有多难。

Brookwood表示,十年来“Tick-Tock”充分发挥了其作用。但是,在14纳米中稍微“跌了个跟头”,导致量产时间延迟一年,而且在10纳米工艺中彻底“崩塌”!另一方面,TSMC却保持两年更新一次的步调,虽然TSMC的性能提高速度不太快,但性能预测的准确度却极高。谁也没有想到的是:在英特尔还在14纳米“徘徊”的时候,AMD几乎已经将所有系列的产品委托给TSMC的7纳米工艺生产。

“14纳米+”是英特尔14纳米工艺的优化版。与采用了14纳米工艺的“Skylake”相比,采用了“14纳米+”工艺的“Kaby Lake”的功耗仅提高了15%,基本没有大的改善。

此外,进一步优化的版本--“14纳米++”的栅极距(Gate Pitch)为84纳米(与14纳米工艺下的70纳米相比,有所改善),且驱动电流提高了24%,因此功耗降低了约50%。英特尔的“14纳米++”主要应用于名为“Coffee Lake”、“Comet Lake”的处理器(主要用于高端的台式游戏机PC、高端PC等产品)。由于英特尔未来还会继续致力于处理器的研发,因此不仅是10nm+&10nm++、应该还会出现7nm&7nm+&7nm++。

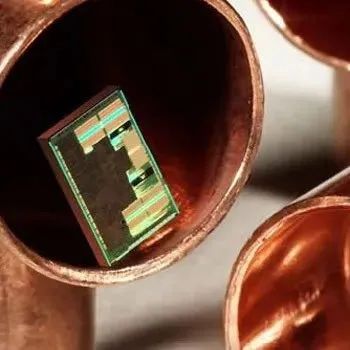

晶体管的性能、耗能。(图片出自:eetimes)

另一方面,英特尔的CEO似乎也在考虑“将主要技术的研发基准时间从两年延长到两年半”。但是,这到底能为英特尔带来什么结果呢?不经过时间考验、无从得知。

英特尔的企业信息管理部的负责人曾表示说,我们的目标是每年更新一代技术,以支持公司的产品蓝图(Road Map)。因此,通过同时进行工艺节点(Process Node)微缩化和提高节间(Internode),来达到提高PPA的效果。

英特尔必须做出改变的地方不仅仅是生产工艺的研发方法。

在很早之前,由于产品设计、生产技术处于调整中,因此当英特尔在进行某种产品设计的时候,必须要使用专用的工艺。但是,如今已经将产品与工艺技术的研发分开,因此可以将最可行的技术应用于未来计划发布的CPU和GPU的研发中。

这种模式与Fabless Chip Maker(芯片设计商)&Foundry之间的关系比较类似。GLOBALFOUNDRIES的前CTO(Chief Technology Officer,首席技术官)--Gary Patton(也曾担任IBM Microelectronics事业部的负责人)于2019年入职英特尔,且英特尔筹备了将设计应用于特定的工艺节点(Process Node)中所需要的要素。据说Patton担任Process Design Kit(PDK)、IP(Intellectual Property)、工具(Tool)等方向的研发管理工作。

晶体管的性能、耗能。(图片出自:eetimes)

另一方面,英特尔的CEO似乎也在考虑“将主要技术的研发基准时间从两年延长到两年半”。但是,这到底能为英特尔带来什么结果呢?不经过时间考验、无从得知。

英特尔的企业信息管理部的负责人曾表示说,我们的目标是每年更新一代技术,以支持公司的产品蓝图(Road Map)。因此,通过同时进行工艺节点(Process Node)微缩化和提高节间(Internode),来达到提高PPA的效果。

英特尔必须做出改变的地方不仅仅是生产工艺的研发方法。

在很早之前,由于产品设计、生产技术处于调整中,因此当英特尔在进行某种产品设计的时候,必须要使用专用的工艺。但是,如今已经将产品与工艺技术的研发分开,因此可以将最可行的技术应用于未来计划发布的CPU和GPU的研发中。

这种模式与Fabless Chip Maker(芯片设计商)&Foundry之间的关系比较类似。GLOBALFOUNDRIES的前CTO(Chief Technology Officer,首席技术官)--Gary Patton(也曾担任IBM Microelectronics事业部的负责人)于2019年入职英特尔,且英特尔筹备了将设计应用于特定的工艺节点(Process Node)中所需要的要素。据说Patton担任Process Design Kit(PDK)、IP(Intellectual Property)、工具(Tool)等方向的研发管理工作。

英特尔未来还会继续致力于提高工艺技术水平。作为10纳米工艺的两个优化版本,计划在2020年推出10纳米+,2021年推出10纳米++。

英特尔的前高级研究员(Senior Fellow)、工艺架构(Process Architecture)&统筹(Integration)部门的总监--Mark Bohr先生在2017年表示,英特尔的10纳米+晶体管的性能优于10纳米,但是频率低于14纳米++,因此,对于桌面游戏机PC的CPU而言,这不是一款有魅力的产品。考虑到10纳米存在着缺陷密度高的问题,同样,频率问题也是10纳米+最应该优先解决的问题之一。

英特尔计划在2020年下半年量产晶体管性能大幅度提高的10纳米++。届时,对于具有较高“时钟频率(Clock Rate)”优势的应用(Application)而言,10纳米++将会是不错的选择。另一方面,英特尔自身也承认10纳米工艺产品的利润不及22纳米、14纳米。

2020年年初,英特尔的CFO(最高财务总监)-- George Davis表示,“10纳米应该不是英特尔最厉害的技术节点。与14纳米、22纳米相比,10纳米的良率较低,但我们正致力于解决这一问题。此外,我们计划在2021年年末开启7纳米时代,且7纳米的性能将会远超10纳米”。

英特尔的Cannon Lake处理器原计划在2016年下半年投入市场,后来延迟到2017年下半年,2018年又限量出货。我们所了解的唯一的Cannon Lake—“Core i5-8121U(没有内置GPU)”并没有投放到大众市场,且在2020年年初“静悄悄”地结束了生产。有观点认为:“在2017年下半年到2018年上半年期间,英特尔的10纳米一直波折不断,因此英特尔不得不对10纳米工艺进行大幅度地改造和重新设计。其证据是出货产品仅有一款SKU(Stock Keeping Unit)”。

英特尔的10纳米量产品—“Ice Lake”在2019年年中发售,如今在售的有11款、半定制(Semi-custom)SKU。Ice Lake的工作频率和TDP(Thermal Design Power)范围较广(9W~28W),这也证明了英特尔可以成功地生产在性能、功耗方面极具优势的10纳米芯片。为获得较高的性能、较高的良率,英特尔必须要使用10纳米工艺技术的改良版。

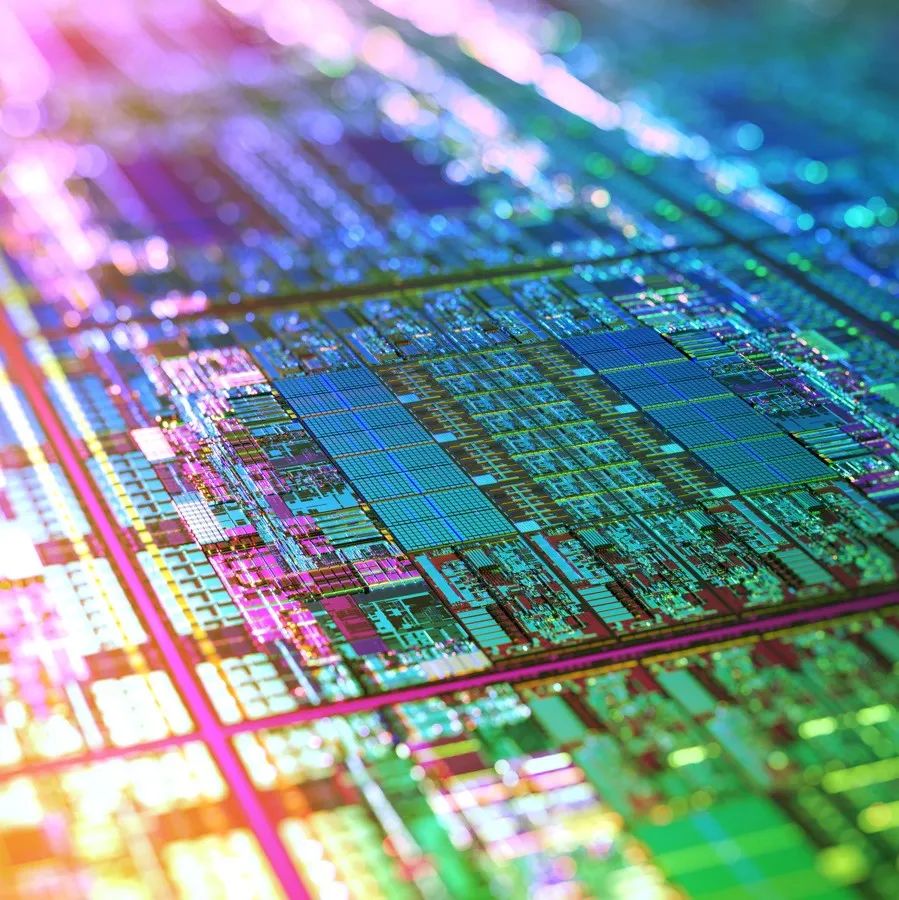

采用了10纳米的“Ice Lake”。(图片出自:eetimes)

与搭载了Cannon Lake的系统不同,搭载了Ice Lake的PC几乎被所有的厂家投放到了市场,因此,英特尔在2019年-2020年期间,改善了10纳米芯片的供给情况。

另一方面,英特尔将采用了14纳米的处理器技术--“Comet Lake”应用于主流的笔记本电脑、高性能的笔记本电脑、台式游戏机电脑。将14纳米++处理器应用于游戏机设备,这并不令人感到意外(希望读者注意的是为适应较高的时钟频率,英特尔优化了此项技术),从将Comet Lake应用于主流的笔记本电脑上和搭载了Ice Lake的笔记本电脑供应不足这两点,可以看出在2019年下半年、2020年上半年,英特尔的10纳米处理器的供应量可能不太充分。

继Ice Lake之后,英特尔又在“CES2020(美国拉斯维加斯)”上公布了“Tiger Lake”处理器,同时,英特尔还表示,会在下一个长假(Holiday Season)之前,向市场投放50多种搭载了“Tiger Lake”的电脑。

英特尔的10纳米产品正在一步步缓慢增多,除了CPU,还有以10纳米为基础的FPGA “Agilex”、5G方向的SoC“Atom P5900系列”等。Atom P5900已经获得三家通信设备厂家的设计方案(Design-win)。

但是,并非一切都是那么乐观。英特尔已经将采用了10纳米+的“Xeon(研发代码:Ice Lake)”处理器的出货时间从2020年上半年推迟至同年的下半年。这应该也会对英特尔的服务器方向的业务造成影响。虽然我们无从推测延迟的理由,但是不难想象如果缺陷密度较高的话,相对小型芯片,对大型芯片的影响较大。主流的笔记本电脑虽然可以“容许”10纳米+的缺陷密度、良率问题,但还达不到高端服务器的要求水准。

要理解英特尔10纳米芯片的生产量,需要理解英特尔能够处理多少数量的10纳米晶圆、有多少处工厂可以处理10纳米晶圆。最近,英特尔不太公布其产能相关的信息。但是,也并不是只字不提。英特尔曾公布说,美国的亚利桑那州、俄勒冈州和以色列工厂可以生产10纳米芯片。

英特尔在10纳米和Hyper Scaling(超级微缩)上下了一个大的赌注,10纳米产品量产的推迟、Ice Lake中的10纳米技术的调整,而且为了满足2018年-2019年期间处理器的需求,英特尔又花费了数十亿美元对14纳米进行扩产。

如今,很难说英特尔的10纳米战略获得了成果。此外,英特尔认为,在2020年之内,10纳米产品的出货数量很难超过14纳米。在2020年年初,其自身也承认10纳米的利润不如之前的其他工艺。

话虽如此,英特尔毕竟是拥有大批客户的巨头厂家,很难想象跳过10纳米而直接进入下一代节点技术,未来应该还会出现很多采用了10nm、10nm+、10nm++的产品。当然,我们也十分期待英特尔的采用了EUV光刻的7纳米技术。

★

点击文末【阅读原文】,可查看

本文原链接

。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2393期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

EUV|蓝牙

|

5G|高通|英伟达|FPGA|国产芯片|晶圆代工

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie

晶体管的性能、耗能。(图片出自:eetimes)

晶体管的性能、耗能。(图片出自:eetimes)