[原创] 两大FPGA巨头的AI技术路线浅析

2020-07-01

14:00:09

来源: 半导体行业观察

来源:内容来自「知乎」,作者:黄乐天,谢谢。

近日Intel发布了Stratix 10 NX FPGA,标志着Intel公司在FPGA领域的人工智能“落地计划”。而去年Xilinx发布了ACAP后大家就一直等待着Intel的对应动作,Intel在时隔半年多以后也在于有了响应。

同样是利用FPGA来实现人工智能算法,两家的技术路线上有什么区别呢?今天我们就有限的资料来加以解读一下。

计算篇一句话总结就是:做FPGA起家的已经不在单纯的做FPGA,而做处理器起家的还是想继续好好的做FPGA。

上面这句话如何解释,我们首先来看看Xilinx的ACAP里面都有什么:

可以看到如今的ACAP早已经脱离了FPGA的范畴,除了中间那灰色的方块还是传统的FPGA那套东西以外,剩下的都是各种其它器件。甚至可以半开玩笑半认真的说,ACAP“主要是在做处理器”。除了左侧的应用处理器和实时处理器以外,右边的HW/SW Programanle Engine其实也是处理器。只不过是一直“众核处理器阵列”。

可以看到如今的ACAP早已经脱离了FPGA的范畴,除了中间那灰色的方块还是传统的FPGA那套东西以外,剩下的都是各种其它器件。甚至可以半开玩笑半认真的说,ACAP“主要是在做处理器”。除了左侧的应用处理器和实时处理器以外,右边的HW/SW Programanle Engine其实也是处理器。只不过是一直“众核处理器阵列”。

把HW/SW Programanle Engine内部打开,其实是有很多“AI Core”组成的。这些AI Core采用的是自适应数据流的方式来组织多个核心。而Xilinx认为传统的多核是用层次化存储的方式来组织多个核心。当然这个不太全面,具体的可以阅读我以前写过的文章:

详说片上网络之二:片上多核系统的互联需求

把HW/SW Programanle Engine内部打开,其实是有很多“AI Core”组成的。这些AI Core采用的是自适应数据流的方式来组织多个核心。而Xilinx认为传统的多核是用层次化存储的方式来组织多个核心。当然这个不太全面,具体的可以阅读我以前写过的文章:

详说片上网络之二:片上多核系统的互联需求

这些AI Core其实就是后面ACAP承载AI等数据密集型运算的主体,Core和Core之间一数据流的方式直连。包括相邻互联和长距离互联两种:

图3 AI Core的相邻互联方式,直接在旁边AI Core的Memory取数据

图3 AI Core的相邻互联方式,直接在旁边AI Core的Memory取数据

这些互联方式组合就可以构成多种不同的互联方式,包括流水线、数据流图、广播等等。更多的细节就不再详细讨论了。总之,Xilinx的AI技术路线是做了一套专门的新的硬件体系来承载AI等新兴的数据密集型运算。

而Intel的思路完全不同,Intel应对AI计算的方式是“升级DSP模块”。

这些互联方式组合就可以构成多种不同的互联方式,包括流水线、数据流图、广播等等。更多的细节就不再详细讨论了。总之,Xilinx的AI技术路线是做了一套专门的新的硬件体系来承载AI等新兴的数据密集型运算。

而Intel的思路完全不同,Intel应对AI计算的方式是“升级DSP模块”。

我们知道,AI算法的核心就是大量的乘加/乘累加。再传统的FPGA中乘累加是依靠DSP模块实现的。为了追求较高的灵活性,普通的DSP模块就是一个或者两个乘法器,外加一个加法器构成。这样就可以基于这种基本的DSP模块配合FPGA的其它部分构成各种不同的运算算法。

但AI运算不是一般的乘加,而是一种“张量”运算。张量的概念大家可以具体去查询其它知乎上的回答和专栏。简单的说就是一组数据先乘后加,乘加之间还有级联。因此提升FPGA执行AI算法的最好方法自然就是把DSP模块升级为更加适应AI张量运算的模块。就是下面这张。

我们知道,AI算法的核心就是大量的乘加/乘累加。再传统的FPGA中乘累加是依靠DSP模块实现的。为了追求较高的灵活性,普通的DSP模块就是一个或者两个乘法器,外加一个加法器构成。这样就可以基于这种基本的DSP模块配合FPGA的其它部分构成各种不同的运算算法。

但AI运算不是一般的乘加,而是一种“张量”运算。张量的概念大家可以具体去查询其它知乎上的回答和专栏。简单的说就是一组数据先乘后加,乘加之间还有级联。因此提升FPGA执行AI算法的最好方法自然就是把DSP模块升级为更加适应AI张量运算的模块。就是下面这张。

图6这张清晰度一般的图可以让我们简单的一窥AI张量运算模块的内部结构。可以看到是大量的乘法器,不同模块之间的级联通道,以及对应的加法。这非常符合张量运算先乘后加,多维运算的运算过程。这样让底层运算结构与算法高度匹配,就可以保证算法的执行效率。

综上所述,可以很清楚的明白:Xilinx的计算路线,是依靠独立的AI Core阵列,用类似于阵列处理器的方式来实现的。这种模式独立于传统的FPGA结构之外,是一个独立的硬件组成单元。而Intel则选择了将嵌入在FPGA内部的DSP模块直接升级乘了AI张量模块,依然是FPGA内部的组成模块之一。

图6这张清晰度一般的图可以让我们简单的一窥AI张量运算模块的内部结构。可以看到是大量的乘法器,不同模块之间的级联通道,以及对应的加法。这非常符合张量运算先乘后加,多维运算的运算过程。这样让底层运算结构与算法高度匹配,就可以保证算法的执行效率。

综上所述,可以很清楚的明白:Xilinx的计算路线,是依靠独立的AI Core阵列,用类似于阵列处理器的方式来实现的。这种模式独立于传统的FPGA结构之外,是一个独立的硬件组成单元。而Intel则选择了将嵌入在FPGA内部的DSP模块直接升级乘了AI张量模块,依然是FPGA内部的组成模块之一。

要高效的执行AI算法,让底层的运算器件更为符合算法特征只是做了一半,甚至只是一小半工作。局座张将军经常讲一句名言:“外行谈战略,内行谈后勤”(貌似已经沦为“公知”的袁老师也经常喜欢引用)。我这里也暂时借用一下:“外行看计算,内行看存储”。对于算法加速,很多时候取决于存储的数据能否及时的被“送”到运算单元中,从而能保证运算单元可以满负荷运转。在这里Xilinx和Intel也采取了不同的策略,Intel“求诸于外”而Xilinx“反求诸于内”。

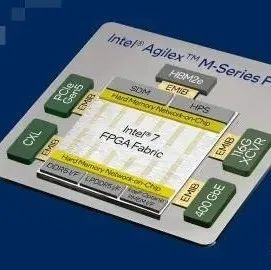

图7给出了Stratix 10NX FPGA的封装结构,很显然的突出了Intel的Chiplet方案。依靠EMIB的接口方式,把HBM(High Bandwidth Memory)直接和FPGA内核连接在一起,从而形成了一块较大容量的“近计算内存”。从而极大的提升了存储器到FPGA的访存延迟。简单、粗暴,但是有效。谁让Intel掌握了EMIB这样的前沿科技呢。

而Xilinx的ACAP中则祭出了另外一个“法宝”:片上网络(NoC)。

图7给出了Stratix 10NX FPGA的封装结构,很显然的突出了Intel的Chiplet方案。依靠EMIB的接口方式,把HBM(High Bandwidth Memory)直接和FPGA内核连接在一起,从而形成了一块较大容量的“近计算内存”。从而极大的提升了存储器到FPGA的访存延迟。简单、粗暴,但是有效。谁让Intel掌握了EMIB这样的前沿科技呢。

而Xilinx的ACAP中则祭出了另外一个“法宝”:片上网络(NoC)。

可以看到ACAP内部各个大的硬件结构之间是依靠NoC互联的,而在AI Core阵列的入口处依靠DMA可以通过NoC直接访问外部的DRAM。这是避免了低效的“可编程互联”结构,用片上网络的高带宽直接把数据送到AI Core阵列的入口,然后用流传输的方式直接送到AI Core内部的Memory来处理。这种方法是在优化芯片内部的传输能力。

值得一提的是,Altera比Xilinx更早的尝试在FPGA内部使用NoC来互联各个可编程模块。2014年我在KTH苦苦研究片上网络之时,读到多伦多大学发表的NoC-FPGA的论文。那论文里的配图风格和Altera的数据手册配图如出一辙。当时坐我旁边的一个哥们儿(华人,复旦大学本硕毕业,KTH去读的博士)去Xilinx实习以后回来谈到这个问题,说Xilinx保守,对于FPGA中嵌入NoC比较保留。然而时过境迁,没想到今天的Intel FPGA中仍然没有看到对于硬核实现的NoC的介绍(软核的早已实现),但在Xilinx的ACAP中是明确的看到了。

综上所述,Intel FPGA依靠着自家已经高度成熟的EMIB技术,走Chiplet的道路,优化存储器到FPGA之间的Die-2-Die传输效率。而Xilinx则通过NoC来优化片内传输效率,减少数据在芯片内部的传输时间。

以上是本人根据接触到的资料对于Xilinx和Intel的FPGA实现AI运算的技术路线的一点解读。由于水平和资料都有限,难免出现纰漏,如果有更多消息的知友们可以补充。如果觉得留言不过瘾的,可以开个贴专门再讲。

最后的最后,在啰唆几句纯粹是猜测的话。Xilinx和Intel之所以出现这两种不同的技术路线,很大程度是取决于他们背后的技术储备和对于FPGA的定位。对于Intel而言,它旗下有CPU、GPU(开发中)、Movidius VPU、FPGA等多种面向不同场景的人工智能计算平台。所以在Intel这里,“FPGA就是FPGA”,只不过是一种实现AI算法的途径而已。而在Xilinx这里,FPGA就是它的全部。为了适应更大的市场,Xilinx需要“FPGA不止是FPGA”。所以就诞生了ACAP这样“超越了FPGA”的新型器件。

最后一段话纯粹是个人胡诌,再次声明,各位就当看个乐。

电子科技大学电子科学与工程学院,副教授, 电子科技大学博士。主要研究方向为计算机系统架构与系统级芯片设计,已在IEEE Transactions on Computers (CCF A 类期刊)等高水平期刊和CODE+ISSS、FCCM、ASPDAC、ISCAS等顶级会议上发表高水平论文50 余篇,申请专利11项,出版学术著作1部。参加工作以来主持和参与过国家自然科学基金项目重点项目、装备预研重点项目、国家科技重大专项、国家“863”重点研究计划等国家级重点科研项目,曾荣获Altera公司(Intel PSG)金牌培训师、 第七、第八、第十二届研究生电子设计大赛优秀指导教师、电子科大网络名师等称号。先后担任过国际会议ICICM 2016年Publicity Chair,IEEE CEDA Chengdu Chapter Chair 、ISOCC 2016年Session Co-Chair、APCCAS2018 Special Session Chair等学术职务。

可以看到ACAP内部各个大的硬件结构之间是依靠NoC互联的,而在AI Core阵列的入口处依靠DMA可以通过NoC直接访问外部的DRAM。这是避免了低效的“可编程互联”结构,用片上网络的高带宽直接把数据送到AI Core阵列的入口,然后用流传输的方式直接送到AI Core内部的Memory来处理。这种方法是在优化芯片内部的传输能力。

值得一提的是,Altera比Xilinx更早的尝试在FPGA内部使用NoC来互联各个可编程模块。2014年我在KTH苦苦研究片上网络之时,读到多伦多大学发表的NoC-FPGA的论文。那论文里的配图风格和Altera的数据手册配图如出一辙。当时坐我旁边的一个哥们儿(华人,复旦大学本硕毕业,KTH去读的博士)去Xilinx实习以后回来谈到这个问题,说Xilinx保守,对于FPGA中嵌入NoC比较保留。然而时过境迁,没想到今天的Intel FPGA中仍然没有看到对于硬核实现的NoC的介绍(软核的早已实现),但在Xilinx的ACAP中是明确的看到了。

综上所述,Intel FPGA依靠着自家已经高度成熟的EMIB技术,走Chiplet的道路,优化存储器到FPGA之间的Die-2-Die传输效率。而Xilinx则通过NoC来优化片内传输效率,减少数据在芯片内部的传输时间。

以上是本人根据接触到的资料对于Xilinx和Intel的FPGA实现AI运算的技术路线的一点解读。由于水平和资料都有限,难免出现纰漏,如果有更多消息的知友们可以补充。如果觉得留言不过瘾的,可以开个贴专门再讲。

最后的最后,在啰唆几句纯粹是猜测的话。Xilinx和Intel之所以出现这两种不同的技术路线,很大程度是取决于他们背后的技术储备和对于FPGA的定位。对于Intel而言,它旗下有CPU、GPU(开发中)、Movidius VPU、FPGA等多种面向不同场景的人工智能计算平台。所以在Intel这里,“FPGA就是FPGA”,只不过是一种实现AI算法的途径而已。而在Xilinx这里,FPGA就是它的全部。为了适应更大的市场,Xilinx需要“FPGA不止是FPGA”。所以就诞生了ACAP这样“超越了FPGA”的新型器件。

最后一段话纯粹是个人胡诌,再次声明,各位就当看个乐。

电子科技大学电子科学与工程学院,副教授, 电子科技大学博士。主要研究方向为计算机系统架构与系统级芯片设计,已在IEEE Transactions on Computers (CCF A 类期刊)等高水平期刊和CODE+ISSS、FCCM、ASPDAC、ISCAS等顶级会议上发表高水平论文50 余篇,申请专利11项,出版学术著作1部。参加工作以来主持和参与过国家自然科学基金项目重点项目、装备预研重点项目、国家科技重大专项、国家“863”重点研究计划等国家级重点科研项目,曾荣获Altera公司(Intel PSG)金牌培训师、 第七、第八、第十二届研究生电子设计大赛优秀指导教师、电子科大网络名师等称号。先后担任过国际会议ICICM 2016年Publicity Chair,IEEE CEDA Chengdu Chapter Chair 、ISOCC 2016年Session Co-Chair、APCCAS2018 Special Session Chair等学术职务。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2357期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

英特尔|汽车芯片|

CMOS

|晶圆

|

AI

|苹果

|IPM|滤波器|射频

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie