来源:内容由半导体行业观察(ID:icbank)编译自「

allaboutcircuit

」,谢谢。

在消费者需求的驱动下,电气和设计工程师一直在努力寻找在保持高性能和效率水平的同时,制造更小,更轻,更智能的设备的方法。然而,使电子设备更小是有代价的。由于超紧凑型半导体中的量子效应,场效应晶体管(FET)停止以易于控制的方式运行,这就是诸如FinFET之类的器件架构发挥作用的地方,使工程师能够继续按比例缩小器件尺寸。

但是,这些创新性的仍然具很快将要达到其极限,这不可避免地促使工程师继续在这一领域进行创新。

现在,新加坡科技大学的一组研究人员报告说 ,他们发现了一种解决2D半导体中出现的接触电阻问题的新策略,这一挑战使他们的发展和应用受到了阻碍。

厚度仅为几个原子的二维(2D)半导体已被认为是下一代超紧凑计算电子产品的潜在选择。这是因为它们有助于将电气开关选项制成FET,而无需使用复杂的设备架构即可有效地控制这些选项。

当由2D半导体制成晶体管时,需要通过“源极”和“漏极”这两个金属薄片进行电接触。然而,这些会在源极和漏极两者上产生接触电阻,这会降低晶体管的性能,并产生大量的热量浪费能量,从而使其效率低下。

鉴于工程师的目标是使设备更小同时保持性能和效率,因此很容易理解为什么2D半导体尚未在实际应用中得到利用。迄今为止,正在寻找不会产生大的接触电阻的合适的金属。

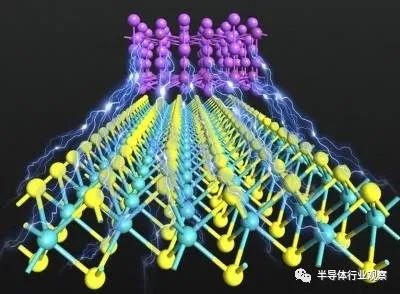

拓扑半金属电接触和导致2D半导体晶体管能效提高的反应的图形表示。图片由新加坡科技设计大学提供

但是,据《应用物理评论》报道,新加坡研究小组声称找到了解决接触电阻问题的方法。通过执行最新的密度泛函理论(DFT)计算仿真,研究小组观察到,可以使用最近发现的拓扑半金属Na3Bi的超薄膜,其具有受晶体对称性保护的导电特性。具有超低接触电阻的2D半导体金属触点。所谓超薄,是指两个原子层较薄。

“我们发现,Na3Bi和2D半导体之间形成的肖特基势垒( Schottky barrier)高度是该行业常用的许多金属中最低的高度之一,”新加坡研究团队的Yee Sin Ang博士说。

肖特基势垒是在金属和半导体之间形成的薄绝缘体。该势垒的高度对所观察到的接触电阻的水平有很大的影响,对于低电阻而言,期望小的高度。

通过发现Na3Bi与两种常用的2D半导体MoS2和WS2之间的肖特基势垒远低于许多常用金属,研究小组发现了拓扑半金属薄膜的强度及其在设计高效的2D半导体器件方面的巨大潜力,因为这些设计拥有最小的接触电阻。

当2D半导体与接触的金属熔合在一起时,它们会被金属化并失去其最初的电气特性,这对于电子应用而言是理想的。

但是,研究小组发现Na3Bi不会使2D半导体金属化,因此将其用作2D半导体的金属触点对于晶体管和太阳能电池等应用非常有利。

“我们将2D材料和拓扑材料协同作用的开创性概念将为设计节能电子设备提供一条新途径,这对于减少诸如物联网和人工智能等高级计算系统的能源足迹特别重要。” ,该团队的首席研究员Ricky LK Ang总结道。

★

点击文末【阅读原文】,可查看

本文原链接

。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2336期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

两会|台积电|

RISC-V

|汽车芯片

|

AI

|EDA

|中美|晶圆|射频|

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!