一文看懂台积电的研发实力

2020-05-26

16:07:41

来源: Sophie

来源:内容来自「

台积电财报

」,谢谢。

在一个月的文章

《这才是台积电的真正实力》

中,我们对台积电公司的实力做了一个概述。今天,我们从台积电去年底的研发投入和成果,看清这家晶圆代工巨头的真正技术实力。

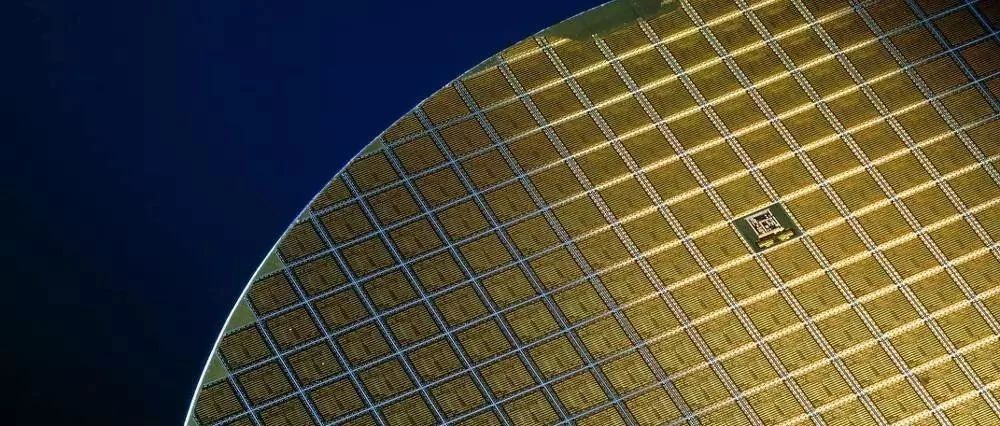

2019年,台积公司持续投资研究与开发,全年研发总预算约占总营收之 8.5%,此一研发投资规模相当于或超越了许多其他高科技领导公司的规模。延续每二年半导体运算能力增加一倍之摩尔定律所面临的技术挑战日益困难,台积公司研发组织的努力着重于让台积公司能够提供客户率先上市且先进的技术和设计解决方案,帮助客户取得产品的成功。

2019年,随着 7 纳米强效版技术的量产,以及 5 纳米技术成功试产,公司的研发组织持续推动技术创新以维持业界的领导地位。当台积公司采用三维晶体管之第六代技术平台的 3 纳米技术持续全面开发时,公司已开始开发领先半导体业界的 2 纳米技术,同时针对 2 纳米以下的技术进行探索性研究。

除了发展互补金属氧化物半导体逻辑技术,台积公司广泛的对其他半导体技术进行研发,以提供客户行动系统单芯片(SoC)及其他应用所需的功能。

● 创新的晶圆级封装技术ー系统整合芯片 TSMC-SoIC®ー的制程认证;

● 大量生产第四代整合型扇出层叠封装技术(InFOPoP)以支援行动处理器封装;

● 成功验证第五代整合型扇出层叠先进封装技术以支援行动应用,与第二代整合型扇出暨基板封装,以支援高效能运算(HPC)应用;

● 开发业界独特的 40 纳米 BCD(Bipolar-CMOSDMOS)技术,提供先进的 20-24 伏高压元件并与40 纳米超低功耗平台完全兼容,以及整合了可变电阻式存储器(RRAM),支援行动应用所需的低功耗、高整合度、以及小布局面积的高速通讯界面;

● 28 纳米嵌入式快闪存储器支援高效能行动运算与高效能低漏电制程平台,达成了车用电子及微控制器单元(MCU)的技术验证;

● 完成开发最新一代次微米像素传感器以支援行动应用,并开发嵌入式三维金属 - 介电质 - 金属(MiM)高密度电容,支援全域快门与高动态范围传感器之应用。

2019年,台积公司致力于维系与许多世界级研究机构的强力合作关系,包括美国的 SRC 及比利时的 IMEC。台积公司亦持续扩大与世界顶尖大学的研究合作,达到半导体技术进步及培育未来人才的二大目标。

虽然半导体产业逼近硅晶之物理极限,5 纳米制程仍遵循摩尔定律,显著地提高芯片密度,在相同的功耗下提供更好的效能,或在相同的效能下提供更低的功耗。2019年,台积公司持续进行 5 纳米制程之全面开发,专注于基础制程制定、良率提升、晶体管及导线效能善,以及可靠性评估。静态随机存取(SRAM)记忆体及逻辑电路之良率均符合预期,台积公司已达成2019年进入试产的目标。

相较于 5 纳米制程技术,3 纳米制程技术大幅提升芯片密度及降低功耗并维持相同的芯片效能。2019年的研发着重于基础制程制定、良率提升、晶体管及导线效能改善以及可靠性评估。2020年,台积公司将持续进行 3 纳米制程技术的全面开发。

2019年,台积公司领先半导体产业进行 2 纳米制程技术的研发。

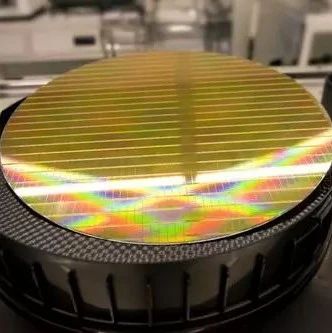

2019年微影技术研发的重点在于 5 纳米的技术转移、3 纳米技术的开发及 2 纳米以下技术开发的先期准备。5 纳米技术已经顺利地移转,研发单位与晶圆厂合作排除极紫外光微影量产问题。针对 3 纳米技术的开发,极紫外光(EUV)微影技术展现优异的光学能力,

与符合预期的芯片良率。

研发单位正致力于极紫外光技术,以减少曝光机光罩缺陷及制程堆栈误差,并降低整体成本。

2020年,台积公司在 2 纳米及更先进制程上将着重于改善极紫外光技术的质量与成本。

2019年,公司的极紫外光项目在光源功率及稳定度上有持续性的进展,光源功率的稳定与改善得以加快先进技术的学习速度与制程开发。此外,极紫外光光阻制程、光罩保护膜及相关的光罩基板也都展现显著的进步,极紫外光技术正逐步迈向全面生产制造就绪。

光罩技术是先进微影技术中极为重要的一环。2019年,研发组织成功地完成 5 纳米制程光罩技术的转移,并在 3 纳米技术顺利导入更复杂且先进的极紫外光的光罩技术,生产良率、周期时间及基板缺陷亦有实质进展,以符合大量生产的要求。

台积公司在导线互连间距密度和系统尺寸上持续升级晶圆级系统整合技术(WLSI),推动系统性能向前演进超越了摩尔定律。WLSI 利用前段三维(3D)整合,系统整合芯片(TSMC-SoIC®)和后段三维整合而开发出创新技术,包括整合型扇出(InFO)和 CoWoS® 技术。台积公司拥有最先进制程的晶圆/芯片,以及混合匹配的前段三维和后段三维系统整合,客户可以利用台积公司独特的从晶圆到封装的整合式服务来打造具差异化的

产品。

● 三维集成电路(3D IC)与系统整合芯片(TSMCSoIC®)

系统整合芯片(TSMC-SoIC®)是一种创新的晶圆级封装技术,将多个小芯片(Chiplet)整合成一个面积更小与轮廓更薄的系统单芯片,透过此项技术,7 纳米、5纳米甚至 3 纳米的先进系统单芯片能够与多阶层、多功能芯片整合,可实现高速、高频宽、低功耗、高间距密度、最小占用空间的异质三维集成电路。有别于传统的封装技术,TSMC-SoIC® 是以关键的铜到铜接合结构,搭配硅导孔(Through-Silicon-Via, TSV)以实现最先进

的 3D IC 技术。

目前台积公司已完成 TSMC-SoIC® 制程认证,开发出微米级接合间距(bonding pitch)制程,并获得极高的电性良率与可靠度数据,展现了台积公司已准备就绪,具备为任何潜在客户用 TSMC-SoIC® 生产的能力。

简言之,TSMC-SoIC® 技术不仅提供延续摩尔定律的机会,并且在系统单芯片效能上取得显著的突破。

● 硅中介层(Si Interposer)与 CoWoS®

2019年,由于高效能运算(HPC)与人工智能(AI)市场的快速成长,CoWoS® 需求持续强劲,该产品类别的独特要求包括将具有最高运算能力的逻辑芯片与具有最大容量和频宽的存储器芯片整合在一起,而这正是 CoWoS® 的优势所在。为了满足持续增加的生产需求,先进后段晶圆厂 AP3 和 AP5 与最初的 CoWoS®晶圆厂 AP1 合力提供客户所需的 CoWoS® 产能。

在技术方面,第四代 CoWoS® 藉由扩大硅中介层的尺寸而进一步提高封装整体性能,中介层面积高达 1,700 平方毫米,其大小足以容纳一个全光罩(full-reticle)尺寸的系统单芯片和多达六个三维(3D)高频宽存储器(HBM)的堆栈。正在开发的第五代 CoWoS® 的中介层面积高达 2,400 平方毫米,并同时考虑了新的芯片架构,例如小芯片、系统整合芯片、以及第三代高频宽记忆体(HBM3)。

2019年,台积公司持续领先全球大量生产第四代整合型扇出层叠封装技术(InFO-PoP Gen-4)以支援行动应用处理器与整合型扇出暨基板封装技术(InFO_oS)高效能运算(HPC)晶粒分割的应用。第五代InFO-PoP 和第二代 InFO_oS 也分别通过了认证,支援行动应用和高效能运算应用。根据第五代 InFO-PoP 认证,此技术可以具有更小的封装尺寸,更多的接脚数和更好的电源完整性(power integrity)。

第二代 InFO_oS 提供了更多的晶粒分割整合于更大的封装尺寸和更高的频宽上。持续开发具有更细间距晶粒到晶粒互连的多晶粒异质整合成就了无基板的崭新整合型扇出技术,支

援消费性应用。

新世代整合式被动元件技术(Integrated Passive Device, IPD)提供高密度电容器和低有效串联电感(Effective Series Inductance, ESL)以增强电性,并已通过 InFO-PoP 认证。

AI 与 5G 行动应用将受惠于强化的 InFO-PoP 技术,新世代 IPD 预计于2020开始进入大量生产。

为了强化客户的竞争力,台积公司透过导线技术架构的创新与新材料的开发,提供先进导线技术以提升芯片效能。创新的电力分布网络(PDN)方案在于减低传统作法上的高压降与电阻电容延迟,并利用更好的布线资源来改善线路密度。新材料包括金属与介电质材料,开发着重于结实的低介电材料与较低等效电容结构。

除了金属阻绝层的开发之外,台积公司亦研发单金属元素、双元与三元合金。先进技术研究晶体管结构及材料的创新持续提升先进逻辑技术的效能并降低功耗。台积公司在二维材料及纳米碳管晶体管的研究一直走在业界前端。

2019年,台积公司在超大型集成电路技术研讨会(Symposia on VLSI Technology, VLSI)发表了使用有区域选择的通道化学气相沉积技术成长在二氧化硅 / 硅基板上的 40 纳米通

道长度上方闸极二硫化钨 p 通道场效晶体管的首次展示。

没有使用二维材料层转移,此直接化学气相沉积技术更适合量产。

台积公司也在2019年举行的国际电子元件会议(International Electron Device Meeting, IEDM)成功率先展示使用后段制程兼容的低温低成本和高迁移率的后段制程纳米碳管晶体管在先进的 28 纳米硅逻辑电路上进行异质整合。台积公司持续寻找支援人工智能和高效能运算的新兴高密度、非挥发性存储器硬件加速器。台积公司的先进技术研究可望为持续密度微缩、提升效能、降低功耗铺路,提供先进逻辑技术以支援行动与高效能运算应用。

台积公司提供多样化的新制程技术以协助客户广泛解决各类产品的应用:

2019年,台积公司成功开发以 5 纳米硅及电磁模拟为基础的 LC 振荡器设计解决方案,满足高速SerDes 电路设计的需求,藉由不同金属层组合及特定布局来缩短设计周期。为了满足客户对于 5G 网络蓝图之高速、低延迟、以及大量物联网应用的需求成长,台积公司提供 16 纳米及 28 纳米射频元件,透过提升截止频率与最大震荡频率以支援射频收发器设计,以及 40 纳米特殊制程强化崩溃电压,在来自导通电阻与断电容的乘积降低的相同效益下,支援射频切换器设计的应用。

● 电源 IC /双极—互补金属氧化半导体—双重扩散金属氧化半导体(BCD)

2019年,台积公司透过 40 纳米超低功耗平台开发出 20-24 伏高压元件的 40 纳米 BCD 技术,与低压元件和逻辑制程完全兼容,并首次成功整合可变电阻式存储器,在小布局面积提供低功耗、高整合度,支援行动应用装置的高速通讯界面,台积公司将持续开发 28 伏及 12-16 伏高压元件以涵盖更多的电源管理芯片应用。

2019年,台积公司完成双平台先进高压显示驱动器 IC 技术。晶圆堆栈(WoW 28HPC / 40HV)和28HV 技术通过制程及可靠性认证,晶圆堆栈技术也已经完成了客户的产品良率和认证,相较于 40HV,其主动功耗降低 60%。

多家客户已完成 28HV 技术之早期IP 验证。这些技术是支援小尺寸面板 4K 分辨率、有机发光二极管(OLED)和 120Hz 显示驱动 IC 的先进技术。

此外,支援 AR / VR 应用的硅基 OLED 在 80HV 技术上展现出优异的亮度均匀度。2020年,台积公司计划提升 28HV OLED 触控显示整合(TDDI)应用以及晶圆堆栈 8 伏晶体管的效能。

2019年,台积公司完成模块化微机电系统(Modular MEMS)技术的验证,以大量生产高解析度加速度计与陀螺仪。未来计划包含开发下一世代高敏感度薄型麦克风、十二吋晶圆微机电光学影像稳定(Optical Image Stabilization, OIS)系统解决方案、以及生物微机电应用。

2019年,第一代 650 伏和 100 伏增强型高电子移动率晶体管(E-HEMT)投入生产,第二代 650 伏 和 100 伏 E-HEMT 之质量因素(FOM)较第一代改善50%,并且通过工程验证。此外,台积公司完成 100V D-HEMT 元件的开发,已通过工程验证,预计于2020年进入试产。

2019年,台积公司在互补式金属氧化物半导体影像传感器技术获得数项进展。两项主要成果:完成开发最新一代微缩化次微米像素传感器,其像素尺寸较前一代减少 12.5%,并提高画素读取速度,降低读取杂讯,以支援行动应用;并成功开发三维金属 - 介电质 -

金属(MiM)高密度电容,内嵌影像传感器阵列支援全域式快门与高动态范围传感器之应用

。

2019年台积公司在嵌入式非挥发性存储器技术领域达成数项重要的里程碑。在 40 纳米制程方面,公司已成功量产分离闸(Split-Gate)反或闸式(NOR)技术,支援消费性电子产品的应用,例如物联网、智慧卡和微控制器单元(MCU),也支援各种车用电子产品的应用。在 28 纳米制程方面,公司的嵌入式快闪存储器开发支援高效能行动运算与高效能低漏电制程平台已完成

技术验证,以因应车用电子及微控制器的应用。台积公司并提供嵌入于非挥发性存储器之电阻存储器技术,作为低成本解决方案,支援对价格敏感的物联网市场。40纳米已完成技术验证,客户产品验证持续进行,28 纳米预计于2020年进入量产,22 纳米的开发符合进

度,预计于2020年完成技术验证。

台积公司也正在开发 22 纳米嵌入式磁阻式随机存取存储器,并已成功完成技术验证进入量产,此外,台积公司致力于 16纳米嵌入式磁阻式随机存取存储器的开发,以支援下一世代嵌入式存储器 MCU、车用电子元件、物联网、以及

人工智能等多项新应用。

台积公司提供客户具备完整设计基础架构的先进技术平台,以达成令人满意的生产力及生产周期,其中包括:电子设计自动化(EDA)设计流程、通过硅芯片验证的元件数据库及硅智财(IP)、以及模拟与验证用的设计套件,例如制程设计套件(PDK)及技术档案。

针对台积公司最先进的 5 纳米、6 纳米、7 纳米、7纳米强效版、12 纳米、22 纳米及 3D IC 技术设计实现平台,所需要的电子设计自动化工具、功能及硅智财解决方案都已经准备就绪来让客户采用以满足产品在不同设计阶段上的需求。

此外,台积公司扩展其硅智财质量管理项目(TSMC 9000),使得硅智财稽核得以在台积

公司或其外部认证的实验室进行。

为了能够结合台积公司开放创新平台生态系统的硅智财以协助客户规划新的产品设计定案,开放创新平台生态系统提供一个入口网站,连结客户至一个拥有 42 个解决方案提供者的生态系统。

总体而言,台积公司与硅智财伙伴们从 0.35 微米到 5 纳米所累积的硅智财组合超过 2 万 6,000 个,满足了客户设计的需求。台积公司与电子设计自动化伙伴从 0.13 微米到 5 纳米打造许多的电子设计自动化解决方案,成功地支援客户设计定案。

台积公司的技术平台提供了坚实的基础,协助客户实现设计,客户得以透过台积公司内部开发的硅智财与工具,或其 OIP 伙伴拥有的硅智财与工具进行芯片设计。

电子设计自动化工具的验证是奠定硅智财和客户设计的基础,以确保它们都符合台积公司制造技术上的需求,而验证的结果可于 TSMC-OnlineTM 取得。这些验证工具都有相对应的技术档案及制程设计套件(PDK)提供给客户下载来使用。从 0.5 微米到 5 纳米制程,台积公司提供广泛的制程设计套件,支援数位逻辑、混合讯号、射频(RF)、高压驱动器、CMOS 影像传感器(CIS)、以及嵌入式快闪技术等应用领域。除此之外,台积公司提供技术档案:设计法则检查(Design Rule Check)、布 局 与 电 路 比 较(Layout Versus Schematic)、 寄生元件参数萃取(RC Extraction)、自动布局与绕线

(Place-and-Route)及布局编辑器(Layout Editor)以确保电子自动化工具支援其制程技术。

截至2019年,台积公司已在 TSMC-OnlineTM 上提供客户超过1 万 600 个不同的技术档案及 360 个制程设计套件。每年客户下载使用技术档案与制程设计套件已超过 10 万次。

硅智财是集成电路设计所需要的基本元件,台积公司和生态伙伴针对客户不同的设计应用需求提供了不同种类的硅智财,包括了基础硅智财,类比硅智财,崁入式记忆硅智财,界面硅智财和软智财,为了支援 3D IC 客户的需求,台积公司也于2019年开始提供 3D IC

硅智财。

台积公司与其设计联盟合作伙伴为客户提供了丰富的可重复利用硅智财,对许多电路设计来说,这些硅智财是不可或缺的基本元件。

2019年,台积公司扩增其元件数据库与硅智财内容,使其总数超过 2 万 6,000 个,较2018年成长 30%。

参考设计流程是建立在经过验证的电子设计自动化工具上,提供客户额外所需的设计流程方法上的创新来帮助提高生产力。2019年,台积公司透过开放创新平台的合作,克服了关键的设计挑战,针对数位及系统单芯片应用所需的创新 6 纳米及 3D IC 技术发表了完整的参考流程,为了达到效能、功耗与面积的最佳化目的,提供 FinFET 和 TSMC-SoIC® 设计解决方案及设计方法。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2321期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

两会|台积电|

RISC-V

|汽车芯片

|

AI

|EDA

|中美|晶圆|射频|

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie