来源:内容来自公众号

「

白山头讲IC

」

,作者:白山头,谢谢。

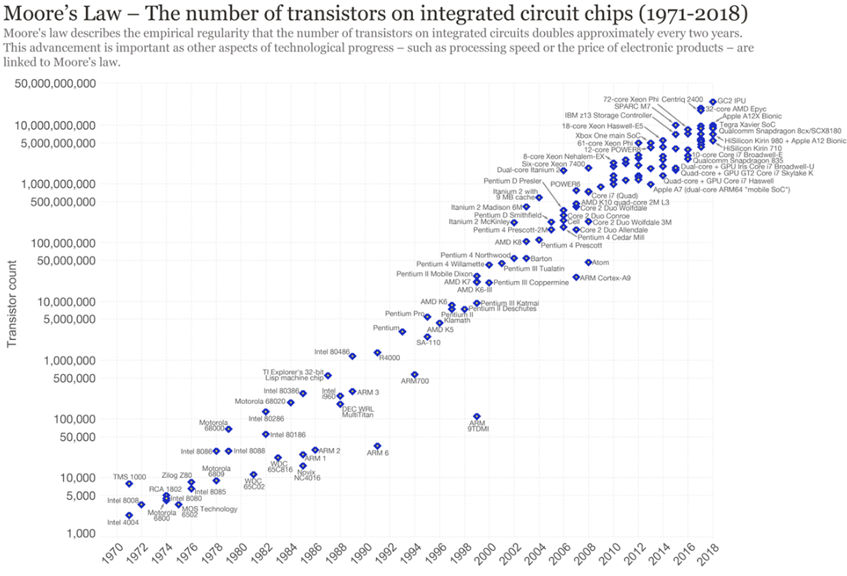

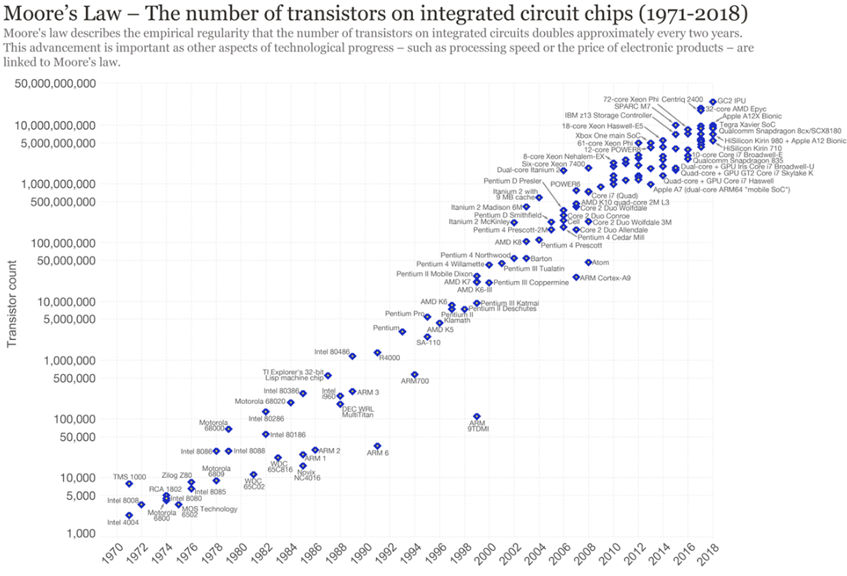

摩尔定律(Moore's law)是由英特尔创始人之一戈登·摩尔提出的。其内容为:集成电路上可容纳的晶体管数目,约每隔两年便会增加一倍;经常被引用的“18个月”,是由英特尔首席执行官大卫·豪斯(David House)提出:预计18个月会将芯片的性能提高一倍(即更多的晶体管使其更快),是一种以倍数增长的观测。

摩尔定律,是在观察基础上,对趋势的一个总结,同时也是对未来的展望。从摩尔定律提出,至今,已经有几十年的时间。期间,不断的有摩尔定律终结的传言,然而,这些传言却不断被打破。

摩尔定律,终有一天会终结,但是所有人都希望这一天来的越晚越好。

我们从另外一个角度来看,就可以明白,摩尔定律的延续能给我们带来的好处。

摩尔定律,是在观察基础上,对趋势的一个总结,同时也是对未来的展望。从摩尔定律提出,至今,已经有几十年的时间。期间,不断的有摩尔定律终结的传言,然而,这些传言却不断被打破。

摩尔定律,终有一天会终结,但是所有人都希望这一天来的越晚越好。

我们从另外一个角度来看,就可以明白,摩尔定律的延续能给我们带来的好处。

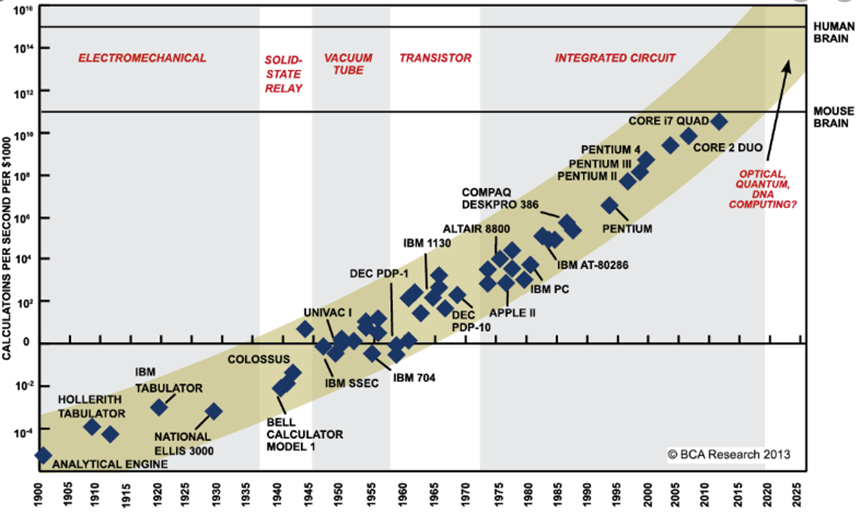

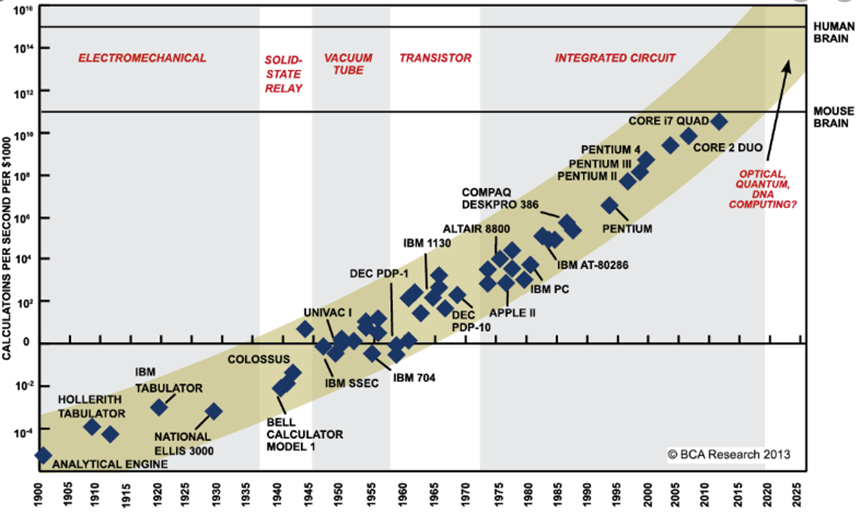

上图是每1000美元,所能买到的计算能力。相信不久之后,仅仅花1000美元,我们就可以买到与人类大脑计算能力相当的电子产品。

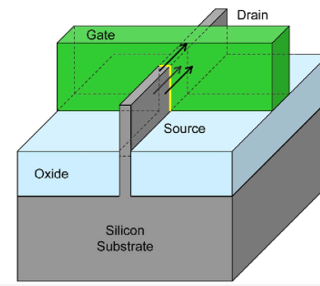

为了让摩尔定律延续到更小的器件尺度,学术界和工业界在不同的材料、器件结构和工作原理方面的探索一直在进行中。探索的问题之一是晶体管的闸极设计。随着器件尺寸越来越小,能否有效的控制晶体管中的电流变得越来越重要。

本文将尝试就小小的晶体管闸极的角度,来见证半导体人是如何不断实现着摩尔当年所吹下的牛逼,使得摩尔定律不断延续传奇。

上图是每1000美元,所能买到的计算能力。相信不久之后,仅仅花1000美元,我们就可以买到与人类大脑计算能力相当的电子产品。

为了让摩尔定律延续到更小的器件尺度,学术界和工业界在不同的材料、器件结构和工作原理方面的探索一直在进行中。探索的问题之一是晶体管的闸极设计。随着器件尺寸越来越小,能否有效的控制晶体管中的电流变得越来越重要。

本文将尝试就小小的晶体管闸极的角度,来见证半导体人是如何不断实现着摩尔当年所吹下的牛逼,使得摩尔定律不断延续传奇。

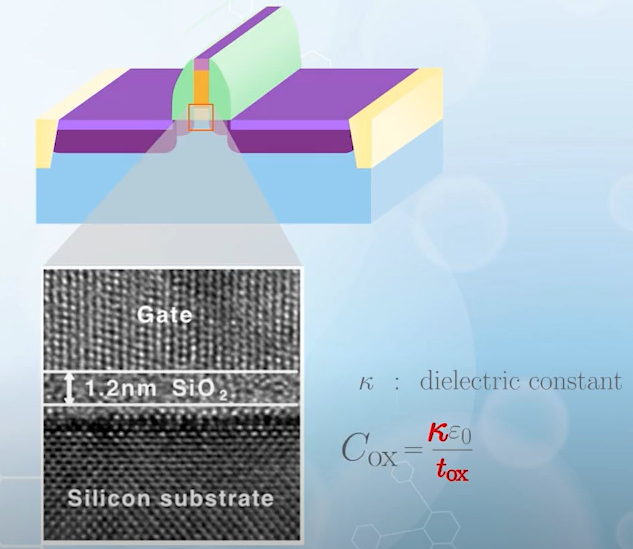

high-k电介质材料的引入(high-k dielectric material)

从亚微米工艺, 到后来的90nm工艺所代表的深亚微米时代,业内一直按照摩尔定律,稳步的发展。

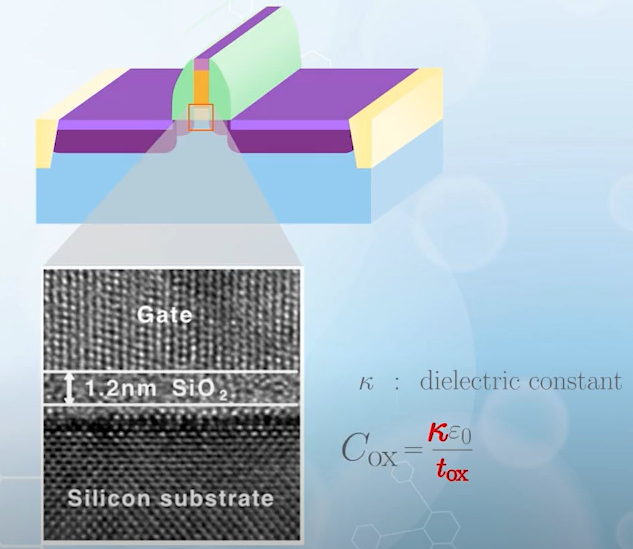

在65nm工艺的晶体管中的二氧化硅层已经缩小仅有5个氧原子的厚度了。作为阻隔栅极和下层的绝缘体,二氧化硅层已经不能再进一步缩小了,否则产生的漏电流会让晶体管无法正常工作。

为什么这层二氧化硅需要越来越薄,其实就是为了增大gate与闸极之间的电容。如果能找到高介电常数的物质,也同样能够增大电容值。

采用高电常数(high-k)的栅极介质,并且增加其厚度,则可获得低阈值电压、低沟道漏电、低栅极漏电的良好折中。

2007年,英特尔采用high-k介质技术,发布第一款基于45纳米的四核英特尔至强处理器以及英特尔酷睿2至尊四核处理器。

由于high-k介质的引入,随后的28nm制程的研发,也还算顺利。

为什么这层二氧化硅需要越来越薄,其实就是为了增大gate与闸极之间的电容。如果能找到高介电常数的物质,也同样能够增大电容值。

采用高电常数(high-k)的栅极介质,并且增加其厚度,则可获得低阈值电压、低沟道漏电、低栅极漏电的良好折中。

2007年,英特尔采用high-k介质技术,发布第一款基于45纳米的四核英特尔至强处理器以及英特尔酷睿2至尊四核处理器。

由于high-k介质的引入,随后的28nm制程的研发,也还算顺利。

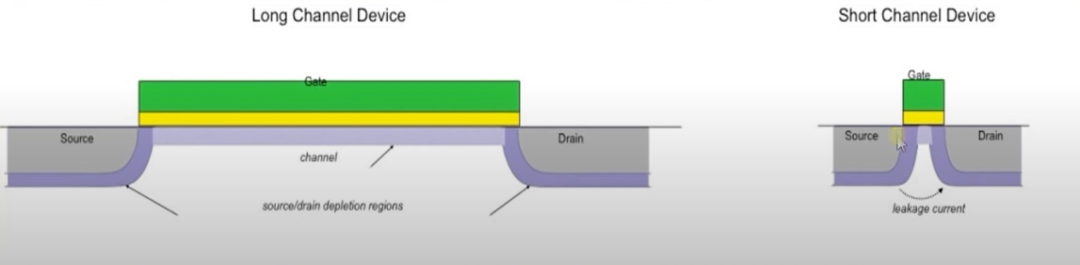

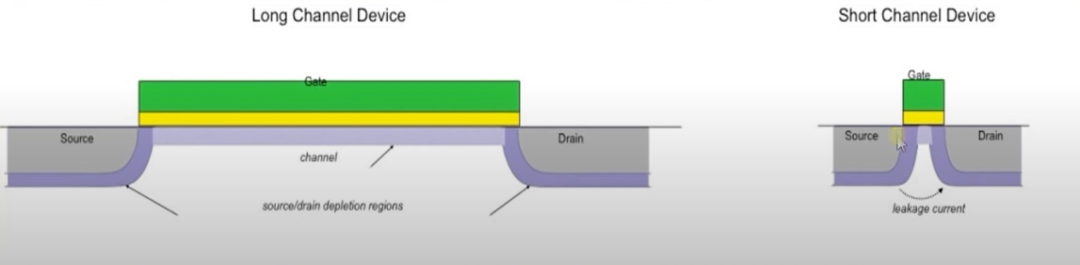

然而在28nm之后,人们发现,如果继续采用传统的Planar结构,摩尔定律难以为继。

这时候,大家的目光放到了两种非常有前途的结构上,那就是现在赫赫有名的FinFET结构以及他的竞争对手FDSOI。

这两种结构都是由业界泰斗胡正明教授在上世纪90年代提出。然后经过不断的论证和实验,趋于成熟。

他的思路就是,鉴于在关闭状态,source到drain之间的漏电主要发生于距离栅极较远的位置,那么,只需要将闸极厚度做到足够薄,那么漏电将会被有效的控制。

基于这个思路,他提出了两种结构,FinFET以及UTBSOI,UTBSOI是Ultra Thin Body SOI的简称,也就是后来的FDSOI。

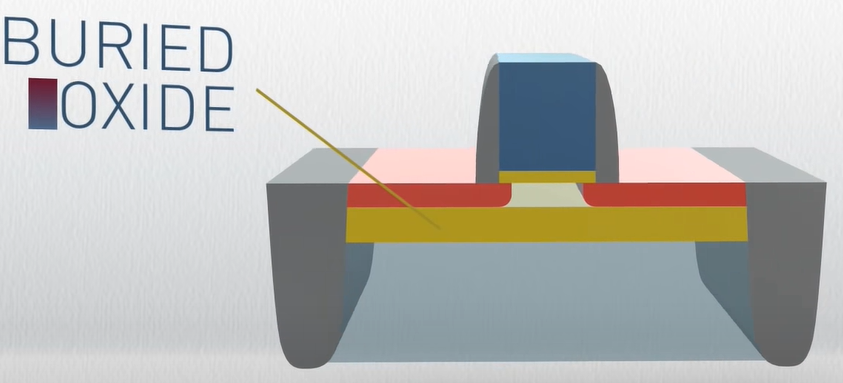

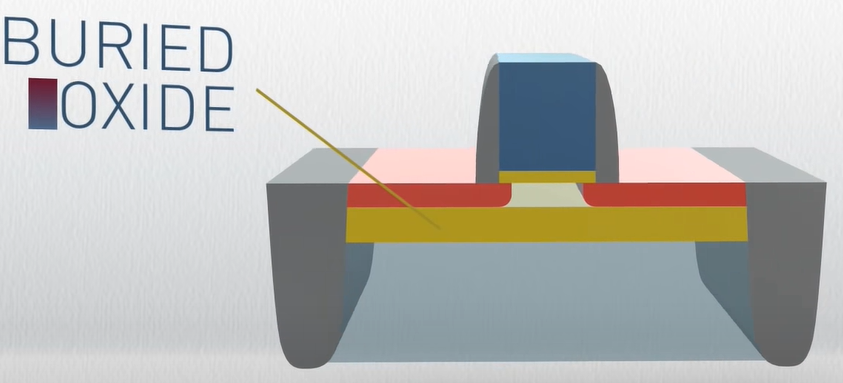

FDSOI, 是将cmos与衬底之间通过Buried oxide(埋氧层)隔离。SOI就是Silicon on Insulator的缩写。

buried oxide

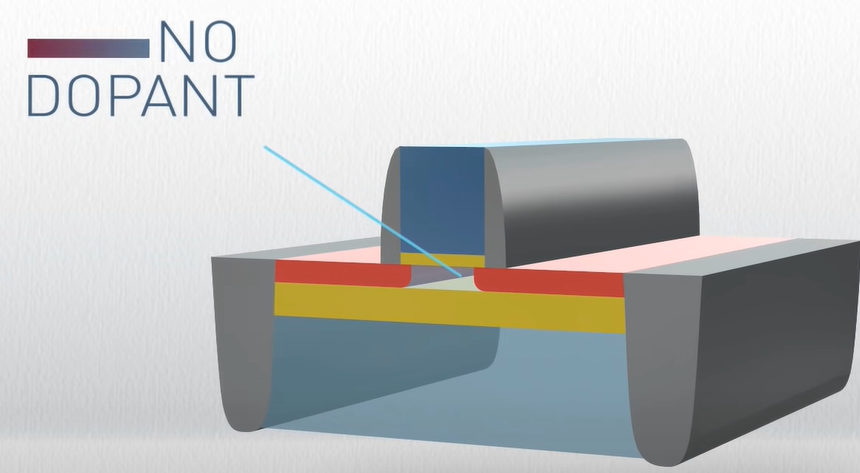

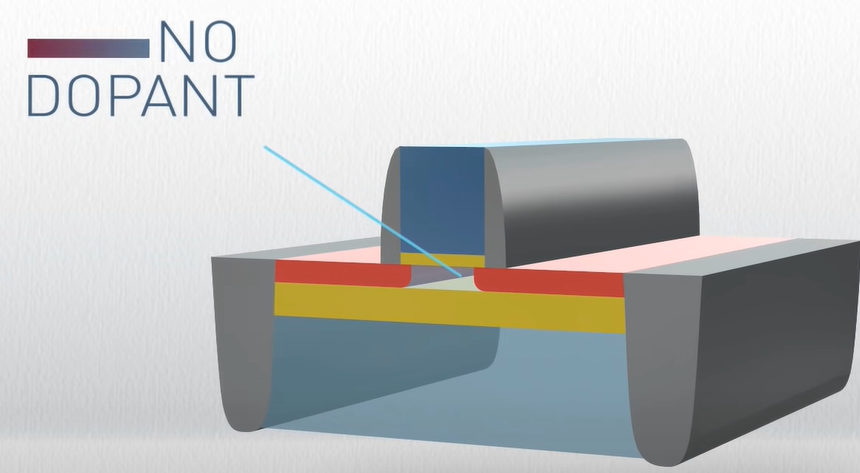

另外,沟道中的将不会进行掺杂,主要也是工艺上的原因,想象一下,在只有十几个原子的距离之间,进行掺杂,那么掺杂多一两个原子都会对晶体管的性能造成很大的影响,而以目前的技术手段,尚不能做到如此精确的控制。

buried oxide

另外,沟道中的将不会进行掺杂,主要也是工艺上的原因,想象一下,在只有十几个原子的距离之间,进行掺杂,那么掺杂多一两个原子都会对晶体管的性能造成很大的影响,而以目前的技术手段,尚不能做到如此精确的控制。

FDSOI的关键点是闸极(body)做到非常薄。只有这样才能够减少SD之间的漏电。如果厚的话,距离栅极远的地方,漏电依然无法避免。

FDSOI的关键点是闸极(body)做到非常薄。只有这样才能够减少SD之间的漏电。如果厚的话,距离栅极远的地方,漏电依然无法避免。

这也是为什么当时胡正明教授提出这种结构时,称之为UTBSOI的原因。

这也是为什么当时胡正明教授提出这种结构时,称之为UTBSOI的原因。

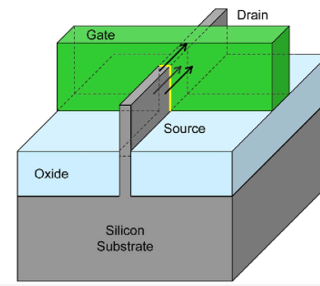

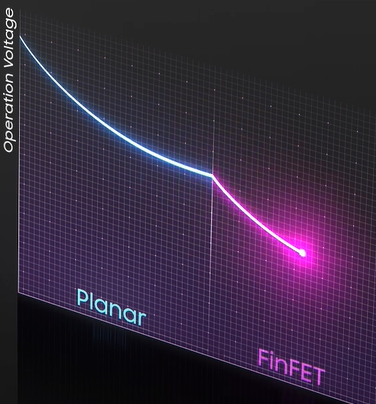

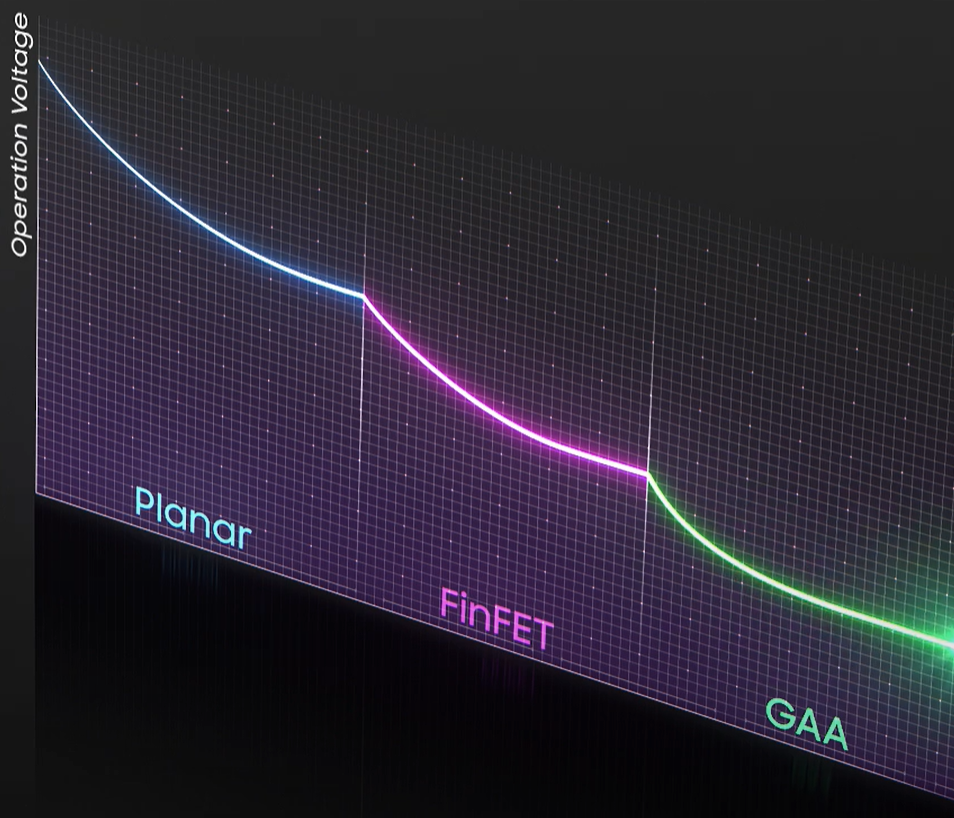

FinFET的鱼鳍(Fin)的结构,增加了栅极对沟道的控制面积,使得栅控能力大大增强,也意味着电压可以进一步降低。

与FDSOI相同,对于闸极材料均不进行掺杂,避免了离散的掺杂原子的散射作用,同重掺杂的平面器件相比,载流子迁移率将会大大提高。

FinFET的鱼鳍(Fin)的结构,增加了栅极对沟道的控制面积,使得栅控能力大大增强,也意味着电压可以进一步降低。

与FDSOI相同,对于闸极材料均不进行掺杂,避免了离散的掺杂原子的散射作用,同重掺杂的平面器件相比,载流子迁移率将会大大提高。

FinFET vs FDSOI:

由于有隔离层与衬底有了隔离,FDSOI有一些特有的特性。

即使衬底可以进行偏压,从而调整晶体管的导通阈值,做到性能与功耗的平衡。虽然目前来看,FDSOI并未成为主流,但是其低成本,低功耗的特性,非常适于现在IOT的大规模应用,因此有其独特的地位。

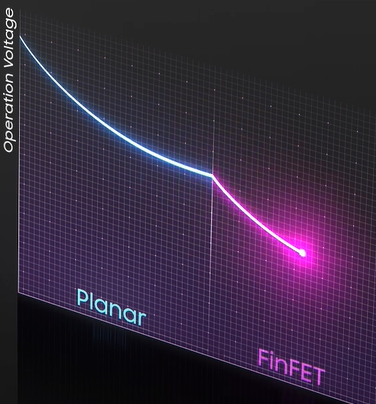

不过,FDSOI虽有成本优势,因为仍然属于平面工艺,尺寸难以做小,目前来看,在到达12nm之后,将难以再进行缩小。

FinFET工艺,使得工艺制程在28nm之后,不断的得以更新换代,直至最新的5nm。

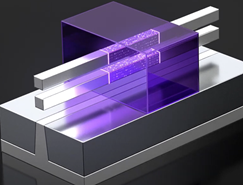

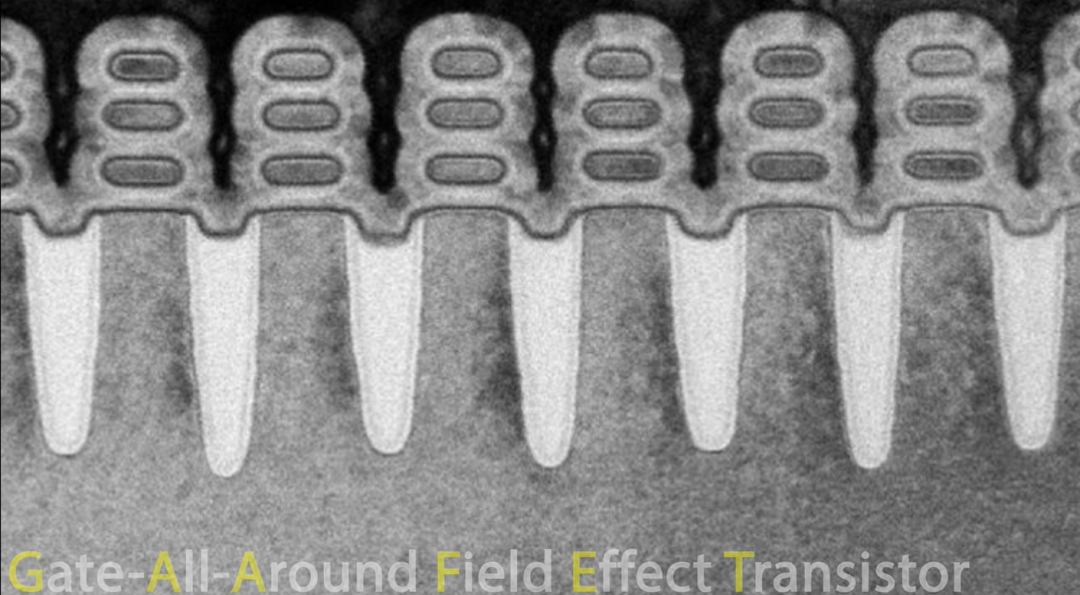

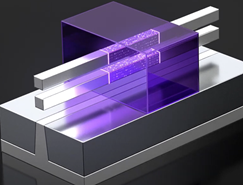

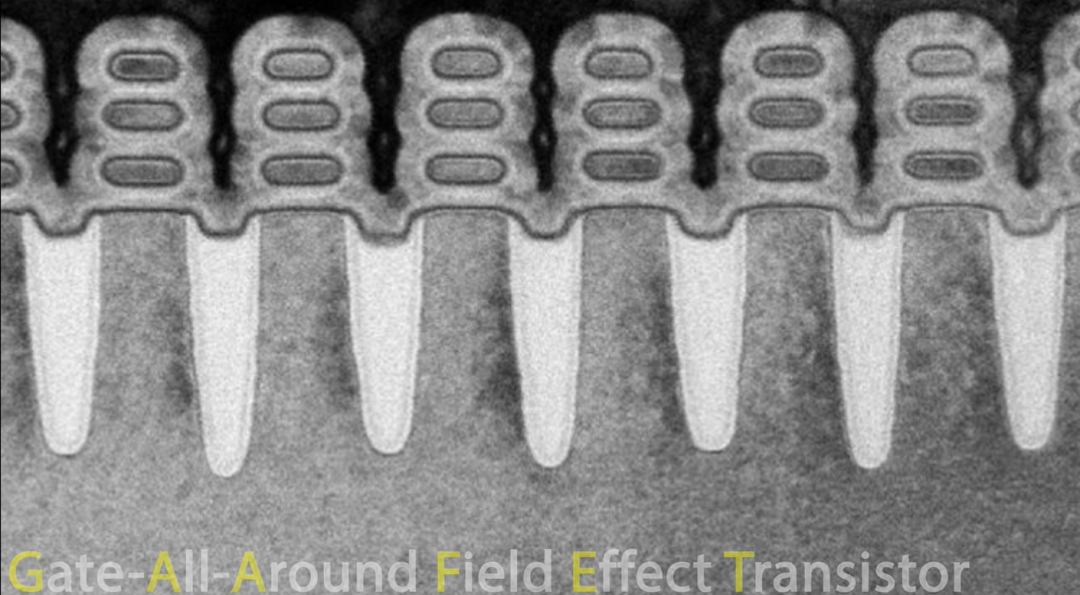

与FinFET的不同之处在于,GAA将通道的四周都被栅极包围,所以称之为Gate All Around。

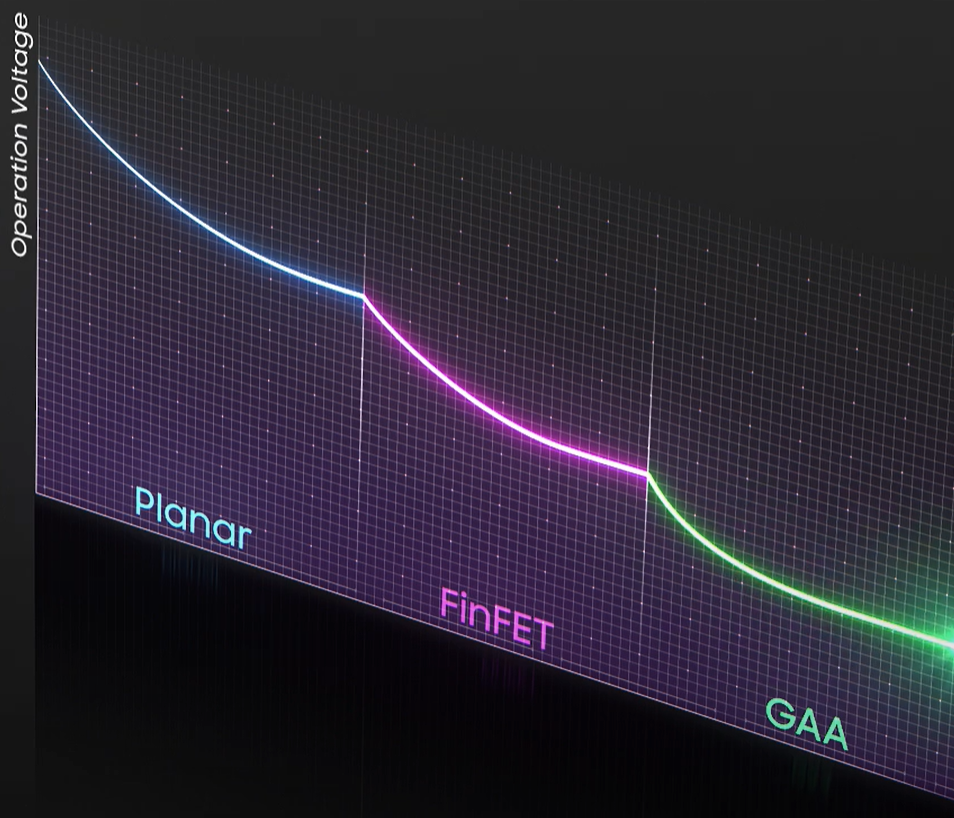

趋势上来看,FinFET的电压已经降到极限,而GAA,能够将工作电压进一步降低。

趋势上来看,FinFET的电压已经降到极限,而GAA,能够将工作电压进一步降低。

目前,intel准备在5nm上使用GAA,三星,则准备在3nm上采用GAA。根据台积电财报会议公布的最新消息,台积电在其准备量产的3nm工艺制程上,不过可以确认,仍将采用FinFET工艺。

目前,intel准备在5nm上使用GAA,三星,则准备在3nm上采用GAA。根据台积电财报会议公布的最新消息,台积电在其准备量产的3nm工艺制程上,不过可以确认,仍将采用FinFET工艺。

FinFET开启了晶体管立体化的时代,相当于将闸极直立起来。GAA,则是将FinFET中的Fin,再次切割出更多的切面以增大与栅极接触面积。

三星提出的称为MBCFET(multi bridge Channle FET)的结构,则更进一步,类似于将FinFET中的多个Fin的结构再进行堆叠。

晶体管纵向排列的好处显而易见,以前一个晶体管的面积,现在可以容纳多个晶体管,晶体管的增加,将不会带来面积的变化。

晶体管纵向排列的好处显而易见,以前一个晶体管的面积,现在可以容纳多个晶体管,晶体管的增加,将不会带来面积的变化。

十年前,也就是2010年,当传统planar CMOS结构走到尽头时,由于胡正明教授发明的FinFET以及FDSOI新结构晶体管,使得摩尔定律得以延续传奇。

无论未来新的结构会不会替代FinFET,无论摩尔定律会不会在未来某一天终结,但是就像胡正明教授所言,半导体产业本身的发展,仍然远远没有到尽头,即使百年之后,它仍将存在。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2302期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

国外半导体|华为

|ARM

|

AI

|设备

|晶圆|英伟达|射频|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

buried oxide

buried oxide