CMOS图像传感器,路在何方?

来源:内容授权转载自公众号「 MEMS」,作者:麦姆斯咨询王懿,谢谢。

CMOS图像传感器制造的工艺问题

智能手机搭载的CMOS图像传感器数量还将增加,为摄像头赋予高分辨率和丰富的功能。例如,三星最新款5G智能手机搭载了五个摄像头,其中一个是基于1.08亿像素(108MP)CMOS图像传感器的后置广角摄像头。这相当于要在如此小尺寸的芯片上集成超过1亿的像素。根据TechInsights介绍,其用于自拍的前置摄像头集成了一颗4800万像素的CMOS图像传感器,像素间距为0.7µm,号称全球像素间距最小的CMOS图像传感器。

CMOS图像传感器上集成了许多微小的光敏像素。像素间距指从一个像素中心到另一个像素中心的距离,以微米(µm)为单位。并非所有手机都需要配备最先进的CMOS图像传感器,也并非所有消费者都乐于用手机拍照。但不可否认,消费者对更多成像功能的追求不会停止。

UMC(联华电子)营销技术总监David Hideo Uriu表示,“从3G到4G,再到现在的5G,要求更高的带宽数据性能,也带动了对高质量摄像头需求的增长。除此以外,对更高像素和更佳分辨率的追求,都推动了CMOS图像传感器的市场热潮。智能手机在红外和近红外光谱的生物识别、3D传感、增强人类视觉等应用也逐渐得到关注。”

CMOS图像传感器厂商仍面临一些挑战。多年来,他们一直在为减小像素间距而努力。这样,图像传感器的像素越多,分辨率也越高。但是,随着像素间距尺寸与光的波长越来越接近,像素缩小变得越来越困难。豪威科技(OmniVision)工艺工程副总裁Lindsay Grant表示:“现在研发团队必须找到新方法来避免灵敏度降低和传感器的串扰增加。”

另一种趋势是CMOS图像传感器的像素大小保持不变,改进方向从减少像素尺寸转向提高图像质量。这个趋势与用户对更大手机屏幕、更佳拍照性能的需求一致,CMOS图像传感器的芯片尺寸则随之增加。

尽管如此,图像传感器厂商已经找到了解决某些挑战的方法。如:(1)采用新工艺:高K薄膜和其它制造技术。(2)芯片堆叠和互连技术,将两颗不同功能的芯片堆叠起来并不是什么新鲜事。但是新的互连方案,例如像素与像素互连(pixel-to-pixel)工艺还处于开发阶段。

图像传感器市场动态

针对各种应用,CMOS图像传感器的格式、帧率、像素尺寸和分辨率也各有不同。图像传感器分为全局快门(Global Shutter)和卷帘快门(Rolling Shutter)。例如,豪威科技最近推出的0.8µm 6400万像素图像传感器,实现1/1.7英寸格式。该传感器可提供静态图像捕获和4K视频性能,配备2x2微透镜相位检测自动(PHAF)对焦功能,可提高自动对焦精度,以每秒15帧(15fps)输出6400万像素画面。

CMOS图像传感器厂商可分为两个阵营:无晶圆厂(fabless)和IDM。IDM拥有自己的晶圆厂,而fabless公司则委托晶圆代工厂制造。无论哪种方式,在晶圆上完成图像传感器芯片后,都需要将其切割并进行封装。

根据Yole称,约有65%的图像传感器采用12英寸晶圆。“对安防、医疗和汽车等众多应用来讲,8英寸晶圆的CMOS图像传感器工艺制程仍然重要。”Lam Research(泛林半导体)战略营销部的总经理David Haynes说。

索尼(Sony)是CMOS图像传感器厂商的霸主,其次是三星(Samsung)和豪威科技。根据IC Insights透露,其它重要厂商包括夏普(Sharp)、安森美(ON Semi)、意法半导体(STMicroelectronics)、格科微(GalaxyCore)、海力士(SK Hynix)、松下(Panasonic)和佳能(Canon)。

根据IC Insights的数据,2019年CMOS图像传感器市场规模达到184亿美元,相比2018年增长30%。“我们预测2020年CMOS图像传感器市场规模将出现负增长(下降3%),最终的市场规模约178亿美元。受新冠疫情影响,手机和其它系统对CMOS图像传感器的需求下降,市场规模持续增长的曲线将出现拐点。”IC Insights的分析师Rob Lineback这样预测。

不同智能手机厂商对摄像头配置策略也不同。例如,苹果iPhone 11 Pro后置三摄配置为:1200万像素广角 + 1200万像素长焦 + 1200像素超广角。三星的5G手机配置了五个摄像头,包括四个后置摄像头和一个前置摄像头,其中一个为ToF摄像头,用于手势识别和3D物体识别。

摄像头的高分辨率不一定等同于能拍出更好的照片。“这是像素尺寸和分辨率之间的博弈,”Girardin说,“像素减小意味着有更多像素。当分辨率超过4000万像素和5000万像素时,捕获细节的能力可能会超过肉眼。对于CMOS图像传感器来讲,拥有更高的量子效率(QE)和信噪比的像素才是决定图像质量优劣最重要的要素。”

未来,虽然智能手机无法取代专业摄影师的数码单反相机。但显然,智能手机提供了比以往更多的功能。维易科(Veeco)产品营销高级经理Ronald Arif表示:“5G能带来更多带宽和潜在的应用,例如体育赛事的8K流媒体现场直播,实时AR(增强现实)、VR(虚拟现实)、MR(混合现实)游戏,这对手机用户的吸引力是无穷的。最新5G手机中的摄像头更加先进,整合了VCSEL的3D传感功能,可用于自动对焦或任何场所(如客厅)的3D投影映射(3D mapping)。可以想象,深度映射功能、5G与先进摄像头的组合会带来丰富的新应用(app),例如游戏、实时流媒体、远程学习和视频会议。”

近红外(NIR)图像传感器是CMOS图像传感器厂商正在交付的创新产品。近红外图像传感器可以探测到物体可见光谱之外的波长,专为在昏暗或黑暗环境中工作的应用而设计。豪威科技最新推出的近红外技术Nyxel 2,使不可见的940nm近红外光谱内量子效率提高25%,而在几乎不可见的850nm近红外波长处的量子效率提高17%。

索尼和Prophesee共同开发了基于事件的视觉传感器。这类传感器主要面向机器视觉应用,可在各种环境中探测到快速移动的物体。

像素尺寸缩小竞赛

几年前,CMOS图像传感器的像素间距为7µm。CMOS图像传感器厂商一直在致力于减小像素间距,但问题层出不穷。

CMOS图像传感器的结构非常复杂。顶层为微透镜阵列,下一层是绿色、红色和蓝色阵列的彩色滤光片,接着是由捕获光线的光电二极管和其它电路组成的有源像素阵列。

有源像素阵列由许多微小的单个感光像素组成。每个像素由光电二极管、晶体管和其它元件构成,像素大小以微米(µm)为单位。

像素尺寸越大的图像传感器,收集的光越多,信号越强。但图像传感器尺寸较大,会占用更多的电路板空间。像素尺寸较小的图像传感器,收集的光较少,但可以将更多的图像传感器封装在一起,从而提高分辨率。

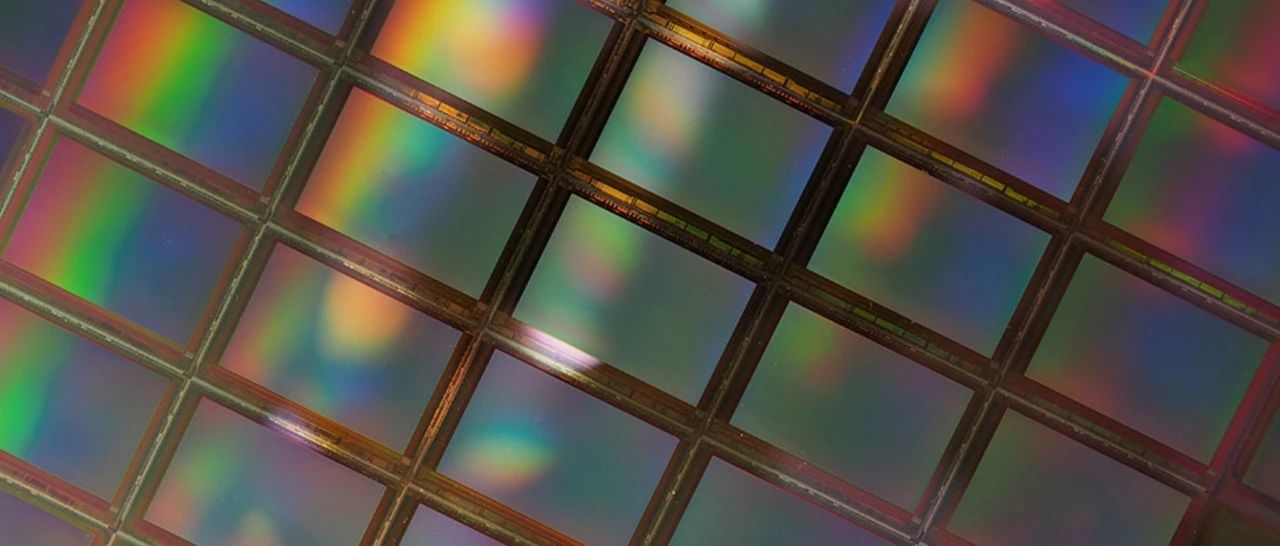

在晶圆代工厂中,图像传感器的制造流程有几种。其中一种简单制造流程中,像素阵列已完成。制备流程从对衬底的正面处理开始。晶圆与载片(carrier)或操作晶圆(handle wafer)键合在一起。对顶层进行注入工艺,再进行退火。在顶部涂上抗反射涂层,再完成彩色滤光片和微透镜阵列。在另一种简单制造流程中,对硅衬底表面进行注入。在顶部形成扩散阱和金属堆叠层。将晶圆翻转,在背面刻蚀出沟槽,在沟槽的侧壁进行隔离氧化层(liner)沉积并填充介电材料。最后在顶部完成滤光片和微透镜阵列。

直到2009年,主流CMOS图像传感器均采用前照式(FSI)像素阵列结构。工作时,光线会照射到传感器正面。微透镜收集光并将其传输到彩色滤光镜。光穿过互连的堆叠并被二极管捕获。电荷在每个像素处被转换为电压,所有像素的信号被收集。

多年以来,在CMOS图像传感器厂商的努力下,经历了多次迭代,像素间距不断减小。据TechInsights称,2006年像素间距为2.2µm,2007年就减小到1.7µm。

2008年,像素间距为1.4µm的FSI结构出现,再次打破了产业壁垒。约从2009年开始,CMOS图像传感器厂商开始采用一种新的结构:背照式(BSI)。BSI结构将图像传感器的光线入射方向从晶圆正面“反转”至背面。当光线从硅衬底的背面进入,光子经过光电二极管的路径更短,从而提高了量子效率。

BSI结构可以进一步缩小像素尺寸。Lam的Haynes解释:“像素尺寸在1.2µm至1.4µm的范围内,BSI技术可实现最佳像素尺寸,而堆叠式BSI可使这个像素尺寸范围内的COMS图像传感器的占位面积保持在30平方毫米以下。亚微米尺寸的像素,可以实现四分之一像素格式,获得超过4800万像素的分辨率。”

除了BSI技术,厂商还在对其它技术进行改进。图像传感器内的光电二极管(捕获光的关键元件)也在缩小,但会降低效率。而且二极管靠得更近,会产生串扰。

在2010年左右,当像素间距达到1.4µm时,CMOS图像传感器厂商在制造工艺的创新方向又一次发生了改变:深沟槽隔离(DTI)。DTI工艺的目标是使光电二极管“长得更高”,从而增加单位面积的容量。为了实现DTI工艺,厂商依然采用BSI结构,并通过各种工艺增加光电二极管的“高度”,同时要求增加二极管周围的硅的厚度。

不过,像素尺寸的缩小速度已经放缓。曾经有一段时间,CMOS图像传感器厂商踩着每年缩小像素尺寸的节奏前行。但是,据TechInsights称,从1.4µm(2008年)演进到1.12µm(2011年),花了三年的时间,达到1µm(2015年)耗费了四年,此后过了三年才达到0.9µm(2018年)。

TechInsights分析师Ray Fontaine在近期的博客中谈到:“总体来说,我们认为DTI和相关钝化方案的开发,是导致1.12µm缩小到0.9µm进程缓慢的主要原因。”

最近,厂商已解决了这些问题。像素缩小竞赛的紧张气势再次燃起。2018年,三星突破了1µm的技术壁垒,达到0.9µm;索尼在2019年达到0.8µm,在2020年又突破了0.7µm。

对于亚微米级像素,CMOS图像传感器行业需要更多的创新。Fontaine在最近的演讲中讲到“随着像素的缩小,需要更厚的有源(硅)来保证光电二极管尺寸。厚(硅)是DTI和相关高K钝化层的关键技术。”

用高K薄膜制造的图像传感器与上述传统流程基本一致。不同之处在于,高K薄膜是沉积在DTI沟槽的隔离氧化层上面。

对于高K工艺和其它工艺,厂商在晶圆代工厂中采用两种不同的方法:前DTI(F-DTI)和后DTI(B-DTI)。豪威科技的Grant解释:“F-DTI使用多晶硅填充间隙,多晶硅的电压偏置可以改善表面钉扎效应。F-DTI还可以进行更多的热处理以减少蚀刻损伤。B-DTI采用带负电荷的高K薄膜来积累电荷,在表面出现费米能级钉扎效应,从而抑制暗电流漏电。高K薄膜沉积采用原子层沉积(ALD)工艺完成。B-DTI通常使用氧化物填充间隙,也尝试了金属填充甚至空气间隙,并已用于批量生产。”

像素缩小竞赛会继续进行吗?Grant认为:“像素尺寸很有可能小于0.7µm。随着像素缩小到0.7µm,需要优化的方面还很多。比如在B-DTI工艺中,对二极管的高能注入,彩色滤光镜和微透镜的光学结构缩小等关键项目仍将是发展重点。像素内晶体管和互连的基本设计规则需要更新。”

另一个问题是移动设备中图像传感器的像素间距正在接近光的波长。Grant说:“有些人可能认为这是像素尺寸的极限。例如,研发0.6µm的像素间距。它小于0.65µm(650nm)的红光波长。因此可能会出现一个问题:‘为什么要缩小到亚波长?用户会受益吗?将像素缩小到亚波长意味着在像素级别空间分辨率信息更有价值。’”

Grant指出,1.0µm像素的光学结构使用了许多亚波长特征。“例如,用于抑制串扰的窄金属网格和用于量子效率改善的窄介电侧壁正在通过光的引导而进行改进。这种纳米光学工程已在现有像素技术领域应用多年,所以缩小到亚波长并非革命。持续缩小的局限,可能来自用户利益而不是技术。正是出于不断发现像素缩小为最终用户带来价值的目的,才推动着这一趋势。只有这样,CMOS图像传感器技术的开发才会继续支持这一方向。”

堆叠和互连技术

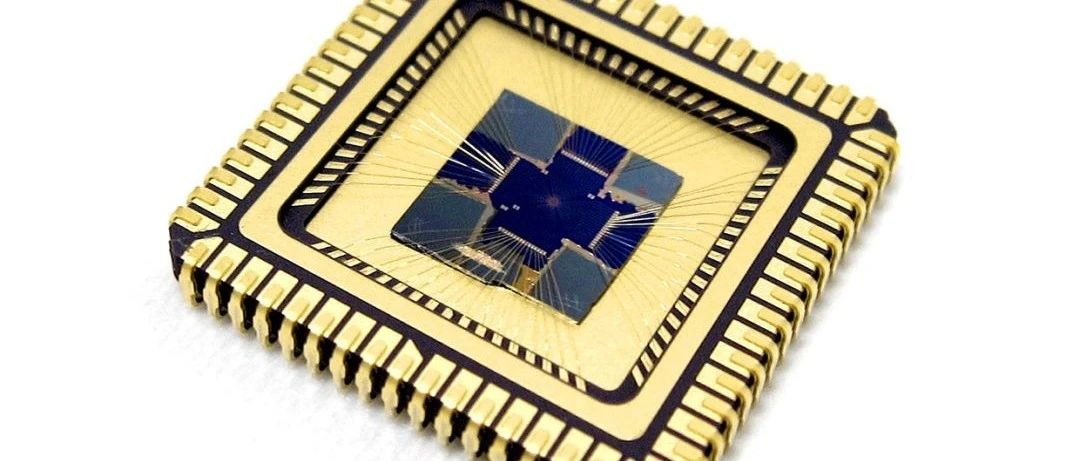

多年来,图像传感器都将像素阵列和逻辑电路集成于同一颗芯片。2012年,索尼推出了两层堆叠式图像传感器。芯片堆叠使厂商可以将传感功能和处理功能拆分到不同的芯片。这允许传感器具有更多功能,同时还可以减小管芯尺寸。

为此,索尼开发了90nm工艺的像素阵列芯片。该芯片堆叠在一颗65nm图像信号处理器(ISP)芯片上,该芯片提供处理功能。然后将两颗芯片互连。

最终,其它厂商转向了类似的芯片堆叠方案。通常,顶部像素阵列芯片采用成熟节点工艺。底部ISP芯片的工艺节点涉及65nm、40nm和28nm。14nm FinFET(鳍式场效应晶体管)技术正在研发中。

在2018年,三星和索尼同时开发了三层堆叠式图像传感器。例如,在索尼的CMOS图像传感器产品系列的一种版本中,DRAM(动态随机存取存储器)单元位于图像传感器和逻辑电路层之间。嵌入式DRAM可实现更快的数据读取。

除了芯片堆叠之外,厂商还开发了不同的互连方案,该方案将一颗芯片与另一颗芯片互连。最初,豪威科技、三星和索尼使用硅通孔(TSV)技术。2016年,索尼转向了一种称为“铜混合键合”的互连技术。三星仍处于TSV阵营中,而豪威科技则同时采用TSV和混合键合两种工艺。

在混合键合中,使用铜-铜互连连接管芯。在晶圆厂中对两片晶圆进行处理,一片是逻辑电路,另一片是像素阵列。使用电介质-电介质键合(dielectric-to-dielectric bond)将两片晶圆键合在一起,然后完成金属与金属的互连。

TSV和混合键合均可实现精细的像素间距。Lam的Haynes说:“在CMOS图像传感器像素和逻辑电路两片晶圆堆叠的BSI结构,TSV和混合键合可能会继续共存。但是随着多层堆叠BSI图像传感器的发展,TSV集成将变得越来越重要。”

谈起其它技术趋势。KLA(科天)营销高级总监Steve Hiebert说:“将来,我们有望看到与CMOS图像传感器芯片堆叠相关的两种趋势。首先是进一步缩小像素间距,以实现更高的芯片互连密度。另一种是三个或更多器件的堆叠。”

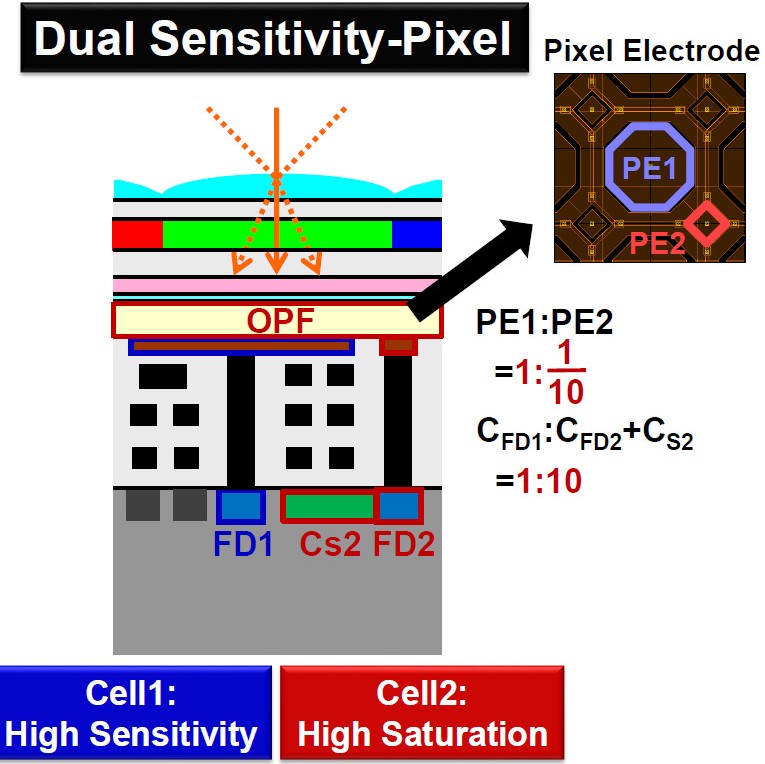

pixel-to-pixel互连将是未来的“重磅炸弹”。Xperi正在开发一种称为“3D混合BSI”的技术,用于像素级集成。索尼和豪威科技已经展示了这项技术。

Xperi产品营销高级总监Abul Nuruzzaman说:“3D混合BSI可以实现更多的互连。实现每个像素与关联的模数转换的像素级互连。这允许对所有像素进行并行的模数转换。该连接提供了堆叠像素层和逻辑电路层之间的高密度电气互连,从而实现了与有效百万像素数量一样多的模数转换器。混合键合还可以将堆叠式内存中的专有内存与对应像素的互连。”

这种架构支持大规模并行信号传输,从而可以高速读取和写入图像传感器的所有像素数据。Nuruzzaman表示:“这可以为对时间要求非常严苛的各种应用(例如自动驾驶汽车、医学成像和高端摄影)提供实时比例缩放像素的全局快门和高分辨率成像。”

结论

尽管如此,市场上还会涌现创新浪潮。IC Insights的Lineback表示:“嵌入式CMOS图像传感器和摄像头在安防、安全、基于视觉的用户界面和识别、物联网、自动驾驶汽车和无人机等更多系统中的应用前景依然可期。”

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2294期内容,欢迎关注。

推荐阅读

★ 浦东芯片三十年

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

中国半导体|苹果 |封测 | 蓝牙 |设备 |晶圆|英伟达|射频|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 复杂SoC芯片设计中有哪些挑战?

- 2 进迭时空完成A+轮数亿元融资 加速RISC-V AI CPU产品迭代

- 3 探索智慧实践,洞见AI未来!星宸科技2024开发者大会暨产品发布会成功举办

- 4 MediaTek 发布天玑 8400 移动芯片,开启高阶智能手机全大核计算时代