[原创] 3nm成为下一个关键战场

2020-04-03

14:00:08

来源: 半导体行业观察

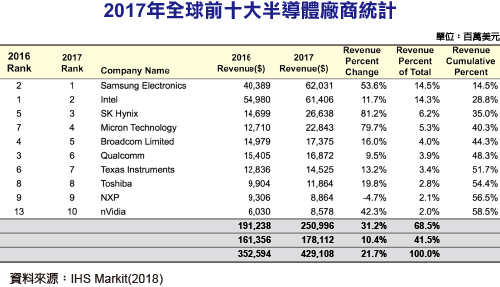

2017年三星将代工业务独立了出来,此后,三星曾多次强调要挑战代工领头羊台积电的地位。但根据相关调研机构所统计的2019年第四季度两者的营收来看,台积电仍遥遥领先于第二名的三星。

在这种情况下,三星代工要想超越台积电,只能将希望寄于下一代先进制程。在其2019年晶圆代工论坛上,三星不仅公布了其先进制程发展规划,还公布了他们在3nm工艺上的重要进展。此举也将先进制程的竞争带入到了3nm阶段。

结合三星发布的代工发展路线图中看,三星的5nm工艺将作为其7nm LPP的改良面向市场推出,而3nm工艺才被三星视为是能够超越台积电的关键节点,在该节点中,三星将采用GAA MCFET(多桥通道FET)工艺。为什么三星会将赌注押在3nm节点上?

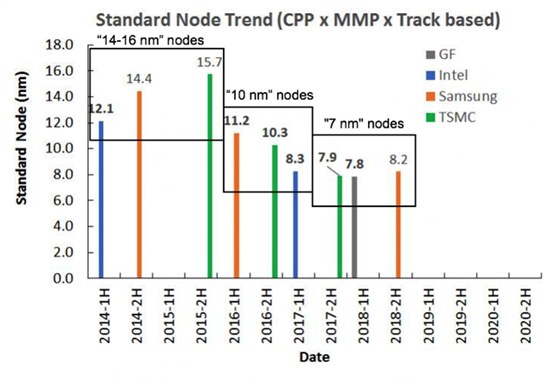

从三星和台积电在过去三年的竞争中看,当年三星将其代工业务独立出来之时,也正值先进工艺即将进入10nm工艺阶段。彼时,两者均推出了10nm工艺的产品。但当年三星10nm大客户仅有高通,不敌台积电。

此后三星又在10nm上推出三种不同的改进工艺,以试图抢夺更多的订单。而台积电则在推出10nm以后,转向了更具优势的7nm工艺。7nm对于半导体制造工艺来说是非常重要的里程碑。2018年台积电宣布其7nm开始量产,三星则是选择在7nm上使用EUV。同年,三星7nm EUV也宣布了量产计划,但因其7nm EUV工艺技术不够成熟,因而未能得到市场的认可。在此期间,华为海思、高通、英特尔和联发科等企业纷纷投入到台积电的怀抱。三星错失了抢夺7nm订单的最佳时期。

但根据市场情况来看,7nm在如今的市场中仍然保持着活力,三星7nm EUV技术也在去年得到了改善。于是,三星凭借低价抢夺了原在台积电手中的英伟达的订单。此外,三星还从台积电手中抢走了IBM Power系列处理器的订单。但这并不足以支撑三星在7nm上超越台积电。所以,三星只能放眼下一代先进制程。

为什么三星没有瞄准5nm工艺?就目前的消息来看,外媒报道称,台积电将在4月份开始大规模量产5nm芯片。而三星则正在加速在韩国华城建设5nm生产工厂V1,预计6月底之前完成生产线建设,据此推算,其5nm工艺最快也是在今年年底才能进行生产。由此来看,在5nm进度上三星暂时无法超越台积电,首先进入到量产阶段。这也意味着,三星将错失首批采用5nm工艺的芯片的订单。

所以,三星瞄准3nm工艺,并试图抢先进入量产,会为其超越台积电提供支撑。除这两者之外,英特尔也对3nm抱有很大的期望。据快科技报道称,英特尔计划在2021年末推出7nm工艺,5nm重拾领导地位。其首席财务官Davis预测英特尔的7nm节点(大概与台积电的5nm相当)将在2021年末重新追平业内发展水平。如果按照这种发展推测,英特尔的5nm性能则有可能相当于台积电的3nm,而英特尔计划在5nm重拾领导地位,也就意味着,3nm的玩家将会又增加一个。

晶圆代工厂在3nm节点会进行激烈的竞争,在保证良率的前提下,抢先进入量产也许会带来更大的竞争优势。因此,很多代工厂也在3nm工艺上进行了大量的投资。

三星曾在2019年宣布,将在未来10年内(至2030年)在包括代工服务在内的其逻辑芯片业务上投资1158亿美元,以期超越台积电,成为全球第一大芯片代工厂。

EUV是三星试图超越台积电的一大杀手锏,它在7nm工艺上就率先用上了EUV技术。其华城V1厂为三星第一条专门生产EUV技术的生产线。三星总裁兼晶圆代工业务主管ES Jung表示,V1生产线目前以7纳米、6纳米制程生产最先进的行动芯片,并持续朝着3纳米前进。按照三星的计划,到2020年底V1生产线投资金额将达到60亿美元。为了支持三星达成2030年南韩成为全球晶圆代工第一、IC设计市占率10%目标。去年,韩国总统文在寅在参访该工厂时曾表示,韩国政府政府也要在未来10年投资80兆韩元,鼓励相关业者的投资与研发,另一方面韩国政府也将从教育政策着手,在未来10年培养出17,000名相关工程师。

通过大量资金的投入,三星也率先公布了其在3nm上的进展。2019年三星宣布将在3nm节点放弃FinFET晶体管,转向GAA环绕栅极晶体管工艺。据悉,采用GAA技术的3nm工艺可将核心面积减少45%,功耗降低50%,性能提升35%。据韩媒Business Korea报道,三星电子已经成功开发了业界首个3nm制程,预计将于2022年开启大规模量产。

相比于三星,台积电在3nm方面的消息比较少。在投资方面,据相关媒体报道称,台积电3nm 工艺总投资500亿美元,其中,建厂至少200亿美元。

在生产计划方面,据外媒报道称,由于新冠肺炎疫情的影响,导致全球物流与人员流动大乱,设备供应同步受到影响,台积电3nm试产线安装被迫延后,原定6月装机的安排将延迟到10月。

在技术方面,台积电相关3nm的消息还不十分明确。只是之前有报道称,在晶体管的选择上,台积电采取了更稳妥的方案,依然是分两步走,首先初期3nm依然采用FinFET工艺,等成熟后在3nm或2nm后期再转向GAA晶体管技术。但曾经有据业内人士透露,台积电3纳米制程在环绕式闸极技术上已经有了新突破。照此进程来看,台积电既已有了环绕式闸极技术却没有优先将其导入3nm工艺当中,或许是为了抢夺首先量产3nm的机会(三星优先在7nm上采用了EUV技术,但因技术不够纯熟,也因此错失了大量7nm的订单,由此来看,导入新技术对于代工厂而言是一件非常冒险的事情。因此,在新型晶体管面前,台积电保持了谨慎的态度)。台积电3nm更详细的消息或将在其技术论坛上披露,但据最新报道显示,台积电原定于相4月29日的技术论坛将推迟到8月24日举行。以此来看,在今年晚些时间我们才能窥见台积电在3nm技术上的进展。

而英特尔在3nm上的消息更是稀少。据Techweb的报道显示,按照英特尔的发展规划,英特尔的7nm工艺将在2021年开始采用,7nm+和7nm++则会在随后的两年分别推出。7nm之后是更先进的5nm、3nm、2nm和1.4nm,其中5nm、3nm和2nm处在路线发现阶段,分别计划在2023年、2025年和2027年采用,2029年拟开始采用1.4nm工艺。同时,也有消息称,英特尔也将在5nm工艺阶段放弃FinFET晶体管,转向GAA环绕栅极晶体管。其首席财务官也曾指出,英特尔要进行10nm量产、7nm提速、5nm投资,考虑到这部分技术交集主要集中在2020~2021年,也必然会影响到英特尔毛利率。

代工厂正在积极备战3nm到来时的竞争。在这个过程当中,仍然还存在众多的挑战等待他们去解决。

首先是EUV设备上挑战,虽说现在台积电和三星的7nm EUV产品已经步入正轨。但当先进工艺推进到3nm之时,与之相关的EUV技术也将再次发生变化。据相关报道显示,3nm EUV也许会采用多重曝光的方式(3nm EUV技术的三个方向:第一、把单次曝光的工程系数维持为0.29;第二、联合两次曝光(LELE技术)和把工程系数改为0.39的曝光技术;第三、利用三次曝光(LELELE)技术)。而这就涉及了EUV曝光技术的开发方面最重要的是EUV曝光设备(EUV scanner)的改良。

其次EUV的产业链也不够完善。莫大康曾在其文章中表示,EUV掩膜、Pellicle薄膜、检测掩膜的缺陷以及光源功率等都将影响EUV技术在先进工艺上的使用。

3nm所采用的新型晶体管也存在的挑战。新型晶体管的出现,意味着代工厂将对其进行大规模的投入。虽然台积电、三星以及英特尔都计划在GAA上有所投入,但在3nm初期阶段就采用新型晶体管,是否能够被市场接纳,也是值得厂商思考的事情。据镁客网的报道称,随着技术的变化和市场的发展,市场中未来制程工艺的变数也越来越大,因此3nm GAA也越来越难收到预想的克敌效果。台积电就曾对外表示,在材料方面,III-V族材料也有可能会代替传统的硅作为晶体管的通道材料以提升晶体管的速度。据相关报道称,III-V化合物可以取代FinFET上的硅鳍片,III-V族化合物半导体没有明显的物理缺陷,而且跟目前的硅芯片工艺相似,很多现有的技术都可以应用到新材料上。

另外,如果采用GAA工艺,则需要导入新材料InAsGe nanowire and Silicon nanowire,因此制程技术上相当困难,尤其是在蚀刻部分是大挑战。

此外,3nm工艺节点的互连也是一项挑战。互连是芯片中的微小铜布线方案,它在每个节点上变得越发紧凑,造成芯片中不必要的RC延迟。根据IEDM的课程整理,3nm以后可能会出现多种新型互连技术,BEOL需要微缩助推器和DTCO来增强工艺能力以实现器件架构。通过预填充(使用Co或Ru)可为替代金属提供垫脚石。但是互连将需要诸如Co或Ru之类的替代金属。

虽然3nm的雏形还未出现在业界的视野当中,但业界十分关注3nm的进展。在该节点阶段,相对保守的台积电和进击的三星之间的竞争将进入到白炽化阶段,同时,英特尔宣布他们也计划将在5nm阶段重回领导位置,将3nm的竞争再次推向了高潮。如论结果如何,代工厂们在3nm节点处必有一战,而胜者则为王。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2268期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

存储|传感器

|IGBT

|

ARM

|FPGA

|中兴|苹果|半导体股价|IP

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie