揭秘台积电5nm CMOS技术平台

2020-03-19

23:17:52

来源: Sophie

来源:内容由半导体行业观察(icbank)

编译自「

semiconductor-digest

」,作者:Dick James,

谢谢。

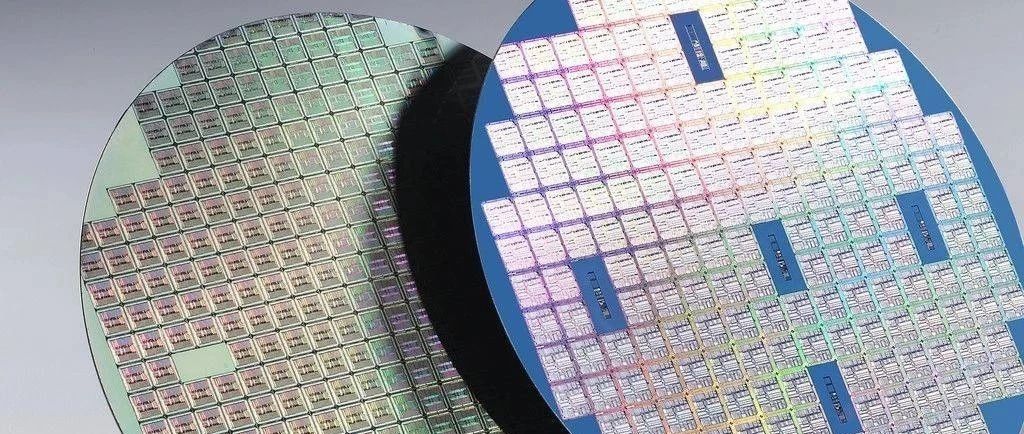

在去年年底于旧金山举行的国际电子设备会议(IEDM)上,台积电Geoffrey Yeap发表了“5nm CMOS生产技术平台”的演讲,该平台使用了成熟的EUV和高迁移率的沟道FINFET,其具备最高密度的0.021μm

2

SRAM单元,能备用用于移动SoC和高性能计算等应用。

在过去的一段时间里,5-nm (N5)工艺的细节已经被慢慢公布,最近一次是在去年4月份的技术研讨会和今年一月份的开放创新平台创新论坛(OIP)上,还有Arm TechCon,这些活动都在硅谷举行。我们将这些报告的信息浓缩起来,没有进行排序,当中包括有:

-

-

台积电 5nm于2019年3月开始风险试产;最近竣工的台南Gigafab 18将在2020年第二季度实现大批量生产(第一阶段设备安装于19年3月完成)

-

一年后将会有一个N5P(性能)版本,在相同功耗的前提下下将性能提升7%,或者在相同的性能下,功耗降低15%

-

与7nm相比,逻辑密度增加1.8倍,SRAM缩放了0.75,模拟缩放是~0.85。

-

与7nm相比,等功耗速度增益为15%,或在相同速度下,功耗降低低30%。

-

强调EUV的使用

-

将会有一个高迁移率沟道(HMC)晶体管

-

低电阻触点和通孔;金属间距略微宽松,通孔更宽。

-

晶体管的变种包括一个1.5V或1.2V的I/O晶体管和一个速度比7纳米等效器件快25%的极限LVT器件。

-

HPC标准单元中的通孔柱(Via pillars)和优化金属(optimized metal )将性能提高10%

-

可用的112Gbps SerDes

-

超高密度MIM电容器结构:2X ff/μm

2

,2X插入密度(insertion density),可将速度提高4%

-

新型低k介电材料

-

金属反应离子蚀刻(RIE),代替Cu damascene以获得小于30nm的metal pitch

-

石墨烯“帽”以降低铜互连电阻率

在测试电路中,有一个PAM4 Ser Destransmitter 展现出了了130 Gb/s的速度和0.96pJ/bit的能效。预计到2020年1H,该技术将获得高产、大批量生产的资格。

下面的图1显示了15%的速度和密度增益(左),以及七个Vt选项。

图2显示了5个浸没式掩模与1个EUV掩模在类似标准单元路由层(即M1或M2)的情况下的比较。如果Mx的暂定间距为30 nm,则需要使用SAQP或LE3,外加两个cut masks,然后用一个EUV 光刻步骤替换。使用30nm的MxP进行校准,该图像给我们提供了约175nm(约5.8个track cell)的track height ,与7nm制程相比,线性微缩约为0.73。我们可以看到这个pattern 更清晰了。

图2:用一个EUV代替5个浸没式pattern,具有更好的pattern保真度、更短的cycle time和更少的缺陷。

根据介绍,我们可以看到这个新设计拥有十层以上的EUV。但如果是在浸没式光刻中 切割,接触,过孔和金属线掩膜步骤中,其mask至少增加了4倍。他们还特别提到了基于EUV的栅极pattern工艺。5nm节点是台积电中第一代使用EUV降低总掩模数的节点(图3)。

图三 :5 nm节点的总掩模计数比较(未显示7FF +)

如下图所示,高迁移率沟道晶体管关进带来的驱动电流的提升(+18%)。有人评论说这可能是锗通道(fin),但考虑到Ge和Si之间晶格的不匹配,以及由此产生的位错,我们似乎更有可能拥有一个PMOS-SiGe通道,类似于IBM财团的平面入门级HKMG部件中使用的PMOS SiGe通道,其中包含高达40%的Ge。

图4,高迁移率设备中改善的驱动电流(左);通过电子束衍射确定鳍中的较高应力(右)

来自fin的高放大率TEM晶格图像表明,该通道是常规的<110>方向,但奇怪的是,右侧的衍射图像似乎是在<100>方向上拍摄的。

在相关报道中没有提到HMC通道的性质,所以我将继续使用SiGe通道。我从问答环节的报告中收集到的信息来看,当时也没有提供进一步的信息。

在planar 版本中,外延SiGe首先生长,然后在NMOS区域移除,在这种情况下只有3-5nm。如果active fin高约55nm,总fin高约120nm,那将是一个完全不同的挑战。但由于最近在纳米片器件上的所有工作,我们现在已经对SiGe和Si进行非常具有选择性的刻蚀。对我来说,一个更大的问题是,如果使用这种方法,SiGe fin将比Si fin高出几十纳米,在随后的处理中会增加复杂性。

为了使 fin保持在同一水平,我想我们可以对N-或P-区域进行蚀刻,然后是Si或SiGe的epi加上CMP(或选择性epi?),这取决于蚀刻的区域;这看起来也不简单。我认为我们会为Si和SiGe fin提供单独的fin定义蚀刻,但其带来quad patterning 听起来也很凌乱——也许fin刻蚀现在也是EUV?

考虑到SiGe通道将具有与纯Si通道不同的工作功能,我们可能会有一些带有Si通道的PMOS设备来增加可用的PMOS Vt范围。宣布的7个Vt是我们见过的最多的;TechInsights分析的三星10nm制程似乎有6个,英特尔在他们的10nm制程论文中宣布了6个。

下面的图6只是已发布的SRAM单元尺寸的曲线图,展现出的0.021μm

2

SRAM是迄今为止报告的最小SRAM。

在下面的图6中,我们有在5纳米测试芯片上构建的PAM4 SerDes transmitters 的眼图,展示了前面提到的112 Gb / s和摘要中详细介绍的130 Gb / s。

来到后端时,最紧金属( tightest metal)和通孔节距(via pitches)的Rc值接近7N节点的Rc值:

除了更新的刻蚀停止层和低k层外,不支持早期对铜金属化和石墨烯金属盖的干刻蚀的评论;看来EUV pattern、创新的缩放屏障/衬垫和铜回流已将电阻值的变化降至最低。

DTCO(Design-Technology-Co-Optimization,设计技术协同优化)的一些特性,如 gate-contact-over-active 和“unique diffusion termination(某种形式的单扩散中断?)与“主要设计规则的智能缩放”相结合,以使芯片尺寸减少35%~40%,尽管这是基于具有60%逻辑、30%SRAM和10%IO/模拟内容的移动SoC设计。

EUV栅极pattern也有助于减小SRAM单元大小、DIBL和Vt的变化(下表1)。

下面所示的七个Vt中,极低Vt(eLVT)在7-nm的范围内提供25%的峰值速度,3-fin标准单元允许HPC额外提高10%的性能(图9)。我认为这将是我们第一次看到平台文件中提到的3-fin单元,除了通常被引用为特定节点处最小SRAM的1-1-1 SRAM单元(在本例中为0.021μm

2

)。

图9 eLVT晶体管的峰值速度比7nm提高了25%,比3-fin标准单元的性能提高了10%。

还有其他可用的SRAM单元,如图10所示;超低漏电(ULHD)单元可用于提高功耗效率,而高速高密度(HSHD) SRAM可以在速度允许的情况下尽可能多地替换HC SRAM,从而最大限度地减少约22%的面积。HD单元的蝶形曲线显示低至0.3 V的工作电压。

图10 ULHD、HD和HSHD单元的泄漏电流与单元电流以及HD SRAM的蝶形曲线

图11 超高密度MiM电容器

通过最小化瞬态电压降,Fmax提高了4.2%,在CPU测试芯片中Vmin降低了约20mV。

你会注意到,大多数信息涉及性能和通用技术的进步,如EUV和DTCO——没有真实的数字,也绝对没有图片。这让我们这些技术发烧友感到失望的是,台积电没有给出任何物理细节,比如fin、CPP和metal pitches。

为了弥补这一点,以下是今年早些时候,有人给出了一系列 的估算值:

尽管他额已将其MxP更新为28 nm,但CPP的推测略有不同,分别为50和48 nm,最小金属间距为30 nm。N7处的最小fin间距为30 nm;如果我们从EUV图像中估算出的标准单元高度为175 nm,并广泛地假设它是2 + 2(N fin+ P fin)个单元,则其高度可能为7 fin。还假设了栅极接触过度激活,允许在NMOS和PMOS之间使用一个fin片间隔,以及两个分隔上下单元的共享fin片间隔。175/7提供25纳米fin片间距,17%收缩,并能与SAQP或EUV一起使用。

图11 超高密度MiM电容器

通过最小化瞬态电压降,Fmax提高了4.2%,在CPU测试芯片中Vmin降低了约20mV。

你会注意到,大多数信息涉及性能和通用技术的进步,如EUV和DTCO——没有真实的数字,也绝对没有图片。这让我们这些技术发烧友感到失望的是,台积电没有给出任何物理细节,比如fin、CPP和metal pitches。

为了弥补这一点,以下是今年早些时候,有人给出了一系列 的估算值:

尽管他额已将其MxP更新为28 nm,但CPP的推测略有不同,分别为50和48 nm,最小金属间距为30 nm。N7处的最小fin间距为30 nm;如果我们从EUV图像中估算出的标准单元高度为175 nm,并广泛地假设它是2 + 2(N fin+ P fin)个单元,则其高度可能为7 fin。还假设了栅极接触过度激活,允许在NMOS和PMOS之间使用一个fin片间隔,以及两个分隔上下单元的共享fin片间隔。175/7提供25纳米fin片间距,17%收缩,并能与SAQP或EUV一起使用。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2253期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

“芯”系疫情

|传感器

|IGBT

|

存储

|

氮化镓|英飞凌|中美贸易|半导体股价|芯片测试

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie

图11 超高密度MiM电容器

图11 超高密度MiM电容器