[原创] 芯片的3D化

2020-03-15

22:01:14

来源: Sophie

摩尔定律遇到发展瓶颈,但市场对芯片性能的要求却没有降低。在这种情况下,芯片也开始进行多方位探索,以寻求更好的方式来提升性能。通过近些年来相关半导体企业发布的成果显示,我们发现,芯片正在从二维走向三维世界——芯片设计、芯片封装等环节都在向3D结构靠拢。

当先进工艺从28nm向22nm发展的过程中,晶体管的结构发生了变化——传统的平面型晶体管技术(包括体硅技术(Bulk SI)和绝缘层覆硅(SOI)技术等)的发展遇到了瓶颈,为了延续摩尔定律,拥有三维结构的FinFET技术出现了。

在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。在FinFET的架构中,闸门成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的闸长。

2011年5月英特尔宣布使用FinFET技术,而后台积电、三星也都陆续采用FinFET。晶体管开始步入了3D时代。在接下来的发展过程中,FinFET也成为了

14 nm

,

10 nm

和

7 nm

工艺

节点

的主要栅极设计。

FinFET是

胡正明

教授基于DELTA技术而发明的,由于FinFET技术为半导体的创新带来了新契机,国际电子电气工程学会(IEEE)授予了胡正明2020年IEEE荣誉奖章,IEEE称其获奖是“开发半导体模型并将其投入生产实践,尤其是3D器件结构,使摩尔定律又持续了数十年。”

2015年曾有报道称,FinFET未来预期可以进一步缩小至9nm。发展至今,我们也看到,FinFET技术仍然还被用于7nm中,但从市场发展中看,FinFET技术还没有走到尽头,根据台积电2019中国技术论坛上的透露的消息显示,台积电在今年第二季度量产的5nm中,将使用High Mobility Channel FinFET的节点。

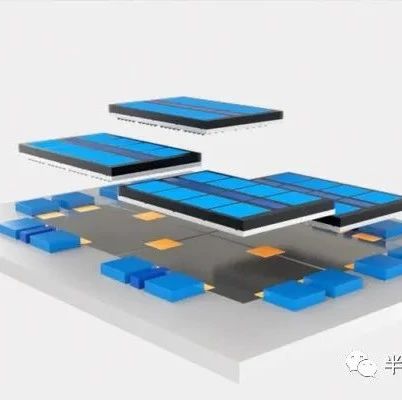

除了晶体管结构走向了3D以外,封装技术也在向3D方向发展。有报道指出,用先进封装技术提供的高密度互联将多颗Chiplet包在同一个封装体内,将是未来的发展趋势。而在这其中,3D封装将产生巨大的影响。

日前,AMD在其2020年财务分析师日发布了其新型的封装技术——X3D封装,据悉,该技术是将3D封装和2.5D封装相结合。AMD称其X3D芯片封装技术将把其MCM带入三维,并将带宽密度提高10倍。

在CES 2019展会上,Intel也正式公布了Foveros 3D立体封装技术,Foveros 3D可以把逻辑芯片模块一层一层地堆叠起来,而且可以做到2D变3D后,性能不会受到损失,电量消耗也不会显著增加。据wikichip的消息显示,第一代Foveros是采用英特尔的

10 nm工艺

引入的,它具有每比特0.15皮焦耳的超低功率,其带宽是类似2.5D

Si中介层的

2-3倍,并且可扩展至3 W至1 kW。

而我们都知道,近些年来,英特尔和AMD之间在CPU上的竞争很是激烈。而伴随着大规模数据中心的发展,让CPU承担所有的计算任务似乎是有些困难,于是GPU逐渐加入了进来——CPU适合日常进行的通用计算,侧重主要在整数计算方面,而GPU在浮点运算和并行处理方面占据巨大优势,如果能够将两者优势结合起来,更强大的处理器就会诞生,因此,AMD和英特尔也先后启动了相关GPU的项目。CPU与GPU如果相集成,也就成为了近些年来备受关注的Chiplet模式。对于Chiplet来说,封装就显得十分重要。而AMD的X3D,英特尔的Foveros 3D,都是发展Chiplet的基础。

CPU和GPU的整合会推动百亿级别的超算的发展,而这或许也会将英特尔与AMD之间的竞争带到另外一个阶段。据外媒报道称,AMD和Intel都赢得了美国DOE百亿级超级计算机的合同。

除此以外,台积电也在积极发展3D封装业务。据相关报道显示,2019年4月,台积电完成全球首颗3D IC封装技术,预计2021年量产。业界认为,台积电正式揭露3D IC封装迈入量产时程,意味全球芯片后段封装进入真正的3D新纪元,台积电掌握先进制程优势后,结合先进后段封装技术,对未来接单更具优势,将持续维持业界领先地位。

格芯亦投身于3D封装领域,2019年8月,格芯宣布采用12nm FinFET工艺,成功流片了基于ARM架构的高性能3D封装芯片。据相关报道显示,3D 封装解决方案(F2F)不仅为设计人员提供了异构逻辑和逻辑 / 内存整合的途径,而且可以使用最佳生产节点制造,以达成更低的延迟、更高的带宽,更小芯片尺寸的目标。另外,格芯还表示,因为当前的12纳米工艺成熟稳定,因此目前在3D空间上开发芯片更加容易,而不必担心新一代 7 纳米工艺所可能带来的问题。

从数据来看,据相关资料显示,与传统封装相比,使用3D技术可缩短尺寸、减轻重量达40-50倍;在速度方面,3D技术节约的功率可使3D元件以每秒更快的转换速度运转而不增加能耗,寄生性电容和电感得以降低,同时,3D封装也能更有效地利用硅片的有效区域。基于3D封装的种种优势,或许,未来将有更多的玩家参与其中。

伴随着三星、美光、东芝、英特尔纷纷开始投入到3D NAND的生产和研发中来,存储产品也开始走向了3D时代。在这些厂商发展3D闪存的过程当中,也衍生了一些新的技术,来助力其闪存产品向3D方向发展。其中,就包括了三星的V-NAND、东芝的BiCS技术3D NAND、英特尔的3D XPoint等。

三星在3D NAND闪存上首先选择了CTF电荷撷取闪存(charge trap

flash

,简称CTF)路线,相比传统的FG(Floating Gate,浮栅极)技术难度要小一些。最终,三星量产的是VG垂直栅极结构的V-NAND闪存,目前已经发展了六代V-NAND技术。据三星官方消息显示,新款 V-NAND 运用三星电子有的“通道孔蚀刻”技术,向前代 9x 层单堆叠架构增加了约 40% 单元。这是通过构建由 136 层组成的导电模具堆栈,然后垂直自上而下穿过圆柱孔,形成统一的 3D 电荷撷取闪存 (CTF) 单元实现的。

东芝方面,东芝的BiCS闪存是Bit Cost Scaling,强调的就是随NAND规模而降低成本,号称在所有3D NAND闪存中BiCS技术的闪存核心面积最低,也意味着成本更低。此外,铠侠今年推出的UFS 3.1嵌入式Flash闪存芯片,同样是基于东芝BiCS 3D存储技术打造,设计容量包括128GB、256GB、512GB和1TB,主控和闪存都按照规范要求封装在11.5 x 13mm的尺寸之内。去年12月,铠侠还宣布,其已开发出一种名叫“Twin BiCS FLASH”的新式半圆形 3D 存储单元结构。据悉,与传统循环设计的电荷陷阱单元相比,铠侠首创的这种半圆形 3D 浮栅单元结构,具有更大的编程 / 擦除窗口和斜率,且单元尺寸做到了更小。

而SK海力士方面,则在去年6月宣布了其关于4D NAND的进展。据相关报道显示,SK海力士将在世界上首次开发和量产128层1Tb级的TLC(Triple-Level cell,三层单元格)4D Nand闪存。据悉,在占据NAND市场85%以上的TLC产品中,SK海力士是第一个推出1Tb级产品的公司。

3D XPoint则是由

英特尔

和

美光科技

于2015年7月发布的

非易失性存储器

(NVM)技术。英特尔为使用该技术的存储设备冠名Optane,而美光称之为QuantX。2019年初,英特尔和美光在3D存储芯片市场上的合作走到了尽头。在3D Xpoint技术上,英特尔率先在2017年完成了3D Xpoint的商业化,推出了傲腾,而2019年11月,美光也终于拿出了自己的QuantX。而根据最新的一些消息来看,英特尔下一代采用3D XPoint的产品或许将要延后发布。根据DOIT的报道显示,在英特尔最新的年度报告中显示,英特尔或将从美光购买3D Xpoint芯片。

此外,长江存储也在3D NAND上有所突破,并推出了其独特的Xtacking技术。据相关报道显示,传统3D NAND架构中,外围电路约占芯片面积的20—30%,降低了芯片的存储密度。随着3D NAND技术堆叠到128层甚至更高,外围电路可能会占到芯片Xtacking技术将外围电路连接到存储单元之上,从而实现比传统3D NAND更高的存储密度。据悉,长江存储的64层3D NAND闪存产品将在2020年进入大规模量产,此外,长江存储还将在今年跳过96层,直接投入128层闪存的研发和量产工作。

芯片从二维走向三维的过程中,出现了很多新技术,这些新技术的出现,不仅突破了某个行业内的瓶颈,也促进了半导体产业的继续创新。同样,在技术变革的过程中,半导体企业也要面临着新的竞争,这种竞争也为新进玩家带来了发展壮大的机会。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2249期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

“芯”系疫情

|ISSCC 2020

|国产芯片

|半导体股价

|

存储

|

Chiplet|氮化镓|高通|华为

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie