一文看懂CMOS集成门电路

-

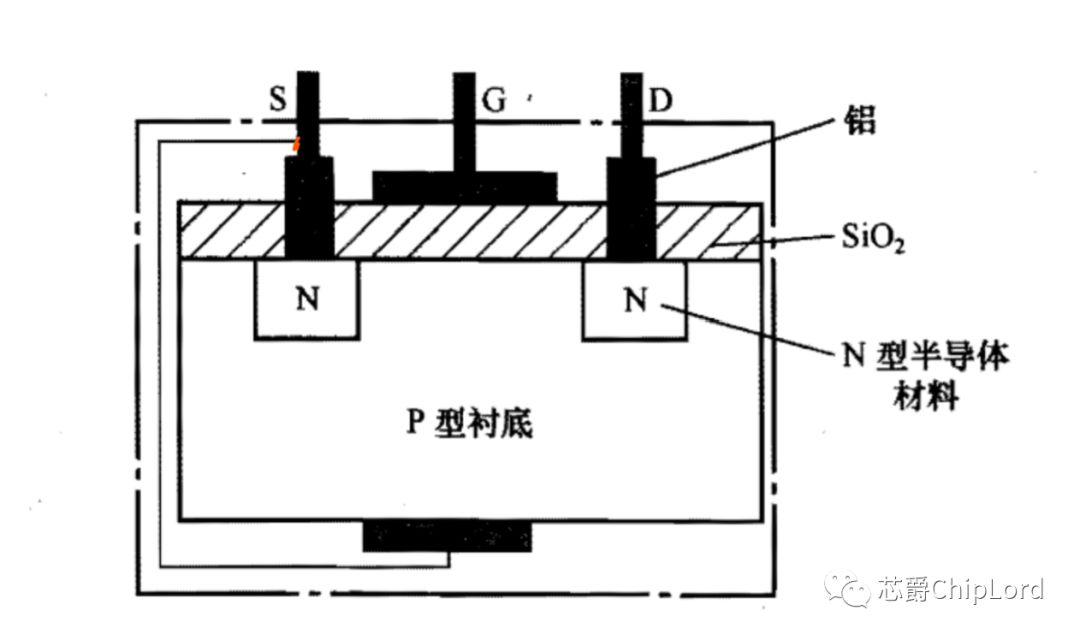

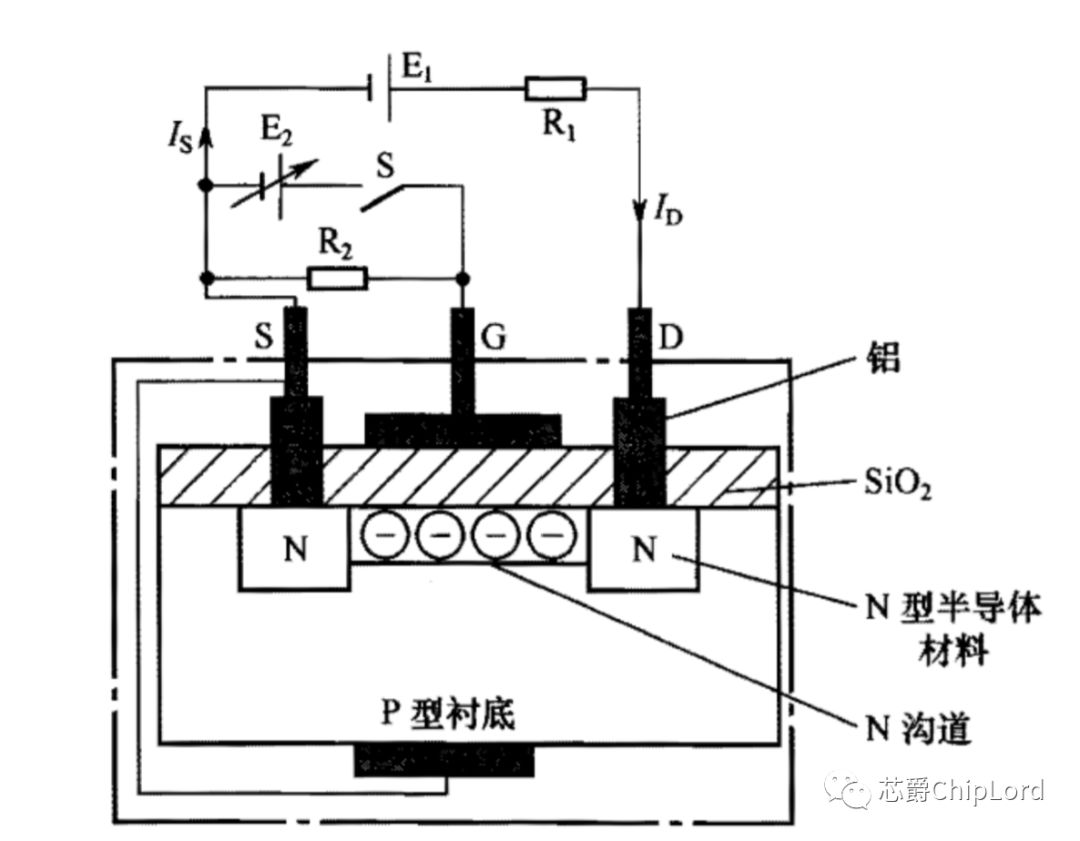

G, S极之间未加电压时,D, S极之间没有沟道,电流为0; -

G, S极之间加上开启电压后,D, S极之间有沟道形成,D, S极之间有电流

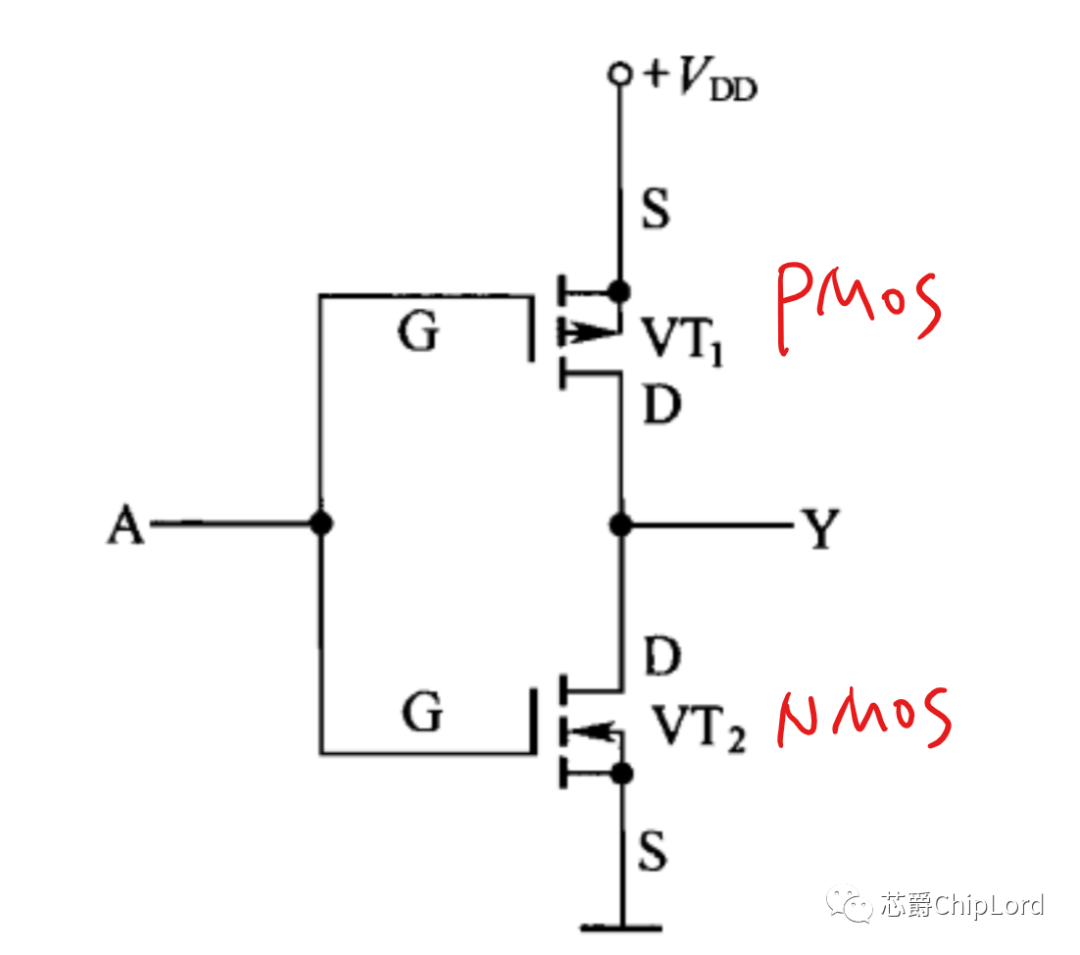

CMOS非门电路

-

当A端为 高电平 时,VT1 PMOS管截止,VT2 NMOS管导通,Y端输出为 低电平 ,也即A=1,Y=0;

-

当A端为 低电平 时,VT2 NMOS管截止,VT1 PMOS管导通,Y端输出为 高电平 ,也即A=0,Y=1。

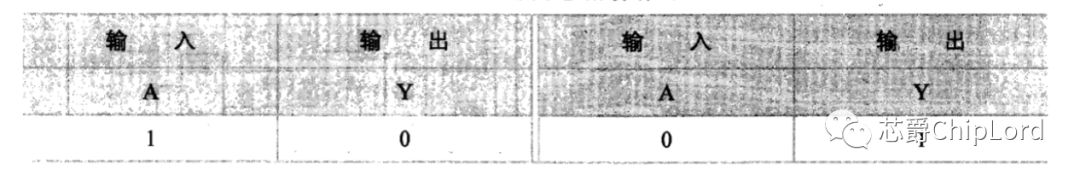

非门真值表

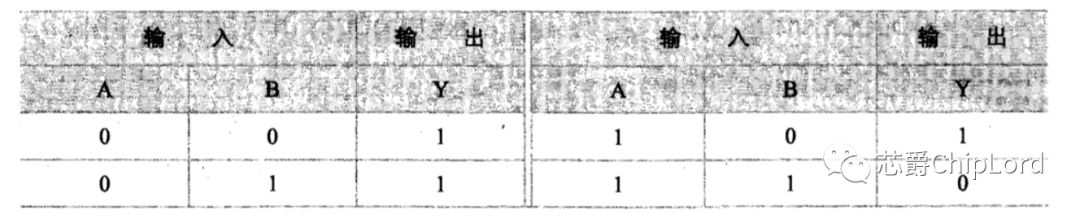

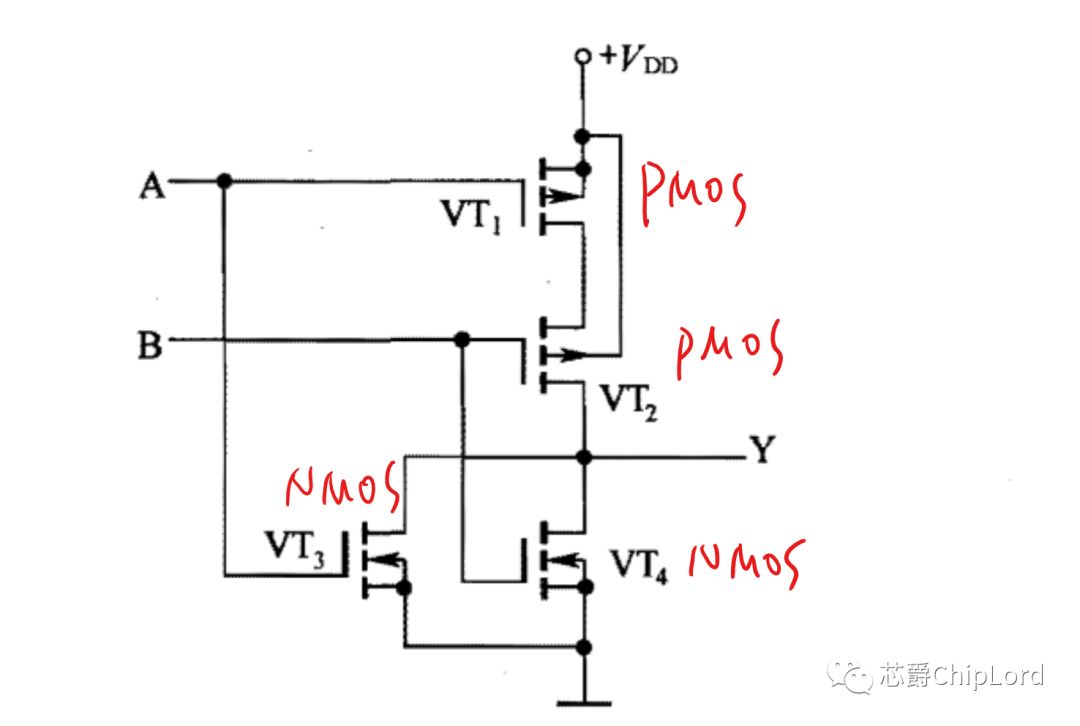

然后介绍 与非门 ,其电路结构图如下:VT1,VT2为PMOS管,VT3,VT4为NMOS管。

-

当A,B端均为高电平时,VT1 PMOS,VT2 PMOS截止,VT3 NMOS,VT4 NMOS导通,Y端为低电平,即A=1,B=1时,Y=0;

-

当A,B端均为低电平时,VT1 PMOS,VT2 PMOS导通,VT3 NMOS,VT4 NMOS截止,Y端为高电平,即A=0,B=0时,Y=1;

-

当A端为低电平,B端为高电平时,A端低电平使VT2 PMOS导通,VT3 NMOS截止,B端高电平使VT1 PMOS截止,VT4 NMOS导通,所以Y端输出高电平,即A=0,B=1时,Y=1;

-

同理,当A端为高电平,B端为低电平时,输出端Y=1。

-

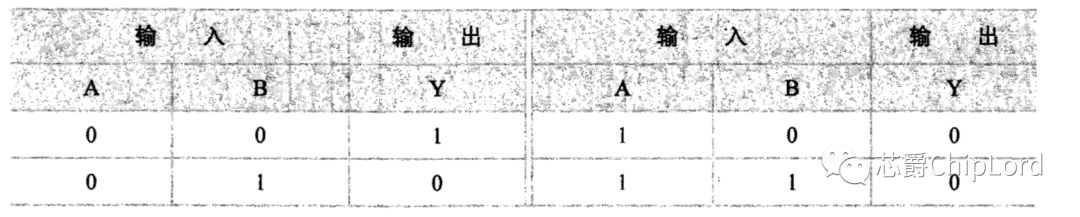

当A,B端均为高电平时,VT1 PMOS,VT2 PMOS截止,VT3 NMOS,VT4 NMOS导通,Y端为低电平,也即A=1,B=1时,Y=0;

-

当A,B端均为低电平时,VT1 PMOS,VT2 PMOS导通,VT3 NMOS,VT4 NMOS截止,Y端为高电平,也即A=0,B=0时,Y=1;

-

当A端为低电平,B端为高电平时,A端低电平使VT1导通,VT3截止,B端高电平使VT2截止,VT4导通,由于VT2截止,VT4导通,Y端输出低电平,也即A=0,B=1时,Y=0;

-

同理:A端为高电平,B端为低电平时,输出端Y为0。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2241期内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

“芯”系疫情 |ISSCC 2020 |日韩芯片 |华为 | 存储 | 氮化镓|高通|康佳

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英伟达,又挖了一道护城河

- 2 江波龙全球最小尺寸eMMC,为AI穿戴设备“减负”

- 3 Solidigm宣布与博通拓展大容量SSD控制器在AI领域的应用合作

- 4 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来