Ampere发布业界首款80核服务器处理器

2020-03-04

17:13:42

来源: Sophie

来源:内

容由半导体行业观察(ID:icbank)翻译自「t

he nextplatform

」,谢谢。

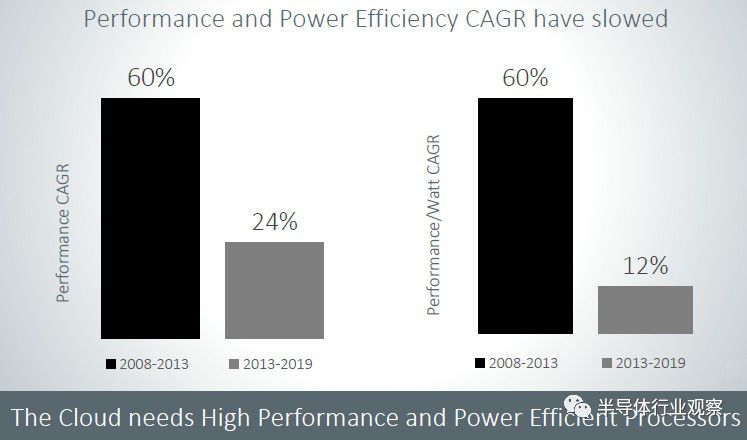

在信息技术史上的这一时间点上,还没有办法推出让超大规模生产者和云构建有吸引力的新处理器。但是,如实是针对这些客户设计的芯片,则完全是另一回事。

而这正是由前英特尔总裁雷尼·詹姆斯(Renee James)领导的,并得到私募股权公司凯雷投资集团(Carlyle Group)的大力支持的Arm服务器芯片新贵制造商Ampere Computing所在专注的。据介绍,他们正在借助其“ Quicksilver” Altra系列处理器实现这个目标,如今,这些品牌已被更全面地展示和品牌化。

复苏的AMD很大程度上已经能够在数据中心再次站稳脚跟,这主要因为其Epyc服务器芯片能满足这些超大型计算机和云构建者客户的特定需求,由于这些公司每年安装的服务器数量众多,为此它们有机会更快地发展。人们普遍认为,芯片制造商高通公司(Qualcomm )几年前在谷歌的鼓励和支持下,携带其Centriq系列芯片杀进Arm服务器市场。这家G字头公司还通过OpenPower Foundation支持了IBM的Power处理器,以此给英特尔施加压力。在过去十年中,英特尔一直垄断数据中心计算技术市场,其高毛利率足以证明这一点。

高通公司(Qualcomm)和之前的Broadcom和Samsung一样起始雄心勃勃,但最后却于2018年5月退出了Arm服务器业务,这间接是的Marvell凭借其ThunderX2系列成为数据中心计算的Arm芯片的主要供应商。但是他们已经好几年没有更新其芯片了。但是正如我们在12月报道的那样,到2020年,他们将图慈湖一款基于7纳米制造工艺的ThunderX2,那就意味着Marvell发布产品的节奏将是两年。而AWS(Amazon Web Services)则以其自己的“ Graviton”服务器芯片成为年度典范。

相反,Ampere Computing将变得更加紧迫,他们回到每年更新的节奏,这是多年以来,英特尔一直在计算机业务中脱颖而出的重要原因,因为这样的话其竞争对手在玻璃屋的时候就可以被淘汰,但坦率地说,即使英特尔服务器芯片大幅滑坡,他们仍然赚钱,这是我们逆序面对现实:如果是您,您将做得和英特尔一样。自从2010年大萧条消退以来,服务器芯片制造商一直在追逐英特尔,直到现在英特尔才感到火热眉毛,以至于不得不重新调整“ Cascade Lake” Xeon SP产品线以使降价看起来像是在进行改造。

今天,我们不打算深入了解Ampere Computing 的整个历史,但是需要进行一些简短的回顾。该公司成立于2018年春季,旨在追逐超大规模生产者和云计算制造商市场,而对现有X-Gene 3设计进行了调整的Skylark芯片则被早期客户所掌握。随着2019年临近尾声,我们与Ampere Computing 取得了联系,以了解下一代Quicksilver处理器的市场定位以及未来的发展方向。今天,Quicksilver芯片获得了Altra品牌名称和提要以及Quicksilver器件以外的这种和未来的Altra芯片的速度和设计理念都在泄露。

我们已经知道,Quicksilver芯片将具有80个内核,这是一个很大的数目,并且不会使用由Applied Micro创建并由Ampere Computing针对eMAG 1芯片进行调整的本地X-Gene内核的变体,据闻,这个芯片有可能是基于Arm Holding的Neoverse N1平台中使用的“ Ares”内核设计。Quicksilver芯片使用Ampere自己的网状互连进行裸片上通信,它是单片裸片而不是小芯片设计,该设计使用台积电的7纳米工艺制造。

AMD拥有PC芯片业务,因此毫不奇怪,它将位于将插槽内的多个芯片组合在一起的小芯片设计的前端。但是,由于螺片的延迟时间和制作封装的复杂性,这需要付出一些代价。

James告诉《The Next Platform》说:“我认为关于小芯片还是单片芯片的决定的向量分为两个部分。”。“一个是成本,如果允许成本引导,您可能会走到错误的地方;另一个是性能,如果您对设计保持谨慎,并且性能是您的目标,那么只要您能做到,您就将一头雾水,知道自己永远不可能。分解的方式几乎与决定分解的方式一样重要。并非所有的小芯片都是相同的,并且具有许多设计,人们进行分类的方式可能最终无法实现所需的可伸缩性和性能。因此,您必须重新设计。从整体的背景出发,您希望Ampere的团队是高效的设计师,而性能是我们的最高水准。我们了解了分解的必要,并且我们有一个多芯片路线图,但是我们想对此保持精明而不是匆忙。而且我认为,考虑到Altra芯片的性能和流片的顺利,我认为这最终是一个明智的决定。当我们沿着这条路走时,在AMD和业界人士看来,这并不是一个明显的决定。因为这这听起来很恐怖。”

好消息是,如果Ampere Computing能够获得更高的性能以及确定性的性能,它可以为此收取额外的费用,或至少比原本可以收取的费用更高。

现有的Ares N1内核具有64 KB的四路L1指令高速缓存和64 KB的四路L1数据高速缓存以及具有512 KB或1 MB的专用L2高速缓存。N1内核具有四个全宽(four-wide)前端,以及一个具有十一级指令流水线(pipeline),并包括三个64位整数单元和一对128位SIMD单元。从技术上讲,它是一种超标量微体系结构(superscalar microarchitecture ),具有乱序执行能力。

在许多其他方面,Ares N1都是非常标准的RISC处理器。整数单元支持8位INT8指令,而SIMD单元则支持半精度或16位FP16浮点指令,这对于机器学习推理工作量都很重要。Ampere产品高级副总裁Jeff Wittich表示,Ampere Computing将在未来处理器中支持Google FP16的bfloat16变体。Arm Holdings于去年9月在其架构中添加了bfloat16,但实现尚需时日。

那11级流水线可以访问1 MB L2缓存,如果使用512 KB L2缓存,则流水线将降回9级以平衡所有缓存。Ampere Computing正在使用具有1 MB L2高速缓存的更深层次的流水线。这些专用缓存直接链接到内核,并有助于提高每个内核的性能。Ampere Computing公司正在整个shebang上封装32 MB的L3高速缓存,尽管尚不清楚该高速缓存的实现方式——以高度分布的方式跨越网格,或以较大块的分段方式在网格边缘。

“现代云需要可预测的高性能,以提供跨平台的扩展性:内核,内存,I / O以及所有内容,,我们需要能效和密度,” Wittich解释说。“我们专注于整数性能,高内核数,大缓存,非常强的服务质量,高I / O和内存带宽所有这些,因此,我们将成为在容器中部署任何内容的理想选择。作为一种功能的微服务是当今云中的部署方式,这与在企业数据中心中运行一个大型整体应用程序大不相同。从性能的角度来看,单线程核心是如此重要,因为它们提供了更好的隔离性和更小的攻击面。”

Quicksilver内核的体系结构处于Armv8.2 +级别,这意味着Ampere Computing正在吸收Armv8.3和Armv8.4的某些功能,这些缓解措施只是一个示例。Quicksilver芯片所没有的,这也是Ampere Computing似乎并不敢兴趣的,那就是支持同时超线程。而且,尽管超线程(通常被称为Intel的SMT风格)在提高效率方面有一些好处,但它也带来了成本,即与两个核心实现相比,两个或多个虚拟线程的性能本质上不确定性高。

Ampere Computing线程在内核方面占有重要地位,因为它消除了那些嘈杂的邻居(neighbor)问题,这些问题使以线程为基础进行检查的特定线程的指令执行时间更长。是的,打开SMT2(每个内核有两个线程)或SMT4(每个内核有四个线程),通过计算机可以完成20%或30%的工作,但是完成每一工作都需要更长的时间,并且由于其他工作会干扰,因此也很难预测每次运行的完成时间。

“我们确保所有内核都可以以相同的持续Turbo频率运行,因为虽然有时90%的CPU空闲,但在单个内核上运行非常高的时钟是有意义的,但这并不是云通常运行的方式”。“如果90%的CPU处于空闲状态,那么您将遇到问题,并且操作方式出了问题。而且,如果这只是一种中间状态,您的服务器在几分钟内大部分时间处于空闲状态,则您实际上并不想提高频率,因为几分钟后,当您将所有其他用户引入该设备时,您不会希望频率下降。然后,用户无法弄清楚频率为何不断反弹。一分钟他们的应用程序运行良好,而下一分钟他们的应用程序具有高延迟。

第一代Altra处理器被设计为在全核Turbo模式下以3 GHz的频率运行,并且它没有实现更高的单核Turbo模式,就像Intel的Xeon SP处理器一样。而且,至少我们知道,所有核心Turbo模式都与说没有Turbo模式是一回事,Wittich说,如果客户需要,它有散热空间可以将时钟提升到3.3 GHz。如果您想以这种方式使用Turbo模式。根据激活的内核数量,Quicksilver芯片的功耗范围从45瓦(可能有10个内核)到200瓦(有80个内核)。

如前所述,Quicksilver芯片具有八个存储通道,但是我们现在知道八个存储控制器将支持3.2 GHz的存储速度,而Quicksilver芯片将允许根据需要激活四个,六个或八个存储控制器。内存控制器根据需要在每个通道上支持一个或两个DIMM,并支持带有基于8 Gb或16 Gb内存芯片的四个或八个存储体的存储棒。控制器还支持DRAM节流,以限制内存总线上的数据流量,以根据服务器内部的散热原因根据需要降低其散热(从而降低其性能),并且内存控制器链接到内部Altra网状互连的外围,这样裸片上任何内核之间的网格上的存储延迟都将尽可能保持一致。两路 Xeon SP服务器可以做到这个,但它只有六个内存控制器。每个插槽最多支持4 TB内存。确实,这是一些繁琐而快速的存储。

每个Quicksilver芯片都有两个PCI-Express 4.0控制器,总共提供128条通道的连通性。当两个处理器链接为NUMA样式以共享内存时,将合并64个通道(每个芯片32个)进行NUMA连接,但剩下192个通道来处理外围I / O。这些PCI-Express控制器中的一个可以率先使用CCIX 协议连接多达四个设备(每个设备具有16通道),用作NUMA互连。我们强烈怀疑CCIX链接可同时用于NUMA或加速器,但很明显,如果其中两个被烧毁,则在剩下的一半中将剩下一半的CCIX x16端口,从而在两个芯片之间建立NUMA链接。如您所料,控制器上的x16通道可以分为x8,x4和x2通道,并且所有通道在Quicksilver系列中的所有SKU中均可用。同上,可用于内存控制器选项和内存访问。

“我们所有的处理器SKU都将支持所有I / O和所有内存,” Wittich说。“我们不执行I / O 或内存容量SKUing,我们希望将容量选择交给客户,这样他们就可以进行创新。”

Quicksilver Altra框图上的最后两个块是PM Pro和SM Pro控制处理器,它们遵循Arm Holdings的Server Base System Architecture Level 4规范,并管理服务器,提供安全启动,执行RAS错误报告以及执行电源管理和温度控制。

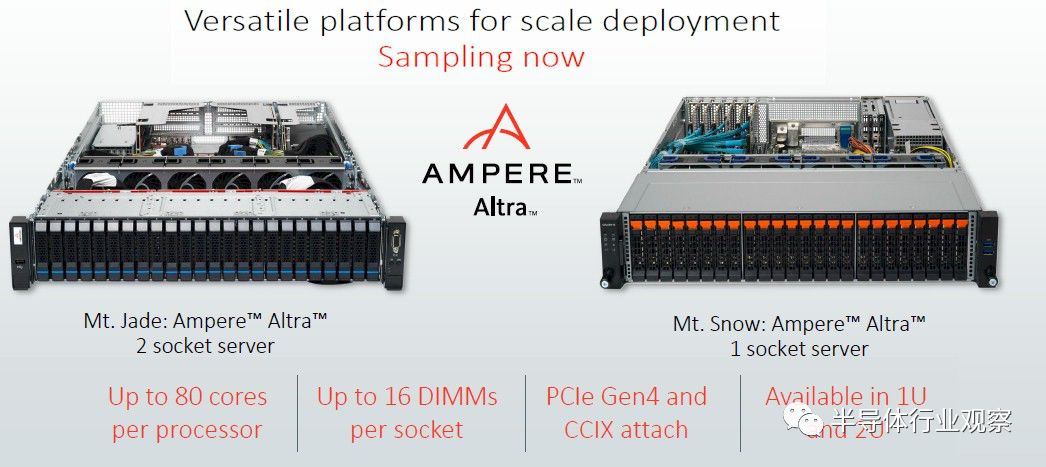

Quicksilver Altra芯片现已向主要的超算和云构建器客户提供样品,而Ampere Computing已开发出两个平台——单路服务器和两路服务器,客户可以将其用作开发和测试平台。

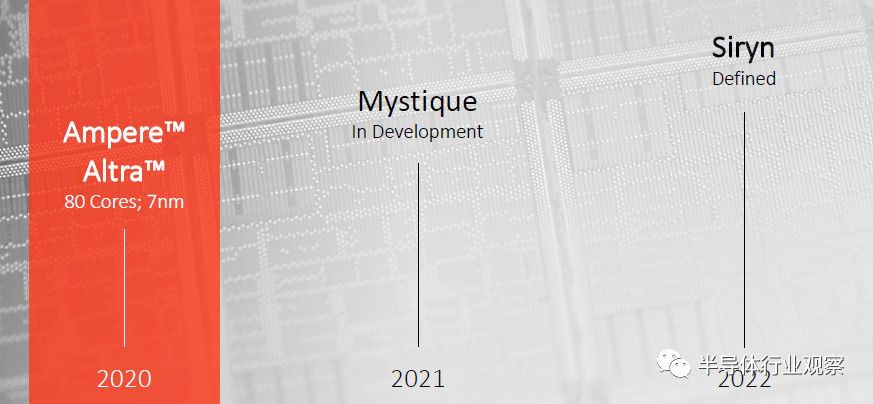

剩下的三件事,以及任何试图在服务器芯片领域获得信誉的新贵都应注意的重要事情:未来芯片的路线图,当前芯片的性能基准以及芯片的价格。我们将分别介绍Quicksilver芯片的性能,但我们尚不了解价格,以下是Ampere Computing的最新路线图:

这与12月份向我们展示的路线图非常相似,不同之处在于,未来的两款芯片现在都有名称,但制造工艺已从图表中删除。但我们认为,“ Mystique”芯片将在2021年推出,并 采用7纳米工艺的修订版,而“ Siryn”芯片将在2022年推出,采用5纳米工艺。正如您从Neoverse路线图中看到的那样:“ Zeus”和“ Poseidon”芯片设计以及它们各自的核心。

Mystique芯片将使用比Quicksilver芯片中使用的N1内核更好Arm内核,因为它们进行了实质性的调整,但目前尚不清楚,我们希望Mystique芯片将与Quicksilver芯片在插槽上兼容,因此服务器制造商不必重新设计插座和主板。出乎意料的是,Siryn将是另一种插槽,可能是同时支持DDR5内存和PCI-Express 5.0外设的插槽。很难说Ampere Computing何时将从单片设计转变为小芯片设计,但我们的猜测是随着收缩到5纳米而发生,也许I / O和内存控制器保持在7纳米,而内核和其他元素收缩到5纳米。时间会证明一切。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2238期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

“芯”系疫情

|ISSCC 2020|日韩芯片

|华为

|

存储

|

氮化镓|高通|康佳

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie