研发收关:高性能处理器核X100完整符合服务器规格要求

2024-05-20

10:55:52

来源: 进迭时空SpacemiT

点击

经过2023年持续的功能开发与性能/频率/功耗优化,进迭时空的第二代 RISC-V 高性能核 X100 的研发工作全部结束,可交付量产。X100 是一款面向服务器CPU芯片研发的RISC-V高性能核,采用4发射乱序架构,通用计算性能 Coremark 达到 7.7/MHz,Spec2k6超过8.2/GHz,在12nm 工艺下频率可达到 2.5GHz ,各项指标均超过设计预期。

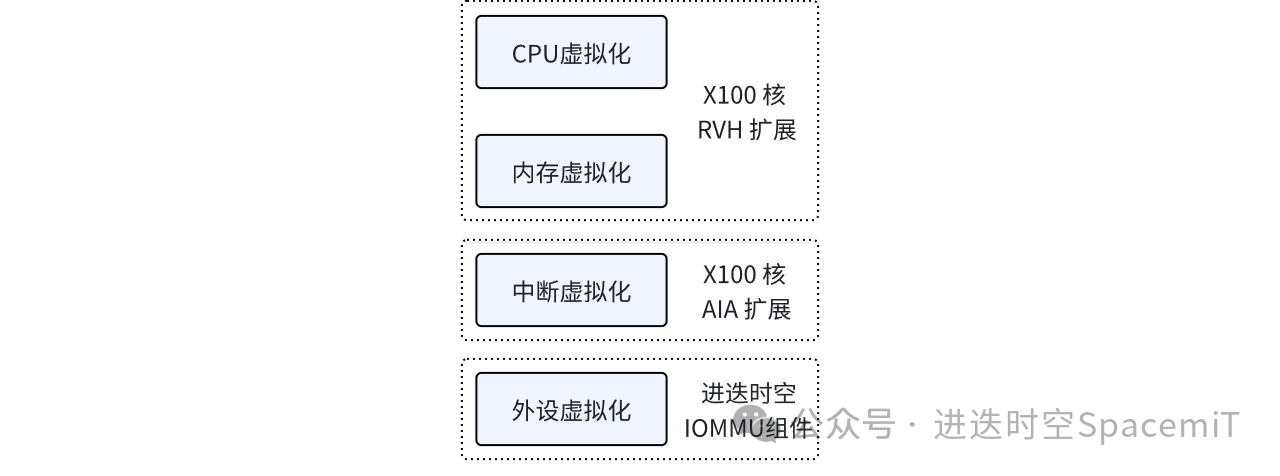

与消费类场景的处理器核不同,服务器CPU除了对处理器核的性能有很高要求外,对虚拟化、安全、RAS、多核互联能力等均有要求,这使得研发一款服务器级别的处理器核相较常规高性能核难度更大。虚拟化是一款服务器CPU的必备功能,虚拟化包括CPU虚拟化、内存虚拟化、中断虚拟化和外设虚拟化,其中CPU虚拟化、内存虚拟化、中断虚拟化均需要在处理器核层面进行支持。

2018年,Intel被爆出震惊世界的Meltdown和Spectre漏洞,使得攻击者可以通过软件方式轻松获得密钥等关键信息并攻入计算机系统,是近年来被披露的最严重的CPU漏洞。抵御Meltdown和Spectre漏洞攻击已成为一款服务器CPU的标准要求。另外,基于隔离的“沙箱”安全技术(类比于Intel的SGX安全技术或者ARM的Trustzone安全技术)也是一款RISC-V服务器CPU必备的。由于服务器CPU要7*24小时不间断工作,长期可靠运行也是一款服务器CPU所必须支持的。

(图源:进迭时空)

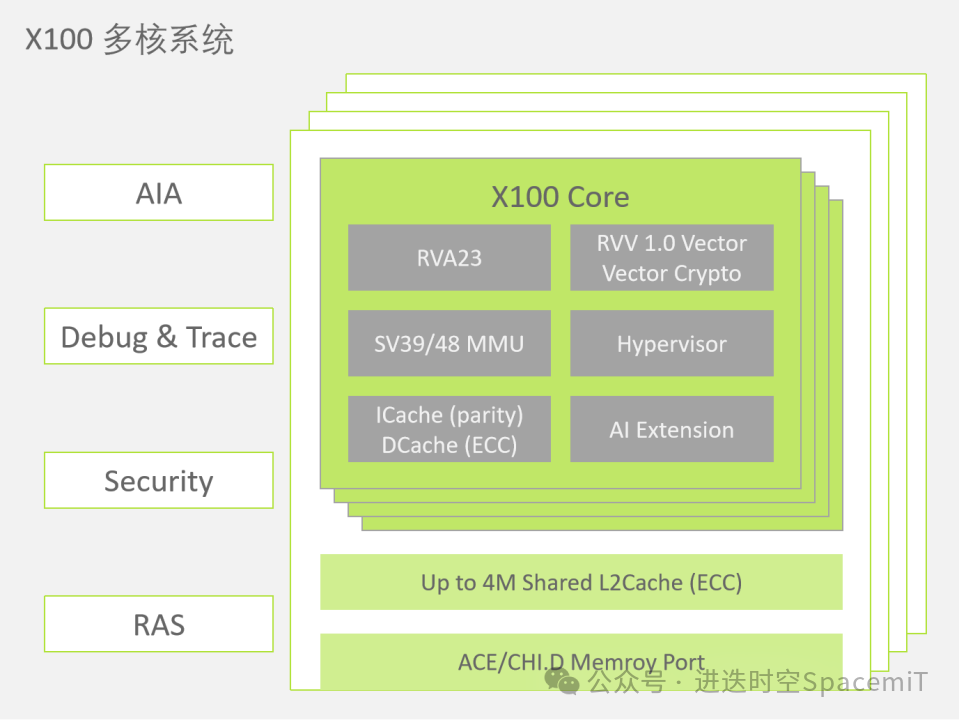

面向RISC-V服务器CPU场景,X100 支持特性如下:

面向RISC-V服务器CPU场景,X100 支持特性如下:

· RV64 指令集,符合目前制定中的 Profile RVA23 标准;

· 支持 RVV 1.0 向量标准,VLEN=256,支持 RV vector crypto 扩展;

· 支持 RVH 虚拟化标准,支持 AIA 先进中断标准;

· 支持安全特性,支持硬件抵抗幽灵、熔断等攻击手段;

· 支持 RAS 扩展,符合 RV RERI 标准;

· 支持 RV debug 调试标准,支持 RV N-Trace 追踪标准;

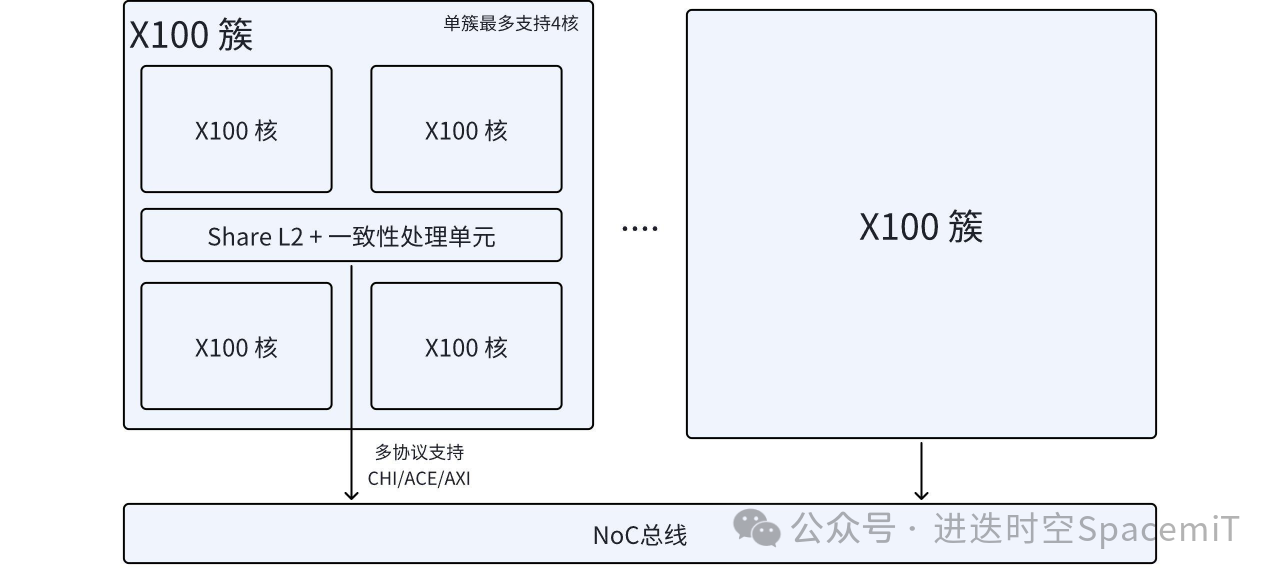

· 支持一致性多核多簇扩展,单簇支持4核,簇原生支持 CHI 接口,典型场景下最大支持 64 核互联。

X100 特性支持

进迭时空 X100 CPU 作为面向服务器场景开发的 CPU 核,不仅在性能和频率上做了大量的优化工作,同时针对服务器等高性能计算领域的应用需求,做了全面的支持与优化。

虚拟化

虚拟化作为服务器必不可少的特性,进迭时空的 X100 核支持 RVH,AIA扩展,可提供CPU虚拟化、内存虚拟化以及中断虚拟化的能力,并且在芯片层面可以配合进迭时空自研 IOMMU 提供外设虚拟化的能力,可以提供完整的虚拟化解决方案。进迭时空基于 X100 CPU 核,也完成了KVM的适配,并在其上成功运行 Linux 虚拟机。同时,经过测试,在虚拟机上的应用程序仍然能维持较好的性能,虚拟机相比物理机的性能仅有约5%的性能损失。

(图源:进迭时空)

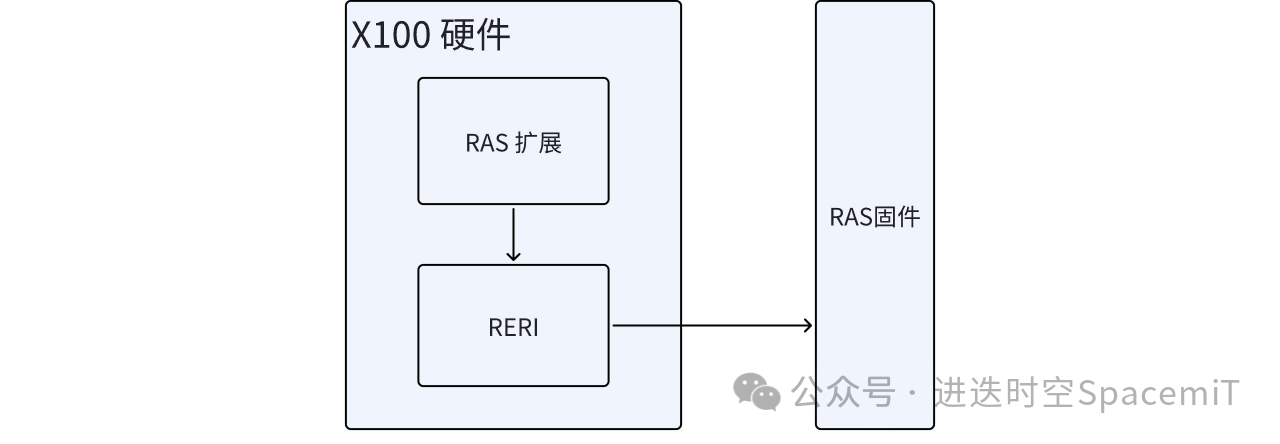

RAS

RAS

为了满足服务器场景的CPU需要能够长时间稳定运行的需要,RAS (Reliability, Availability and Serviceability) 是一个针对服务器领域必不可少的 feature。X100 在规格上支持了内部RAM的检错纠错,包括 ICache, TLB 的 parity 校验,以及 DCache, L2Cache 的 ECC 校验;支持总线传输的校验,支持 CHI 总线的 Data Check 以及 poison 特性;同时通过增加额外的校验以及纠正机制,增加其他非预期情况发生时核的稳定性。通过这些手段,增加整个系统的稳定性。同时,X100 RAS 事件的上报与记录,均符合 RV RERI 规范,使得管理核可以更轻松地维护整个系统的稳定性。

(图源:进迭时空)

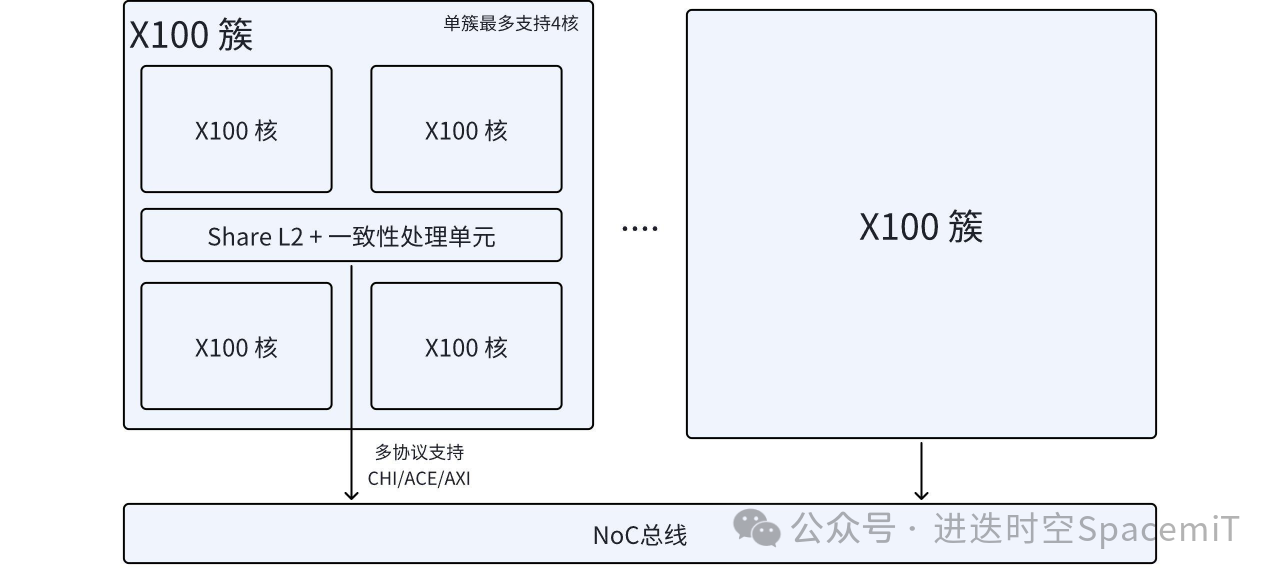

多核多簇支持

X100 可以实现多核多簇的互联,每个簇对外支持 CHI/ACE/AXI 口可配置,内部完全紧耦合接口协议,系统集成时无需额外集成协议转接桥引入的额外延迟和面积开销,可以根据应用场景不同,选择不同的互联接口,典型场景下,最大可支持组成64核的互联系统。共享的 L2Cache 以及簇内一致性维护单元,经过延迟、并行访问能力以及outstanding能力多方面优化,配合最大可支持最高到256bit的总线宽度,给核提供更大的访存带宽和更优的访存性能。

(图源:进迭时空)

安全支持

安全支持

X100 提供了支持TEE安全能力的核心隔离组件PMP/ePMP,允许最高特权模式下的可信固件利用PMP的隔离能力虚拟出多个可信执行环境,同时利用RISC-V AIA中断模型中的中断权限分离机制,允许最高特权下可信固件对中断进行过滤以及转发,从而实现不同执行环境下的中断隔离。除了CPU自身的隔离能以外,X100 还提供核外的安全组件IOPMP用于设备访问的保护。利用RISC-V PMP以及IOPMP等核心隔离组件,在可信固件软件的协同下虚拟出满足服务器安全要求的可信执行环境。除此之外,针对幽灵,熔断等攻击手法,X100 设计了硬件抗攻击的手段,能够由硬件消除潜在的被攻击的风险。

调试与追踪支持

在服务器的应用场景下,由于CPU核数增加,软硬件的调试会变得非常复杂,难以通过简单的手段分析程序流最终定位错误的场景。X100 不仅仅支持了 RV debug 1.0 扩展,同时针对服务器领域调试的痛点,实现了 RV N-Trace 规范,给软件的调试增加了更多手段。

矢量计算增强

X100 支持 RISC-V Vector1.0矢量扩展及向量加密扩展,不仅满足安卓操作系统对RISC-V指令集架构需求,也满足RISC-V服务器规范对指令集架构要求。矢量扩展支持多种数据精度(INT8/16/32/64及FP16/32/64/BF16),单核可提供20GFLOPS浮点算力。矢量加密扩展提供最大256-bit的处理宽度,支持AES/SM4/SHA/SM3/GHASH等算法的高效计算。同时,X100 引入了AI融合算力,基于矢量寄存器实现,提供灵活的算力和编程方式,16核算力可达10TOPS@2.5GHz。

X100 应用场景

由于有着较高的通用计算性能,X100 非常适合用于服务器、自动驾驶、云端AI推理芯片主控等场景。目前,搭载 X100 处理器核,由进迭时空自主研发的服务器CPU芯片也在同步研发中。进迭时空根据自身的应用以及与合作伙伴的深度交流,针对 X100 在高性能场景下的应用,形成了一套完整的高性能 RISC-V CPU 解决方案,可以提供更有性价比的算力,提供更优越的 RISC-V 计算芯片。

进迭时空2024年度产品发布会

2024年4月29日 10:00

扫码关注 不见不散

(图源:进迭时空)

文字|hw、Goku、Jovi、Sun

责任编辑:Ace

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根