台积电称霸晶圆代工市场的四大原因

2019-11-22

14:00:12

来源: 半导体行业观察

来源:内容来自「

天下杂志

」,谢谢。

全球经济一片愁云惨雾,多数金融机构都预期2020年,将是金融海啸以来经济表现最差的一年。

对台积电4万多名员工而言,前景却是一片灿烂,如同11月2日,台积运动会举办时,新竹秋高气爽的艳阳天一般。

「明年,将会是大大成长的一年,」董事长刘德音在司令台致词时,慷慨激昂地说。这句话,第二天出现在各大报的头条。如同呼应刘德音的喊话,外资券商也纷纷上调台积的获利预期。

例如,美商伯恩斯坦证券便在3天后,将台积股价从285元上调到330元,并预期2020年、2021年,这两年每股获利将年均成长20%,远高于过去几年的个位数。美国《霸荣周刊》(Barron's)更在10月18日刊出头条新闻,「台积电夺走英特尔的皇冠」。开头就写,台积电开足马力,这对英特尔而言是坏消息。

为何景气低迷时,台积能大踩油门,在未来两年,每年增加约40%的天文数字投资,甚至可望创造较过去高出2、3倍的成长?台积的经营层看到什么?分析师又看到什么?《天下》采访多位相关人士。归纳出四个致胜关键。

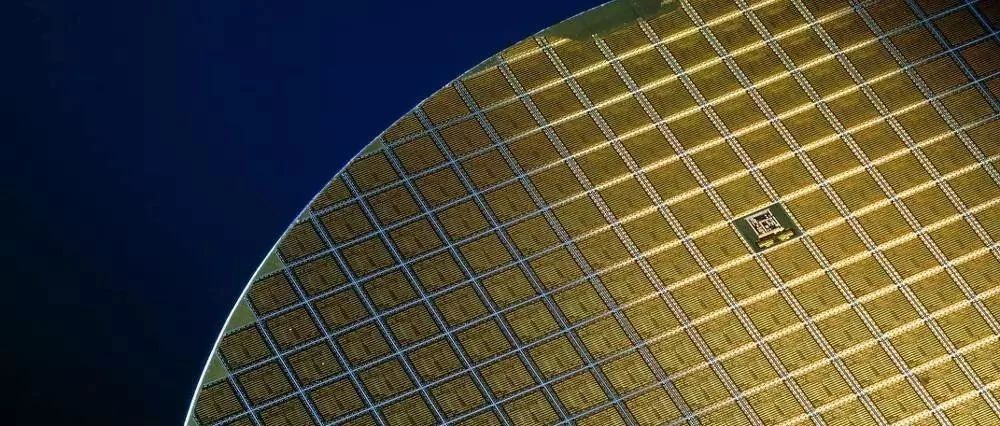

第一个理由,也是最直接的,当然是刘德音在股东报告书写的,成功量产七纳米制程,领先其他同业至少一年。并且,今年6月成功量产业界首个商用极紫外光(EUV) 微影制程,也就是第二版本的七纳米技术N7+。

此事意义深远。因为这是史上第一次,台积在一个重要技术转折时,领先群雄。

上一次重要的技术转折——导入3D电晶体(台积、三星称为FinFET,英特尔称为Tri-gate ),台积足足落后英特尔4年,落后三星半年。这回的极紫外光(EUV)之役,却领先英特尔两年,英特尔要到2021年才会导入。

很多改变历史的关键,往往是一些一开始不被注意的小事。而台积这次得以甩开三星、英特尔,关键其实是几颗小到肉眼无法辨识的「灰尘」。

EUV微影制程,是半导体产业期待已久的「救世主」技术。

目前半导体制程的主流光源是氩氟雷射,波长为193纳米,当电晶体尺度已微缩到几十纳米时,就像用一支粗毛笔写蝇头小字一般,生产起来有点力不从心。这也是近几年,摩尔定律即将告终声浪不断的主因。

极紫外光的波长仅有13.5纳米,这支「超细字小楷」波长已经接近X光,世界上多数物体对它而言都是不透明,连空气都会干扰EUV,因此生产机台的内部得抽成真空。

半导体技术,也因此正式进入皮米(picometer)时代,即纳米的千分之一。EUV只能用镜子反射,由德国蔡司产制的反射镜,得做到史无前例的完美无瑕,能容许的瑕疵仅能是皮米大小。这相当于,如果镜面积有整个德国大,最高的突起处不能高于1公分高。

EUV对生产环境洁净度的要求,更是前所未有的严苛。

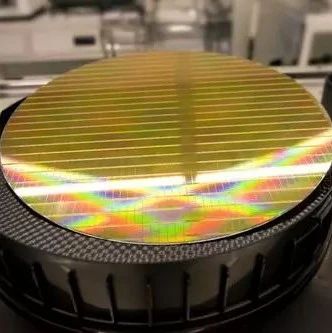

例如,包括台积自制的光罩基板(mask blank),是一片6吋大小的明亮圆镜,造价数百万。上头80层多层膜反射层,跑进去几颗纳米级的灰尘,都会对芯片良率造成巨大影响。

独家供应EUV机台的荷兰商艾司摩尔(ASML)研发副总经理严涛南表示,现在已经从一开始的100颗,慢慢减少到个位数。若从艾司摩尔的曝光机飘下灰尘,更是不能容忍。严涛南表示,技术规格是,每曝1万片晶圆,只能掉1颗,「我们已经非常接近。」

因为控制灰尘太难,EUV量产阶段的最关键技术,是一片薄如蝉翼,厚度只有50纳米,相当于一根头发直径千分之一的透明薄膜。这片「光罩护膜」(pellicle),用在晶圆生产的光罩上头。用来隔绝细微的尘粒。否则,只要一颗尘粒掉到光罩上,可能导致整批芯片作废。

在10月的法说,当分析师群起追问EUV的进度时。台积总裁魏哲家胸有成竹地说,「我们已经准备好了,」并强调,「台积自己生产光罩护膜。」

因为光罩护膜太难做了,处处得挑战物理的极限。要将矽磨到仅有50纳米厚,但EUV照射时,瞬间局部温度会升到数百度。「有点震动,啪,就裂掉了,」一位供应商说。

光罩护膜一旦破碎,瞬间飘出的细微碎屑会污染生产机台,得花7天整理,形同产线停摆1星期。台积供应商透露,三星跟英特尔都卡在光罩护膜这关,导致EUV生产效率迟缓。

一位供应商表示,台积另辟蹊径,在光罩盒加上特殊的防尘设计,意外发现,可以不靠光罩护膜,就达到一定的良率,便大胆量产。「这有可能,」严涛南表示,虽然他不知道台积最新技术突破的细节,但台积很早就投入研发「不用光罩护膜的方案」。技术瓶颈一突破,台积就开始踩油门,大举量产EUV制程。

EUV微影机每台售价超过1亿美元,是人类史上最贵的「工具机」。尽管台积与艾司摩尔都不揭露台积进了多少EUV机台。根据财政部资料,台湾今年向荷兰进口的「半导体生产设备」暴增,光是今年1到10月,就高达33.8亿美元,相当于过去两年全年进口量。

「张忠谋神话」当中,有个经典篇章。时间是在2009年。

当时金融海啸刚过,景气还在谷底,张忠谋刚回任执行长,看好智慧型手机的未来需求,竟大笔一挥,将翌年(2010年)的资本支出,倍增至59亿美元,大盖当时最先进的28纳米产能。在众人惊呼中,奠定台积日后的高速成长。

10月的台积第二季法说,里昂证券分析师便问台积总裁魏哲家,台积今明两年的大手笔扩建,会不会预期产生,与2010年那次扩建28纳米产能类似的荣景吗?

没想到,魏哲家竟意外地切换到「深刻反省」模式。「我知道你在说什么,」他说,「但我认为,台积已经更加聪明……我们这次扩充产能,经过跟顾客的紧密合作与很详细的分析,我有信心,我们不会再犯过去的错误。」

其实,魏哲家会「误解」分析师的问题,背后另有原因。

「这次的扩产,其实台积内部有不同声音,」一位外资分析师解释。28纳米制程是台积史上最成功的制程。但后期因过度扩建、同业杀价竞争,现在反而成了台积最大的累赘。今年上半年毛利率偏低,主要就是28纳米产能利用率「非常低」的拖累。

因为担心如此大规模的投资,会重蹈28纳米「先盛后衰」的覆辙,台积内部规划部门一开始抱持反对意见,「而且一路呈到最上面,」一位分析师说。但最后刘德音、魏哲家还是决定「大踩油门」。另一个重要理由是,竞争者追不上,因为「EUV的技术门槛远远比28纳米的高介电金属闸极(HKMG)要高,」魏哲家说。

但奇怪了,EUV早年可是英特尔一手扶持的技术,2012年,艾司摩尔研发进度延宕,台积还与英特尔、三星三巨头各出102亿元台币资助。大家都出钱出力。为什么台积对该技术特别有信心?

答案是:因为台积对这个梦幻技术量产的实质投入最多。

艾司摩尔的研发副总严涛南是活生生的见证。他曾是台积20多年的研发老将,曾任主导台积EUV研发的资深处长,两年前才加入艾司摩尔。他早在1990年代后期,就跟当时长官林本坚赴美观察EUV的进展。「那时台积不大,但是研发就已经看得很远了,」严涛南说。

接下来,他派一个研究员去比利时的爱美科(Imec)半导体研发机构,参与和艾司摩尔合作的开发案,一开始状况很不乐观,实验机台有大部份时间,都处于故障状态。两年时间,只寄回来20片晶圆。「但是绘制的线图非常漂亮,」所以当时刚回锅的资深研发副总蒋尚义,就批准买一台样机研究。

要让EUV实际上阵量产,难题无数,其中最棘手是如何产生足够强度且稳定的光源。目前的方法,简直像是做高能物理实验一般。在真空环境用超高能量的雷射,射击一滴滴仅有细菌大小的锡滴,锡滴会瞬间气化,变成高热的电浆,同时产出EUV光线。

整个反应过程,浪费许多能量,因此最后输出功率极低,甚至有好几年停留在40瓦,距离250瓦的量产目标甚远。业界不少人因此质疑,EUV永远无法进晶圆厂量产。

2014年9月,是一个分水岭。严涛南牢牢记得那个晚上,他在新竹厂里加班,跟艾司摩尔工程师一起尝试,最后看到90瓦输出功率,大为振奋。

他立刻将结果带到10月在美国华盛顿举行的业界盛会EUVL Symposium发表,引起台下听众一阵惊呼。为了确认稳定性,研发资深副总罗唯仁立即要求,每天用EUV生产500片晶圆,连续生产1个月。

达成之后,严涛南总算松了口气,EUV量产应该是八九不离十了。

一位业界资深人士分析,三星与英特尔主要生产自家产品,尤其是英特尔处理器毛利率高达70%,可以忍受缓慢的生产速度,因此「英特尔(对EUV)的态度比较保守。」

但是为客户产品代工的台积无法如此,因此全力协助艾司摩尔研发,要提升到每小时125片的量产速度,也就是250瓦的输出功率。

「如果一直只有40瓦,那(台积)就没有戏唱啊,我们就一直push、一直push,」严涛南说,多数艾司摩尔的EUV技术突破,都是千里迢迢地从美国或荷兰,拿到竹科12厂的研发工厂,完成首度量产测试。

尽管如此,一个封装大厂主管透露,台积的EUV版7纳米虽已量产,但良率其实不佳,只有50%左右,形同切割出来的芯片,两片只有一片能用。这也是台积7纳米产能吃紧的一大原因。

因此,台积在今年追加的40亿美元左右的资本支出,其实有15亿用来扩增7纳米产能,其他25亿,才是用在明年第一季就要量产的5纳米产能。

抢不到台积产能,「前阵子很多人跑到三星看,去找备胎,」这位封装大厂主管说,「但是台积老神在在。」

尽管三星「宣称」已在去年底量产采用EUV的7纳米制程,但却因为良率问题。「所以大家看了之后,又回来台积排队,」他表示。

因为记忆体景气低迷,三星近来加码晶圆代工事业。在今年4月发表「半导体愿景2030」,宣布要在2030年达到记忆体之外的半导体业务世界第一的目标,打败英特尔、台积。

三星更随后预告,将跳过5纳米,直接在3纳米制程导入全新的「环绕式闸极结构」(Gate-All-Around,GAA),借着重新设计电晶体底层结构,可让尺度减少45%、性能提升35%、电力消耗减少50%——几乎等于摩尔定律微缩一个世代的好处。

而且,三星公告的量产时间是2021年,竟然比台积3纳米的预定量产时间还早一年。

当真孰可忍孰不可忍。7月份的台积法说,刘德音当众吐槽三星,他指出,台积的5纳米跟3纳米,都是货真价实的「全节点微缩」(full-node shrink),「这跟我们竞争对手的技术蓝图不一样喔,所以你如果比较他们的『3』,其实是跟(台积的)『5』比较接近。」

一位外资分析师解释,刘德音这段话暗示,三星「偷斤减两」,利用换上全新的电晶体结构,效能大幅提升之际,假装再微缩一个世代,称为3纳米,其实实际尺度仅较7纳米微缩一个世代,与台积明年第一季量产的5纳米同一等级。所以台积还是领先三星。

而且,一位台积前任研发主管透露,台积研发GAA结构已有10多年历史。

甚至早在2004年,台积就在半导体业界知名的「国际超大型积体电路技术研讨会」(VLSI)发表论文,公开以GAA技术设计的5纳米电晶体。「只看台积要不要在(3纳米)这时候就拿出来,」这位主管说。

所有高科技公司最大的梦魇,就是所处的领域的技术演进已到尽头,即将进入「传产化」(commoditization)的枯燥地狱,原本落后的追兵会一拥而上,价格一落千丈。例如现在的太阳能、LED。

2016年,当时还担任台积董事长的张忠谋,接受《天下》专访时表示,摩尔定律停止的时间点,可能会在2025年左右,停在2纳米制程。

现在,距离这个「大限之日」只剩6年,台积也已经着手研发2纳米。(延伸阅读:地表最接近工业4.0!台积电两大独门武器首度公开)

在台积运动会后的记者会,《天下》再问心情很好的张忠谋,还坚持他当年的末日预言吗?他笑咪咪地回答,他已经不再预测摩尔定律的结束日期,「这种东西要怎么说呢,就是『山穷水尽疑无路、柳暗花明又一村』。」

刘德音随后补充,台积有信心做到1纳米以下,更重要的是——他举了微软执行副总沉向洋前一周在台湾半导体协会(TSIA)年会的演讲为例,「沉向洋的keyword就是,『在AI的世界,计算能力永远是不够的』(computing power is never enough)。」

「永远不够,」刘德音又强调一次,「这是我们驱动最尖端科技的一个confirmation(保证)。」这其实呼应张忠谋过去的说法,摩尔定律其实是个经济定律,如果市场不愿付钱买最新技术,摩尔定律自然走不下去。

例如,过去一直有人质疑,除了苹果、高通,还有谁用得起、或者需要用昂贵无比的3纳米技术?

但进入AI、5G(AI的通路)的时代,登时「柳暗花明又一村」。答案变成:每一家公司。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2136期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

FPGA

|苹果

|台积电

|射频

|

ASML

|

集成电路

|

存储|晶圆

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie