[原创] 这种创新晶体管架构有望颠覆传统CMOS

2019-10-22

14:00:04

来源: 半导体行业观察

来源: 内容 翻译整理自网络 , 谢谢。

英国晶圆代工厂Semefab生产了一种名为Bizen的新型量子隧穿晶体管和晶圆工艺样品,可以大大缩短交货时间、晶圆面积和工艺层,同时提高速度,降低功耗并提高CMOS的栅极密度。

Bizen是由位于英国诺丁汉的初创公司Search For The Next(SFN)开发的新型晶体管体系结构,其使用了量子隧穿(如下图所示)而不是绝缘栅。 这种结构由双极和齐纳二极管组合而成,它允许在标准CMOS工艺中仅在8层中产生逻辑,而对于传统CMOS晶体管设计,则需要20到30层。 Semefab首席执行官Allan James表示,Semefab在苏格兰Glenrothes生产的1μm制程工艺的Bizen测试芯片将传统CMOS晶体管设计的交货时间从15周缩短到了3周,并且芯片面积是同一工艺下同类CMOS器件的三分之一。

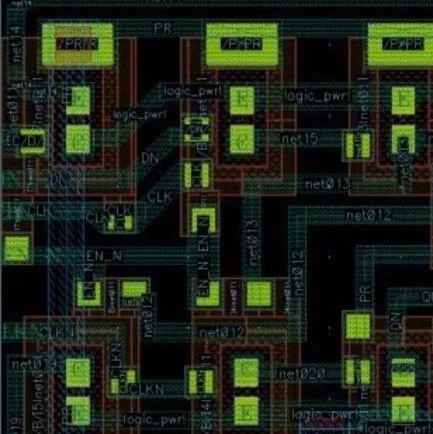

图: (左)单个Bizen晶体管和(中央)CMOS晶体管(请注意,电路的左手用于ESD保护,Bizen版本不需要)创建的NOR门之间的比较,以及TTL等效电路。

Bizen是一种新颖的晶体管结构,本质上是一种PNP器件,其基极通过量子隧道结驱动,并且包括第二个隧道结内部的自偏置晶体管。 目前,这种结构是基于硅的,但是能够迁移到GaN和其他化合物半导体。

量子隧穿技术并不是什么新鲜事物,它已被广泛应用于NOR闪存芯片中。 但是,在过去的两年中,借助Bizen,该技术已应用于逻辑器件,并已由Semefab进行生产、验证。

James说: “事实证明,通过仔细建模,可以将传统的横向和纵向双极结构集成在一起,以整合成Bizen,而不会造成额外的工艺复杂性。 起初我非常怀疑,但是我接受了这个概念并看到了早期的成果,它的确具有颠覆该行业的潜质。 尽管CMOS容易发生闩锁和ESD,但是否有缺陷对CMOS来说并不是什么大问题,而且,CMOS的低功耗特性,已经通过了时间的考验,并且普遍可靠。 但是,CMOS比较复杂,并且与功率集成时更是如此。 复杂性意味着更长的交货时间和更高的成本。 而Bizen恰好能够解决这些问题。 ”

Bizen晶体管结构

如前文所说,Bizen的晶体管具有类似PNP的结构,但基极有所不同。

SFN首席执行官David Summerland说: “这是一种双极机制,而不是像MOSFET那样的单极机制。 它不会像BJT那样直接与基极接触,且不会像MOSFET那样被氧化物隔离。 取而代之的是到基极的隧道结,其中的掺杂很重,使得Bizen——双极稳压管——保留了传统双极处理的优点,但通过使用齐纳量子隧道机制消除了缺点。

SFN公司称,虽然也将Bizen的两个电极称为“集电极”和“发射极”,但其实该结构是对称的,可以在不更改功能的情况下交换这两个端子,因此,可以将它们命名为“阳极1”和“阳极2”。

第二个隧道结(如上图所示,用两条水平线表示)使Bizen偏置,以便在隧道端子开路时“接通”(但不饱和)。 根据Summerland的说法,虽然这表示在操作过程中有连续的电流流到地面,但隧道电流通常仅为2nA ~5nA,他补充说,可以通过包括一个可断开偏置隧道连接的单一结构来引入低功耗“睡眠”模式。

在这种开路条件下,隧道电极将以200-300mV的电压浮在最正的阳极下方(如下图所示),该器件可以在其阳极之间通过20nA~30nA的电流,且这些阳极之间的压降可低至几毫伏。

当Bizen的隧道连接被拉到正极时,两个阳极之间的电流路径将关闭,且器件的隧道端子不会被驱动。

因此,使用Bizen晶体管构建的任何逻辑都是基于电流的逻辑,而不是基于电压的逻辑,并且,除了电阻器或偏置隧道结以外,不需要额外占用空间的的电流吸收器。

根据Summerland的说法,可以使用Bizen晶体管实现任意逻辑功能,并且只需4个工艺光刻掩模(而不是整个工艺的8个掩模)即可实现逻辑芯片(4层–无需金属层),这是因为可以在晶体管内部建立晶体管到晶体管的连接。

如下图所示,右侧黄色部分是Bizen D型主从触发器,在该1μm工艺示例中,仅需8个晶体管,并占45μm x37μm的面积。 不需要金属层。 在相同节点的制程工艺上,根据Summerland介绍的CMOS版本(下图中左侧绿色部分),将需要28~35个晶体管,并占用112μm x37μm的面积。 “从理论上讲,我们可以扩展Bizen制程,目前正在研究当中,” Summerland补充说。

图: 等效触发器电路显示: Bizen晶体管(右)比CMOS MOSFET(左)节省空间

功耗方面,Summerland表示,Bizen的动态功率要低得多,因为它没有与CMOS相关的所有浪费功率的MOSFET栅极电容。

Bizen SPICE模型

SFN团队重写了一系列Bizen的Spice模型。 还有针对Cadence设计流程的完整的物理设计套件(PDK)。 可使Bizen比CMOS的生产速度快80%~90%。

当前的方法允许进行模拟计算,其中电流可以合并,并随着时间的流逝而增长。 在不使用SOI衬底的情况下,芯片可以分为8层。 Summerland说: “很难将功率和逻辑两部分结合起来,如果只是逻辑,它的层数就更少。 我们将在明年第一季度和第二季度发布PJT,我们期望晶圆厂能够采用该工艺。 我们认为该制程的规模将超过1μm,但这尚未得到证明。 我们正在积极地研究一个扩展项目,而我们的仿真结果表明它将会成功。 ”

SFN团队称,8层工艺还可以容纳高达650V的NPN功率晶体管和这些晶体管的基极驱动器。

Semefab与SFN合作,探索在降低智能电源IC工艺复杂性的同时保持对芯片进行编程的能力的方法。 早期,这样的建议被拒绝,因为它们不能满足所需的低掩模数目标。 最终,SFN提出了使用微型反向偏置的齐纳二极管结构的量子隧道效应的想法。 结果表明,经过仔细建模,可以将传统的横向和纵向双极结构的集成设计结合为Bizen,而不会造成额外的过程复杂性。

但是,双极功率晶体管不是有损耗的吗? 对于这个问题,Summerland给予了否定,他认为,MOSFET跨导基于漏极电流的平方根。 他说: “BJT跨导与集电极电流成正比,而跨导与速度有关,除非MOSFET的宽度比长度长得多。 我们相信,Bizen功率IC的开关速度将与IGBT的一样快。 ”

这里,工艺设计套件(PDK)可用于1A和10A功率晶体管。

Bizen模拟模块: 运算放大器和比较器,甚至是模拟计算模块,例如分频器。 在某些情况下避免使用逻辑,从而避免使用相关的ADC和DAC应用程序。 如果采用逻辑,Summerland则使用了结构可预测1μW1μs的模拟除法,而不是大约20条或100条指令周期。

SFN团队预测使用Bizen晶体管和Semefab开发的相关工艺的芯片将在-40至+ 85°C的温度范围内运行,但详细数据需要运行更多的晶圆。

隧道电流受温度影响,但该公司将平衡工艺参数和预期的工作电压(范围为5V至3V,并且在不同的掺杂下可能更低),以达到雪崩和齐纳特性交叉以最小化温度的目的。

Semefab的James表示: “温度系数将与二极管的暗电流泄漏相距‘100万英里’,二极管每7°C就会增加一倍。 ” Summerland补充道: “这要小几个数量级,这就是为什么我们选择隧道电流而不是漏电流的原因。 ”

关于代工准备情况,James说: “Semefab公司现在正在验证PDK,并预测了明年第二季度的Bizen逻辑。 我们已经实现了垂直功率晶体管,尽管我们还没有达到650V。 ”他强调说,他的公司能够将Bizen芯片设计转变为硅产品的速度会相当惊人。 在特征尺寸为1μm时,甚至不必考虑晶圆抛光,可以在两到三个星期内完成。

Bizen芯片何时问世?

综上,Bizen不仅仅是一项理论研究,而且还与基于Glenrothes的芯片制造商Semefab合作,该公司已经在运行Bizen晶圆。 两家公司共同致力于在明年第二季度向潜在客户提供技术演示和芯片样品。

目前来看,Bizen可能会打开老式晶圆厂的逻辑生产之门。 “如果它能被业界采用,鉴于将给定技术节点上的Bizen裸片面积比CMOS逻辑实现的面积要小这一优势,或许能够将摩尔定律时钟倒退10年或更长时间。 Allan James说: “ Bizen成为商业现实还有很长的路要走,我们仍然在学习,但是Semefab和SFN一直在努力工作,以使其取得成功,并可能很快成为现实。 ”

Semefab在苏格兰Glenrothes运行了33年,经营着三个晶圆厂,包括两个MOS /双极工厂(一个在1µm节点处处理100mm晶圆,一个在1µm节点处处理150mm晶圆,步进能力低至0.7µm)。 主要从事MEMS晶圆代工业务。

接下来,还需要晶圆代工厂将进行进一步的Bizen测试,提高集成度并进行进一步的特性描述,包括加速寿命测试。 James说: “目前还没有获得成品率统计数据,但到目前为止,Bizen晶体管在其150mm晶圆上看起来是均匀的,并且随机采样大量器件表明其确实是均匀的。 ”

James表示,各个处理步骤的性质使该技术具有天生扩展到较小节点的能力。 他说: “Semefab计划与另一家苏格兰工厂合作,该工厂具有优良的线宽光刻能力,低至0.35μm,合作可以以在2020年中左右实现可扩展性。 ”

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2105期内容,欢迎关注。

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

AI| 射频 |日韩芯片 |TWS耳机|碳化硅 |华为 | 集成电路 | 制程工艺

回复 投稿 ,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie