台积电市值冲新高背后:这项技术功不可没

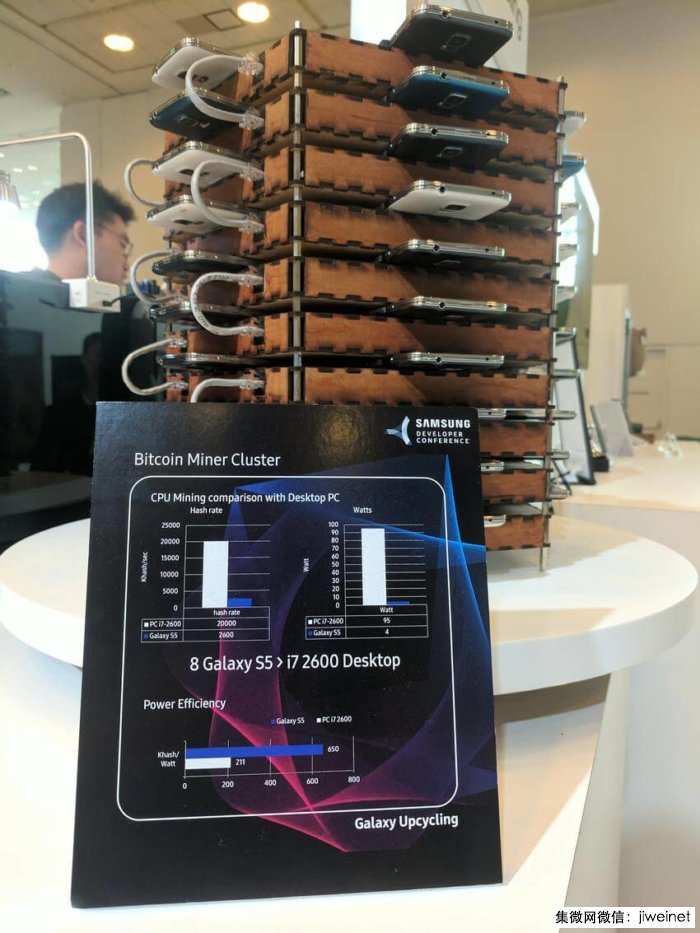

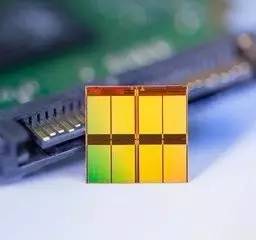

乐高堆叠,小裸芯片组成系统单芯片

Chiplet封装,联发科、AMD也采用

中美角力新战场,忙于建立I/O标准

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2082期内容,欢迎关注。

推荐阅读

★ 芯片级拆解iPhone 11 Pro Max,BOM清单曝光

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

AI| 射频 | 华为 | CMOS |晶圆| 苹果 | 存储 |WiFi 6

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 首次!芯联集成2024年度毛利率转正

- 4 汽车芯片需求激增,南芯科技加速推进“第二增长曲线”