晶体管微缩难上加难,厂商们有何妙招?

2019-09-05

14:49:43

来源: 互联网

点击

来源:内容来自「新电子」,谢谢。

图1 ASML资深市场策略总监Boudewijn Sluijk表示,自动驾驶、5G、AI等新应用推升芯片性能发展。

图1 ASML资深市场策略总监Boudewijn Sluijk表示,自动驾驶、5G、AI等新应用推升芯片性能发展。

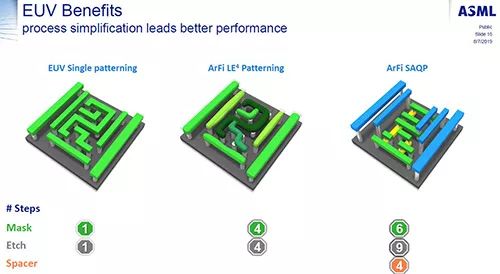

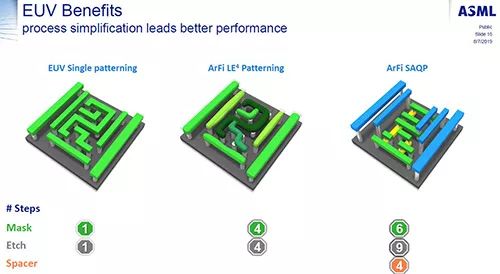

图2 EUV技术可有效减少曝光次数,进而降低成本。资料来源:ASML

图2 EUV技术可有效减少曝光次数,进而降低成本。资料来源:ASML

图3 Lam Research副总裁Yang Pan认为,高级节点发展的重要趋势是Vertical Scaling。

图3 Lam Research副总裁Yang Pan认为,高级节点发展的重要趋势是Vertical Scaling。

人工智能(AI)、自动驾驶、车联网、5G等应用相继兴起,且皆须使用到高速运算、高速传输、低延迟、低耗能的先进功能芯片,10纳米以下的先进制程重要性也与日俱增,同时也成为晶圆代工厂重要获利来源;台积、三星两大晶圆代工厂继实现7纳米之后,皆致力朝5纳米、3纳米发展。然而,半导体制程节点越来越先进,意味着需要更新颖的技术支援以进行加工制造,因此,除了晶圆代工厂外,半导体设备商也相继研发新一代技术。

简化制程EUV扮关键要角

艾司摩尔(ASML)资深市场策略总监Boudewijn Sluijk(图1)表示,VR/AR、自动驾驶、5G、大数据及AI等,持续推动半导体产业发展,为满足各式应用、资料传输,以及演算法需求,芯片效能不断提高的同时,还须降低成本,而极紫外光(EUV)在先进制程中便扮演关键的角色。

图1 ASML资深市场策略总监Boudewijn Sluijk表示,自动驾驶、5G、AI等新应用推升芯片性能发展。

图1 ASML资深市场策略总监Boudewijn Sluijk表示,自动驾驶、5G、AI等新应用推升芯片性能发展。 Sluijk指出,过往采用ArFi LE4 Patterning或是ArFi SAQP进行曝光的话,要实现7nm、5nm,须经过许多步骤。例如用ArFi LE4 Patterning需要4个光罩、4次曝光;用ArFi SAQP需要6个光罩、9次曝光,而EUV只需1个光罩、1次曝光(图2)。采用EUV技术不但可有效简化制程,加快产品设计时程,也因为曝光次数明显减少,因而可有效降低成本,满足芯片设计高效能、低成本的需求,因此,市场对于EUV的需求有增无减。

图2 EUV技术可有效减少曝光次数,进而降低成本。资料来源:ASML

图2 EUV技术可有效减少曝光次数,进而降低成本。资料来源:ASML 据悉,ASML的EUV系统现在可用于7nm生产,满足客户对可用性、产量和大量生产的需求。截至2019第二季季末,半导体界已经有51个EUV系统被建置(包含NXE:33xx、NXE:3400B),而该公司在2019年的销售目标为30台EUV。

据悉,ASML目前已出货11台EUV极紫外光系统,而在第二季再度接获10台EUV极紫外光系统的订单,显示市场对于EUV设备的需求相当强劲。因此,ASML的出货计划将着重于2019年下半年和第四季,而2019年的整体营收目标维持不变。

然而,随着晶圆产能不断增加,ASML也持续推出生产力更高的EUV设备。Sluijk透露,目前EUV系统在晶圆厂客户端每天生产的晶圆数量超过1,000片,而ASML持续强化EUV微影系统「NXE:3400C」的量产效能,不仅在ASML厂内展示每小时曝光超过170片晶圆的实力,在客户端实际生产记忆体芯片的制造条件下,也成功达到每天曝光超过2,000片晶圆的成果,甚至达到2,200片的纪录。另外,ASML也计划在2020上半年推出生产力更高的设备,将NXE:3400C的生产率提升至>185wph。

除提升设备生产量之外,因应未来先进节点,ASML也计划推出全新EUV设备,名称为EXE,不仅拥有新颖的光学设计和明显更快的平台,且数值孔径更高,为0.55(High- NA),进一步将EUV平台延伸至3nm节点以下,扩展EUV在未来先进节点中的价值。

Sluijk说明,此一产品将使几何式芯片微缩(Geometric Chip Scaling)大幅跃进,其所提供的分辨率和微影叠对(Overlay)能力比现有的NXE:3400高上70%。EXE平台旨在实现多种未来节点,首先从3纳米开始,接着是密度相近的记忆体节点。另外,EXE平台有着新颖的光学设计,并具备更高的生产力和更高的对比度,以及更高的生产量,每个小时>185wph,且Reticle Stage比NXE:3400快上4倍;Wafer Stage比NXE:3400快上2倍。

Sluijk指出,该公司的EUV平台扩展了客户的逻辑芯片和DRAM的产品路线图,透过提供更好的分辨率、更先进的性能,以及逐年降低的成本,EUV产品将会在未来十年到达一个经济实惠的规模。

满足芯片设计PPAC需求蚀刻/沉积技术不容小觑

科林研发(Lam Research)副总裁Yang Pan(图3)认为,在高级节点,最重要的趋势是垂直缩放(Vertical Scaling)以满足「功率-性能-面积-成本(Power Performance Area Cost, PPAC) 」的需求,特别是记忆体和逻辑芯片;垂直缩放过去5年彻底改变了NAND产业,目前3D NAND的出货量多于平面NAND(Planar NAND)。垂直缩放的实现须透过沉积和蚀刻中的High Aspect Ratio(HAR)制程实现,而这是该公司所擅长的。

图3 Lam Research副总裁Yang Pan认为,高级节点发展的重要趋势是Vertical Scaling。

图3 Lam Research副总裁Yang Pan认为,高级节点发展的重要趋势是Vertical Scaling。 Yang Pan进一步指出,另一个趋势则是产业对于新材料的需求不停增加。半导体产业对于新材料的需求一向都很强劲,过去几十年来半导体产业探索了大部分的元素,而现今的重大挑战是在每个设备上实现新材料的益处。同时,随着内部连接间距(Interconnect Pitch)变小,薄阻障层(Barrier)、线层(Liner)和种子层(Seed)不能充分缩放,导致Copper Fill的可用体积减少,使得通过电阻和线路电阻大增。因此,须整合新的或是替代性低电阻材料,以满足设备性能和可靠性;但这也是极具挑战性,Lam便透过在介质阻挡层、金属化及其相互作用方面的丰富经验为新一代解决方案提供关键的支援。

同时,为了协助客户实现更快、更便宜的量产,Lam正在利用机器学习和AI使工具变得更加智能化。在现今的半导体制程环境当中,晶圆清洗之间的平均时间是限制蚀刻系统生产力的主要因素。蚀刻制程模组通常需要每月,或有时需每周进行清洗,以保持稳定的效能,并更换因电浆制程受腐蚀的零件。

蚀刻制程模组需要维护和更换消耗性零件,这是既耗时又耗力的工作,因为必须打开腔体、更换零件、清洗,然后再对腔体重新进行认证,这会影响产出并需要复杂的排程作业。为此,Lam与客户合力研发自我维护解决方案,使得设备可以知道何时需更换零件,而且毋须打开腔体即可自动更换零件。此举减少了工具的停机时间,并提高了整个晶圆厂的生产力。

除此之外,当半导体制程进入7纳米、5纳米之时,可说是进入了「原子时代」,以原子级的精度控制制程变化对于芯片功率、性能和产量相当重要,越来越多的应用需要原子层沉积(Atomic Layer Deposition, ALD)和原子层蚀刻(Atomic Layer etching, ALE)减少Within-die和Within-wafer的变异。

另外,先进制程另一个重大变化是引进EUV。Yang Pan表示,为了要继续扩展节点路线图,需要EUV减少边缘放置误差(Edge Placement Error)。每个新的光刻都需要新的抗蚀剂、新的蚀刻制程等来定义图案(Pattern)。当到了5纳米节点及以下时,需要使用EUV进行多次图案(Multiple Patterning)以实现所需的元件尺寸。为此,Lam一直与包括ASML在内的生态系统伙伴合作,提供整体解决方案,像是透过应用原子层蚀刻技术(Applying Atomic Layer Etching)使得边缘粗糙度变得更平滑以改善EUV制程产量。

IC设计新技术纷现缺陷检测需更精准

KLA新技术制程控制解决方案及研发总监Chet Lenox则指出,行动系统单芯片(SoC)的功耗需求、高性能计算(HPC)伺服器以及AI芯片的性能要求都推动了先进设计节点的发展。虽说先进节点提高了单位面积上的电晶体缩放比例,但随之上升的晶圆成本则抵消了大部分的获益。不过从功耗/性能的角度来看,采用先进设计节点制造芯片仍然是值得的。因此,目前看到更多的代工厂采用了7nm节点,并期望5nm和3nm节点的发展也将如此。

过往半导体制造商在领先制程的开发和良率提升中所面临的挑战主要是由关键特征(主动区、闸极和后段制程金属线)的原始间距缩放造成的。然而,随着创新整合解决方案兴起,提高了主动区电晶体密度,而无需太多原始间距的缩放,此外采用新材料也可以持续改善电晶体的性能。

对此,Lenox表示,从检测和量测的角度来看,这些新的整合设计技术协同优化(DTCO)构造和材料改进可能会产生独特和意想不到的缺陷类型,也因而向半导体设备商提出了在之前的节点中从未遇到过的全新量测要求。因此,该公司必须与半导体制造商更为紧密地合作,才得以预测潜在的缺陷模式并预期量测的需求;且该公司的制程控制系统才能够对这些先进的整合技术和材料进行故障排除和监控。

除此之外,另一个KLA目前也在密切关注的领域,则是在图案化制程中使用选择性沉积。业界长期以来一直在包括前段(FEOL)的外延生长和后段(BEOL)的金属封盖等制程中使用选择性沉积,但是新一代的沉积制程可能会拓展并用于结构图案化的制程之中。

Lenox解释,举例来说,如果FEOL触点可以从主动区或是闸极区选择性地「生长」(而不是自上而下蚀刻),并可以连接到中段层(MOL),则极有可能显著地降低EPE相关的良率问题。

另一个重要的趋势是替代记忆体类型应用更广泛,例如在产品中选用自旋移转转矩RAM(STT-MRAM)和相变化RAM(PCRAM)作为非挥发性记忆体。目前市场上已看到这些元件类型所带来的新型整合方案、单元制程类型,以及需要特定检测和量测方法和机台的材料。目前,它们仅仅是后缘节点选项的小众应用。但预计一旦它们能够替代传统逻辑芯片中的高级缓存SRAM,并且在客制的AI训练和介面处理器中被用作记忆体,就会更为广泛地普及。

上述所提到的产业变化衍生了全新的测试需求,为此,KLA近期推出全新的392x和295x光学缺陷检测系统和eDR7380电子束缺陷检视系统,满足先进逻辑芯片、DRAM和3D NAND元件从研发到量产的关键缺陷检测、识别和溯源。

总结来说,芯片微缩不仅伴随着高性能,也带来许多新的设计、测试挑战。也因此,半导体设备业者纷纷针对EUV、蚀刻、沉积等技术进行强化,发展新一代解决方案。

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 MediaTek 发布天玑 8400 移动芯片,开启高阶智能手机全大核计算时代

- 2 探索智慧实践,洞见AI未来!星宸科技2024开发者大会暨产品发布会成功举办

- 3 国产EDA突破,关键一步

- 4 共筑国产汽车芯片未来,中国汽车芯片联盟全体大会即将开启