关于芯片产业的未来,专家是这样看的!

2019-08-12

11:50:30

来源: 互联网

点击

来源:内容来自「科学网」,谢谢。

图1. 2016年远景研讨会上开源硬件便备受关注

图1. 2016年远景研讨会上开源硬件便备受关注

图3. 2019年远景研讨会11位报告人

图3. 2019年远景研讨会11位报告人

图4.ISA指令集、微结构设计、产品三个层次以及对应的三种商业模式

图4.ISA指令集、微结构设计、产品三个层次以及对应的三种商业模式

图5. 三种不同商业模式形成处理器分类

图5. 三种不同商业模式形成处理器分类

图7. 采用三部曲设计方法的DNN加速器案例

图7. 采用三部曲设计方法的DNN加速器案例

图8. MIT Sze教授团队设计与实现的系列芯片

图8. MIT Sze教授团队设计与实现的系列芯片

报告3:来自DARPA的视角

图9. 传统初创企业Seed/A轮/B轮融资额度稳步提升,但芯片初创企业A轮就需要2000万美元

图9. 传统初创企业Seed/A轮/B轮融资额度稳步提升,但芯片初创企业A轮就需要2000万美元

图10. DARPA希望能将芯片设计门槛降下来,促进风投和初创行业,推动创新

图10. DARPA希望能将芯片设计门槛降下来,促进风投和初创行业,推动创新

ERI自从2017年启动以来,其资助的研究内容越来越成体系。下图是DARPA ERI项目所资助的21个项目一览图。DARPA每年也会在7月份举办ERI Summit,将这些项目的核心成员们召集研讨进展与下阶段工作。值得一提的是ERI Summit的报告材料都是可以公开下载,这是2018年的日程与报告下载地址:[http://eri-summit.com/agenda]

图11. DARPA ERI项目所资助的21个项目一览图

图11. DARPA ERI项目所资助的21个项目一览图

图12. DARPA IDEA项目的目标是全自动化(无人干预)、24小时完成全系统硬件设计

图12. DARPA IDEA项目的目标是全自动化(无人干预)、24小时完成全系统硬件设计

图13. OpenRoad在四方面进行优化

图13. OpenRoad在四方面进行优化

图14. OpenRoad将于今明两年开源

图14. OpenRoad将于今明两年开源

图15. 全世界范围内开源EDA工具出现快速增长趋势

图15. 全世界范围内开源EDA工具出现快速增长趋势

图16. 构建开源芯片生态所需要突破的四个要素

图16. 构建开源芯片生态所需要突破的四个要素

图17. CHIPS联盟旨在推动开源芯片生态

图17. CHIPS联盟旨在推动开源芯片生态

图18. 越来越多的开源工具开始出现

图18. 越来越多的开源工具开始出现

Google开源了一个面向RISC-V的验证框架(图19),可以通过RISC-V-DV来产生指令流,对设计进行压力测试。芯片设计过程中的验证环境非常耗时耗力,但又是极其重要的环节。应该说Google的这个开源工具确实芯片设计中的痛点,但如何能灵活应对不同的设计,如何能达到更高的性能,这些都还需要不断优化。

图19. Google开源的针对RISC-V的验证框架

图19. Google开源的针对RISC-V的验证框架

Horowitz教授的这几点经验教训具有很强的启发性,也很具有可操作性,他们团队的工作值得关注。

图20. 硬件加速器的本质就是将应用快速地映射到硬件

图20. 硬件加速器的本质就是将应用快速地映射到硬件

图21. 斯坦福大学开发的芯片敏捷开发AHA工具链

图21. 斯坦福大学开发的芯片敏捷开发AHA工具链

(1)需要花大力气对代码重构才能达到好的性能,简单的C代码在综合得到硬件后甚至可能比CPU性能慢上百倍(图23)。Cong教授团队认为可通过编译优化技术来解决这个问题,因此开发了一个编译器Merlin,简化代码重构工作。体系结构设计的“三大法宝”为并行、流水和缓存。Merlin编译器的目标是将“三大法宝”对应的设计规则集成到编译器中,从而在整个过程中减少人的参与。

图22. 高层次综合HLS面临的两大挑战

图22. 高层次综合HLS面临的两大挑战

图23. C代码需要重构才能获得加速,否则可能会比CPU慢上百倍

图23. C代码需要重构才能获得加速,否则可能会比CPU慢上百倍

图24. DSL能提高HLS开发效率

图24. DSL能提高HLS开发效率

图25. 英伟达产品开发周期需要3-5年,设计与验证占比大约70%

图25. 英伟达产品开发周期需要3-5年,设计与验证占比大约70%

图26. 敏捷开发思路三个要点:高层次语言、工具、库/生成器

图26. 敏捷开发思路三个要点:高层次语言、工具、库/生成器

图27. 机器学习为敏捷开发带来的机遇

图27. 机器学习为敏捷开发带来的机遇

图28. 生成器(generator)是芯片敏捷开发的核心

图28. 生成器(generator)是芯片敏捷开发的核心

图29. 数字电路生成器Chisel3和模拟电路生成器BAG2

图29. 数字电路生成器Chisel3和模拟电路生成器BAG2

图30. 基于BAG2的SerDes生成器

图30. 基于BAG2的SerDes生成器

图31. 基于Chisel与BAG生成的RISC-V芯片

图31. 基于Chisel与BAG生成的RISC-V芯片

图32. 2016年NSF Expedition in Computing项目:DeepSpec

图32. 2016年NSF Expedition in Computing项目:DeepSpec

图33. 端到端形式化验证框架

图33. 端到端形式化验证框架

图34. RISC-V核的形式化验证示例

图34. RISC-V核的形式化验证示例

图35. 经过验证的RISC-V核

图35. 经过验证的RISC-V核

中国当前需要尽快突破被称为是“燃眉之急”的多项关键技术,但从长远来看,中国芯片领域面临的 “卡脖子”问题根源在于优秀人才储备严重不足——我们曾做过一项统计,2008到2017年的十年间体系结构顶会ISCA论文的第一作者(可认为是芯片架构研究优秀人才)85%选择在美国就业,仅有4%在中国就业,差距巨大(图36)。这与当前芯片设计门槛过高,导致中国大学无法开展芯片相关教学与研究密切相关。

开篇

2019年度国际计算机体系结构旗舰会议ISCA于6月在美国亚利桑那州凤凰城召开。6月23日与ISCA一起举行的远景研讨会(SIGARCH Visioning Workshop)吸引了上百位听众。一方面是因为此次研讨会主题“面向下一代计算的敏捷开放硬件(Agile and Open Hardware for Next-Generation Computing)”是当前体系结构研究领域的前沿热点,引起了很多人的关注;另一方面11位报告人中大牛云集,有图灵奖得主David Patterson教授,也有多位美国工程院院士加持,还有来自MIT、Berkeley、Stanford、UCSD、Google、Nvidia、DARPA等顶尖大学、企业和政府机构的专家(自己成了唯一的一位来自美国以外的报告人,多少有些势单力薄)。

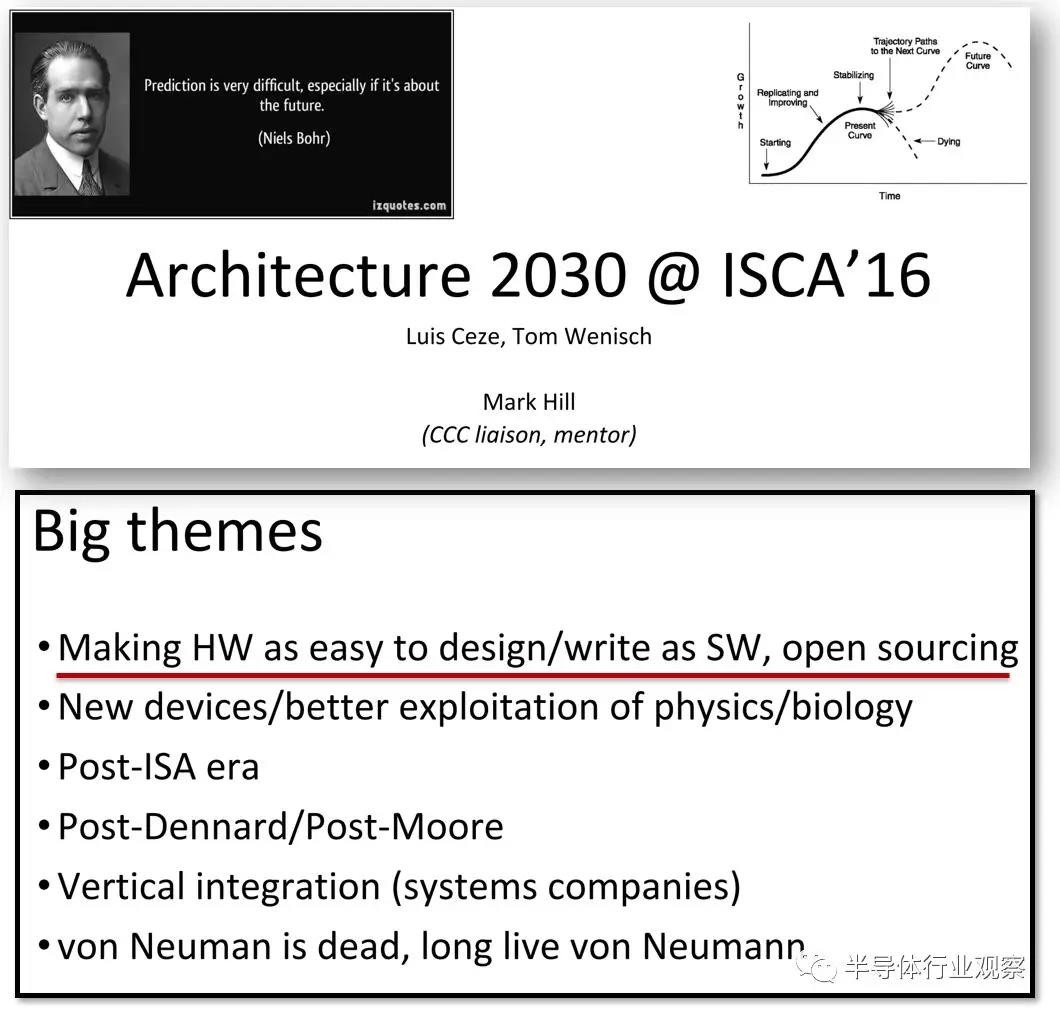

全程听完了一天的报告,我的最大感触是开源硬件(芯片)在美国各界已经成为一种共识——从学术界、企业界到DARPA这样的政府机构,都在积极投入到开源芯片与芯片敏捷开发方向的研究中。早在2016年的首届Architecture 2030远景研讨会上,很多人就认为开源硬件将会是未来的大主题(Big Theme,如图1)。而在国内,很多人对开源硬件/芯片的理解还有些片面,只是认为“开源芯片=RISC-V”。

图1. 2016年远景研讨会上开源硬件便备受关注

图1. 2016年远景研讨会上开源硬件便备受关注 远景研讨会(Visioning Workshop)

ACM体系结构专业委员会SIGARCH组织的远景研讨会(Visioning Workshop)是一个畅想未来的学术研讨会。第一届在2016年的ISCA上举办,当年的主题是《Architecture 2030》,知名华人学者UCSB的谢源教授受邀做了题为《Technology-driven Architecture Innovation: Challenges and Opportunities》的报告。第二届是在多伦多举办的ISCA上,主题为《Trends in Machine Learning》,图灵奖得主 Yoshua Bengio 教授以及陈天奇、贾扬清两位博士均为受邀报告人。

今年是第三届,主题是“Agile and Open Hardware for Next-Generation Computing”,一共有11个报告,以下是议程。

David Patterson, UC Berkeley/Google, A New Golden Age for Computer Architecture

Vivienne Sze, MIT, Domain-Specific Architectures for AI and Robotics: Opportunities and Challenges

Serge Leef, DARPA, Automatic Implementation of Secure Silicon

Andrew Kahng, UCSD, Bringing Design Technology and Architecture Closer Together: What Open Source Might Enable

Yungang Bao, Chinese Academy of Sciences, The Four Steps to An Open-Source Chip Design Ecosystem

Richard Ho, Google, Building A Sustainable Open-Source Hardware Ecosystem

Mark Horowitz, Stanford, AHA! – Agile HArdware

Jason Cong, UCLA, Democratize Customizable Computing

Brucek Khailany, NVIDIA, Machine-Learning-Assisted Agile VLSI Design for Machine Learning

Borivoje Nikolić, UC Berkeley, Generating the Next Wave of Custom Chips

Adam Chlipala, MIT, Strong Formal Verification Across a Hardware-Software Stack with RISC-V

图3. 2019年远景研讨会11位报告人

图3. 2019年远景研讨会11位报告人 报告1:图灵奖得主David Patterson教授眼中的体系结构黄金时代

Patterson教授介绍敏捷与开放体系结构的挑战与机遇。其实他的报告在很多场合都有讲过,其中他对处理器指令集标准与架构设计的分类值得专门再提一下。

首先,他向大家强调ISA指令集、微结构设计、产品是三个层次。如图4,ISA是规范标准,往往用一本书甚至几张纸来记录描述;微结构设计是具体实现,对应的是源代码;产品则是设计的实例化,比如RedHat推出的Linux发行版。他进一步将指令集标准与架构设计都分为三类:开放免费(open & free)、可授权(Licensiable)、封闭(closed)。于是,我们可以看到,Intel就属于封闭指令集+封闭设计,ARM属于可授权指令集+可授权设计,但要获得授权价格不菲,往往需要上百万甚至数千万美元。

RISC-V为全世界提供了开放免费指令集+开放免费设计的选择。根据图5的第一行,我们可以知道只有先有了开源开放的指令集,才有可能有开源开放的微架构设计,即绿色格子。需要强调的是RISC-V本身是一种标准规范,和C/C++语言规范、POSIX系统调用等这些标准是一样的。本身是开放的,谁都可以基于这些标准来实现自己的处理器。但有一点需要厘清的是即使都是基于开源开放指令集(比如RISC-V),也存在三种不同的商业模式:(1)Google、NVidia等企业在内部大量使用RISC-V核作为MCU,但他们不对外开放IP以及源代码,这就属于第一行的红色格子;(2)SiFive公司、中国台湾晶心Andes、阿里平头哥的RISC-V核是可以被授权给第三方使用,但并不开源RTL级源码,因此属于橙色格子;(3)Berkeley的Rocket Chip、剑桥大学的LowRISC、蜂鸟E203等RISC-V核将RTL级源码也开源,这些设计可归到绿色格子。

图4.ISA指令集、微结构设计、产品三个层次以及对应的三种商业模式

图4.ISA指令集、微结构设计、产品三个层次以及对应的三种商业模式 图5. 三种不同商业模式形成处理器分类

图5. 三种不同商业模式形成处理器分类 从图5第一行可知,开放开源指令集并不等于就有了开源的微结构设计,这两者很容易被混为一谈。很多人也误判RISC-V受到DARPA资助会影响其开放性。事实上,TCP/IP协议也是DARPA资助下形成的互连标准,但在具体实现层面也可以有不同商业模式:(1)在网络协议栈的软件实现方面,有集成到BSD/Linux中的开源TCP/IP协议栈,也有微软实现集成到商用Windows的TCP/IP协议栈;(2)在硬件实现方面上,美国思科公司可以研发支持IP协议的路由器,中国华为公司也可以研制自己支持IP协议的路由器,并不会因为是TCP/IP协议是受DARPA支持而不能使用。

另一个典型的例子是龙芯。龙芯是基于MIPS指令集发展起来的,而MIPS最早是由美国企业开发和维护的,但人们都认为龙芯是自主设计开发的,这正是区分了标准规范和微架构设计。但谈到RISC-V时,大家又经常混为一谈,实不应该。

报告2:面向AI和机器人的加速器设计

MIT的Vivienne Sze教授介绍了面向AI、机器人和视频压缩的加速器设计。如图6所示,Sze教授认为领域专用加速器设计的套路是:(1)挖掘应用特征——利用专用硬件来将并行性、数据访问特征等特征转变为吞吐与能效;(2)设计更高效负载——在不影响结果质量的前提下,通过算法与硬件协同设计更高效的负载;(3)定义应用范围——根据应用需求平衡灵活性与效率。

Sze教授用了三个例子分别展示这个套路的有效性,即DNN、机器人自动导航、视频压缩。图7是一个DNN的例子,其他两个例子可以直接看她的PPT材料。

Sze教授近年来获得了各种奖项,今年ISCA上她的学生也获得了最佳博士论文奖。个人觉得他们团队的工作属于稳扎稳打型,他们的设计中采用的技术方案都是意料之中,并没有特别的亮眼的地方。但是他们的工作做得非常扎实,每一项工作都会把芯片做出来(如图8),让人很佩服。相比之下很多其他团队的工作更多只是停留在论文阶段的漂亮设计。

题外话:Sze教授的研究工作风格让我想起中科院动物所所长周琪院士的团队。周所在报告时提到他的学生曾抱怨,“我们发表一篇文章数据量是其他团队的10倍,有这个必要吗?”他的回答是:“你以后会认识到,发表文章不是最难的,最难的是文章发表了要把它撤回来”。世界顶尖团队的研究风格都是类似的。

图6. 硬件加速器设计三部曲

图6. 硬件加速器设计三部曲

图6. 硬件加速器设计三部曲

图6. 硬件加速器设计三部曲 图7. 采用三部曲设计方法的DNN加速器案例

图7. 采用三部曲设计方法的DNN加速器案例 图8. MIT Sze教授团队设计与实现的系列芯片

图8. MIT Sze教授团队设计与实现的系列芯片报告3:来自DARPA的视角

DARPA一直是颠覆式创新的代表,它孕育了很多对人类产生巨大影响的项目,比如Internet、GPS等。在半导体领域,MPW模式/Fabless模式都是在DARPA资助的项目中孕育出来的。因此DARPA的视角也值得关注。

这次报告的是项目主管Serge Leef,他之前一直在工业界,已经有丰富的芯片领域经验。他的报告介绍了如何自动化实现芯片安全。除了传统大家知道的芯片架构安全,他还专门强调了供应链安全,这也反映了美国在对华为禁运的同时,其实也在担心有一天禁运的板子打到自己身上。

这个报告并没有包含具体的技术,但给人印象深刻的是Serge从整个业界生态角度来分析技术的价值——他提到降低芯片设计门槛不仅仅是一个技术问题,也将促进风投和创业,从而推动行业的创新(图9与图10)。对于这一点我深表赞同,自己也曾写过一篇从经济学角度分析开源芯片的文章《驳“发展开源芯片弊大于利”论》。我曾经看过其他DARPA的材料,也都能看到类似这种跳出技术本身、从更宏观的角度分析的思路,很值得学习。

图9. 传统初创企业Seed/A轮/B轮融资额度稳步提升,但芯片初创企业A轮就需要2000万美元

图9. 传统初创企业Seed/A轮/B轮融资额度稳步提升,但芯片初创企业A轮就需要2000万美元 图10. DARPA希望能将芯片设计门槛降下来,促进风投和初创行业,推动创新

图10. DARPA希望能将芯片设计门槛降下来,促进风投和初创行业,推动创新ERI自从2017年启动以来,其资助的研究内容越来越成体系。下图是DARPA ERI项目所资助的21个项目一览图。DARPA每年也会在7月份举办ERI Summit,将这些项目的核心成员们召集研讨进展与下阶段工作。值得一提的是ERI Summit的报告材料都是可以公开下载,这是2018年的日程与报告下载地址:[http://eri-summit.com/agenda]

图11. DARPA ERI项目所资助的21个项目一览图

图11. DARPA ERI项目所资助的21个项目一览图报告4:高效开源EDA工具链已在路上(OpenROAD)

UCSD的Andrew Kahng教授获得了DARPA项目的资助,开展高效开源EDA工具链的研究。他认为EDA以前是关注质量,但现在该开始关注把易用性了。他参与的DARPA IDEA项目目标非常激进——24小时内全自动地完成IP、SoC芯片、PCB版的设计(图12)。

在DARPA的资助下,他带领团队启动了OpenROAD项目,该项目将从四个维度来应对芯片设计复杂度问题:(1)最大化划分,将大的设计尽可能划分为小模块,这样可以两个好处,一方面是降低算法复杂度,另一方面就是更易挖掘并行性;(2)并行优化,这一点与前面最大化划分密切联想,当存在大量并行度时,就可以采用各种加速并行的技术来优化,包括使用GPU来加速;(3)采用机器学习的工具与流程,传统芯片设计流程中有很多经验规则,这一点可以通过训练大量已有设计变成神经网络模型,从而加速最优电路设计的搜索和预测。这方面也是Kahng教授在报告中特别强调的;(4)受限的布局方案也可以减少布局布线时的算法复杂度。

OpenRoad将于今年推出Alpha版,然后在2020年推出v1.0版本。

图12. DARPA IDEA项目的目标是全自动化(无人干预)、24小时完成全系统硬件设计

图12. DARPA IDEA项目的目标是全自动化(无人干预)、24小时完成全系统硬件设计 图13. OpenRoad在四方面进行优化

图13. OpenRoad在四方面进行优化 图14. OpenRoad将于今明两年开源

图14. OpenRoad将于今明两年开源 EDA是国内芯片设计产业最大的软肋,中国的EDA工具企业始终未能做大做强。如今,美国开始将EDA转向开源,中国又应该如何应对?这个问题值得认真研究。我自己的观点是开源总体对中国是有利的,但开源也存在竞争,只有更多的投入、参与和贡献,才能在开源社区中起到主导作用。中国不一定能在所有环节上都存在优势,但还是有可能在某些环节上推出有竞争力的开源EDA工具。

图15. 全世界范围内开源EDA工具出现快速增长趋势

图15. 全世界范围内开源EDA工具出现快速增长趋势报告5:中国的声音

我是这届远景研讨会上唯一一位来自美国以外的报告人,这也反映了美国在这个方向上处于绝对领先地位。我的报告题目是“The Four Steps to An Open-Source Chip Ecosystem”,根据过去几年在开源芯片与敏捷开放领域的一些实践,梳理了构建开源芯片生态所需要突破的四个方面:开源ISA/IP/SoC、开源EDA工具链、高效低成本的仿真验证、系统软件。然后对每一部分的现状和未来努力方向进行了分析。

图16. 构建开源芯片生态所需要突破的四个要素

图16. 构建开源芯片生态所需要突破的四个要素报告6:CHIPS联盟与开源UVM验证框架

来自Google的Richard Ho博士介绍了CHIPS联盟——这是近期Google联合了6家企业成立了一个开源芯片联盟,旨在推动开源芯片生态(图17)。这7家企业每一家都贡献了开源芯片设计中所需要的功能模块,例如西部数据的SweRV核、SiFive的Rocket核、Google的RISC-V-DV验证工具等。从图18可以看到,越来越多的开源工具开始出现,未来基于全开源EDA工具设计开源芯片,将不会是空谈。

图17. CHIPS联盟旨在推动开源芯片生态

图17. CHIPS联盟旨在推动开源芯片生态 图18. 越来越多的开源工具开始出现

图18. 越来越多的开源工具开始出现Google开源了一个面向RISC-V的验证框架(图19),可以通过RISC-V-DV来产生指令流,对设计进行压力测试。芯片设计过程中的验证环境非常耗时耗力,但又是极其重要的环节。应该说Google的这个开源工具确实芯片设计中的痛点,但如何能灵活应对不同的设计,如何能达到更高的性能,这些都还需要不断优化。

图19. Google开源的针对RISC-V的验证框架

图19. Google开源的针对RISC-V的验证框架报告7:硬件加速器设计与领域专用语言DSL

美国工程院院士、斯坦福大学的Mark Horowitz教授介绍了他们在加速器领域的工作。Horowitz教授早期参与了很多多处理器架构、高带宽内存的研究,创办了Rambus公司。在这个报告中,他认为设计一个硬件加速器的本质就是将应用快速地映射到硬件上,这可以分解为三个步骤(图20):(1)用领域专用语言DSL来写应用;(2)用编译器将应用映射到可编程的硬件模型(也可以看作某种粒度的ISA)上;(3)将ISA映射到目标硬件上。

Horowitz教授接着介绍了团队正在开发的AHA工具链,融合了上述三个步骤(图21)。报告非常精彩的部分是他坦言到虽然这套工具链能工作,也开发出了芯片,但还存在很大的问题,整个工具链需要重构。然后他总结了6个经验教训:(1)敏捷开发应该关注系统构建,而不仅仅是加速器的性能,用户关心的应用最终性能;(2)硬件设计不只是功能,还包括很多复杂问题,如时序、布局、测试生成等,这些都不应该暴露给用户,因此可以通过DSL+编译器来为用户屏蔽这些底层细节;(3)用户使用加速器时都会重写应用代码,既然需要重写,从一开始就应该让用户使用DSL;(4)用户希望为一类应用设计加速器,而不是仅仅为一个应用,因此粗粒度可重构架构CGRA是很好的选择;(5)敏捷开发的核心是重用,因此要尽可能设计一些新工具提供重用度;(6)开源硬件可以降低NRE成本,降低维护成本,但开源硬件的形式不一定是硬件,而将会是以软件工具或代码的形式。

Horowitz教授的这几点经验教训具有很强的启发性,也很具有可操作性,他们团队的工作值得关注。

图20. 硬件加速器的本质就是将应用快速地映射到硬件

图20. 硬件加速器的本质就是将应用快速地映射到硬件 图21. 斯坦福大学开发的芯片敏捷开发AHA工具链

图21. 斯坦福大学开发的芯片敏捷开发AHA工具链报告8:高层次综合

美国工程院院士、UCLA的Jason Cong教授是FPGA与高层次综合HLS(High-Level Synthesis)领域的顶尖专家。HLS是从1980年代FPGA兴起时CMU、IBM等就开始研究,但一直未能形成商用。从2006年开始,Cong教授在UCLA启动了xPilot项目,后成立公司AutoESL推出AutoPilot工具,并于2011年被Xilinx收购集成为Vivado HLS工具。在报告中,Cong教授指出HLS还面临两大挑战(图22):

(1)需要花大力气对代码重构才能达到好的性能,简单的C代码在综合得到硬件后甚至可能比CPU性能慢上百倍(图23)。Cong教授团队认为可通过编译优化技术来解决这个问题,因此开发了一个编译器Merlin,简化代码重构工作。体系结构设计的“三大法宝”为并行、流水和缓存。Merlin编译器的目标是将“三大法宝”对应的设计规则集成到编译器中,从而在整个过程中减少人的参与。

(2)如何在很大的设计空间中找到优化设计也是一个很大的挑战。前面提到体系结构层次有“三大法宝”,而在具体设计时每一个法宝都有很多种选择,因此设计空间很大。这个挑战不仅仅是学术界关心,事实上工业界也很关心,我们和海思技术交流中也提到这点。为了应对这个问题,Cong教授团队开发了一套自动化设计空间探索框架(Automated design space exploration framework)。目前还主要是基于梯度进行空间搜索,这方面还有很大的优化空间。

图22. 高层次综合HLS面临的两大挑战

图22. 高层次综合HLS面临的两大挑战 图23. C代码需要重构才能获得加速,否则可能会比CPU慢上百倍

图23. C代码需要重构才能获得加速,否则可能会比CPU慢上百倍 Cong教授认为让程序员来写HLS代码效率太低,应该提供更高抽象的语言,即领域专用的语言DSL——程序员用更高级的DSL来写代码,然后自动生成HLS代码,进而映射到FPGA上(图24)。到这里可以看出这个技术思路与斯坦福Horowitz教授提出的三个步骤一致,如果接着往下看,也会发现第10个来自Berkeley的报告也是同样的理

图24. DSL能提高HLS开发效率

图24. DSL能提高HLS开发效率报告9:英伟达的敏捷开发实践

英伟达ASIC与VISL研究部门主任Brucek Khailany介绍了他们采用机器学习方法的敏捷开发技术。英伟达积极投入芯片敏捷开发,其动力也是因为现在芯片设计太过复杂。例如,英伟达产品的开发周期一般需要3-5年,其中设计与验证的时间与成本占比大约70%(图25),2018年Nvidia Xavier SoC一共花了8000人年!因此英伟达希望能将开发周期与成本降低一个数量级。

英伟达的总体思路包含三个要点(图26):(1)使用更高级的开发语言,英伟达选择的是C++;(2)利用HLS工具将C++代码转变为RTL代码,从而可以嫁接到现有的ASIC开发流程;(3)充分使用已经开发好的库和生成器(libraries/generator),尽可能地重用已有设计从而节省时间。值得一提的是,第(3)点库和生成器是面向领域专用的芯片敏捷开发方法中很重要的环节,未来将会决定芯片敏捷开发的性能与质量。最近这方面的工作也开始增加,比如英伟达开发的MatchLib,Berkeley开发的面向RISC-V的Rocket Chip Generator和面向模拟电路的Analogy Generator(下一章节将会介绍)。

最后Khailany简要总结了将机器学习应用到芯片设计自动化方面的相关工作(图27)。如之前Cong教授报告中提到,设计自动化中面临的挑战之一便是巨大的设计空间。深度学习在大空间高效搜索方面则具有很大的潜力。

图25. 英伟达产品开发周期需要3-5年,设计与验证占比大约70%

图25. 英伟达产品开发周期需要3-5年,设计与验证占比大约70% 图26. 敏捷开发思路三个要点:高层次语言、工具、库/生成器

图26. 敏捷开发思路三个要点:高层次语言、工具、库/生成器 图27. 机器学习为敏捷开发带来的机遇

图27. 机器学习为敏捷开发带来的机遇报告10:支持硬件敏捷开发的新语言与生成器

Berkeley的 Borivoje Nikolić 教授的核心观点是生成器(generator)将是芯片敏捷开发的核心(图28),可以降低芯片设计的成本和开发周期。生成器技术和软件开发中的面向对象思想有很多相通之处,generator可以看作是一个class。简单总结一下这种方式的好处:(1)重用度高,一个生成器可产生很多实例;(2)更易定制化,可通过修改参数产生不同的实例;(3)便于验证,理论上对生成器充分验证(包括形式化验证),可以保障生成实例的正确性。

Nikolić教授带领团队过去几年在这方面做出了杰出的贡献。他们发明了具备更高抽象能力的Chisel语言,使生成器的开发变得更简单。事实上,近年来非常火的RISC-V最早开源实现Rocket Chip实现就是一个基于Chisel的生成器(图31)。

一款SoC芯片设计很大的挑战是模拟电路。Nikolić教授开发了BAG(Berkeley Analog Generator),一套基于Python的开源模拟电路生成器(图29),包括 Comparator 、多种ADC/DAC生成器、SerDes生成器(图30)等。这些生成器在ST 28nm, GF 22nm, TSMC 16nm等不同工艺下成功流片。当然目前实测性能与业界主流产品相比还有差距,比如使用TSMC 16nm工艺的ADC采样频率为7GS/s,精度为6.5bit,而ADI公司于2017年便开发出基于28nm工艺的10GS/s、精度为12bit的产品。但值得一提的是这些都是开源设计,如果社区和企业在此基础上不断优化改进,有可能最终得到足够性能的开源模拟电路设计。

图28. 生成器(generator)是芯片敏捷开发的核心

图28. 生成器(generator)是芯片敏捷开发的核心 图29. 数字电路生成器Chisel3和模拟电路生成器BAG2

图29. 数字电路生成器Chisel3和模拟电路生成器BAG2 图30. 基于BAG2的SerDes生成器

图30. 基于BAG2的SerDes生成器 图31. 基于Chisel与BAG生成的RISC-V芯片

图31. 基于Chisel与BAG生成的RISC-V芯片报告11:端到端的形式化验证

形式化验证(Formal Verification)方法被认为是保证系统正确性的最有效方法。自从2009年第一个经过形式化验证的操作系统内核SeL4发表以来,形式化验证方法已收到越来越多地关注,尤其是在操作系统领域。2016年,美国NSF在计算机领域额度最大的“Expedition in Computing”项目(5年1000万美元)资助了由普林斯顿大学、麻省理工学院、康奈尔大学、宾夕法尼亚大学联合申请的形式化验证软硬件全系统栈的项目:DeepSpec(图32),一个目标极其远大而具有颠覆性、同时也极具挑战的研究项目。

MIT的Adam Chlipala教授也是DeepSpec的co-PI,他在Visioning Workshop上介绍了基于RISC-V开展的全系统端到端强形式化验证研究进展(图33),包括硬件RTL层次的验证、编译器的验证等。Chlipala教授展示了一个经过验证的RISC-V核实现(图34,图35),目前还只能用于演示点灯。

报告中我的理解是相比于传统的Verilog,具有更高抽象的硬件描述语言(如BlueSpec、Chisel)将有助于RTL层次的形式化验证。不过由于自己对这个领域也了解不多,所以也无法更深入地解读他们的研究工作。

在这里可以分享一段有趣的经历:我在普林斯顿大学做博士后时在同一个办公室的是Andrew Appel教授的博士后Lennart Beringer,当时正在开展编译器的形式化验证研究。当时曾问过他形式化验证的前景,他自己认为可能需要20年才能实用。让人感慨的是,几年后,即使在一线研究人员看来都很遥远的研究却得到了NSF的大力资助,而Lennart现在也正是DeepSpec项目的副主任。相比较于美国大力资助形式化验证的系统实现,国内从事这方面研究的团队就显得太少了,也很难得到资助。这种现状亟需改变。

图32. 2016年NSF Expedition in Computing项目:DeepSpec

图32. 2016年NSF Expedition in Computing项目:DeepSpec 图33. 端到端形式化验证框架

图33. 端到端形式化验证框架 图34. RISC-V核的形式化验证示例

图34. RISC-V核的形式化验证示例 图35. 经过验证的RISC-V核

图35. 经过验证的RISC-V核中国的挑战与机遇

芯片一直是中国半导体产业的软肋,如何破解中国半导体产业面临的“卡脖子”问题,各界都在积极实践与探索。

中国当前需要尽快突破被称为是“燃眉之急”的多项关键技术,但从长远来看,中国芯片领域面临的 “卡脖子”问题根源在于优秀人才储备严重不足——我们曾做过一项统计,2008到2017年的十年间体系结构顶会ISCA论文的第一作者(可认为是芯片架构研究优秀人才)85%选择在美国就业,仅有4%在中国就业,差距巨大(图36)。这与当前芯片设计门槛过高,导致中国大学无法开展芯片相关教学与研究密切相关。

这种人才危机美国也曾经历过,1982年全美上千所大学中只有不到100 位教授和学生从事半导体相关的研究。为了应对人才危机,美国DARPA在1981年启动MOSIS项目,为大学提供流片服务,通过MPW模式大幅降低芯片设计门槛(图37)。三十余年来MOSIS为大学和研究机构流了60000多款芯片,培养了数万名学生。因此,降低芯片设计门槛亦可大幅提高人才培养效率。

开源芯片与敏捷开发,有可能再未来实现数量级地降低芯片开发门槛。开源芯片生态仍处于起步阶段,如果中国能积极参与并主导开源芯片生态中若干核心模块,那么就有可能吸引更多开发人员、民间资本参与芯片开发,提高芯片领域的创新活力,同时也能为中国芯片企业提供基于开源的芯片关键技术与优秀人才、摆脱“卡脖子”困境。

结语:2030憧憬

总结来说,开源芯片与敏捷开发备受关注,背后存在两方面的驱动力:

(1)应对摩尔定律终结的技术发展需求:Dennard Scaling定律和摩尔定律逐渐走向终结,但摩尔定律赋予芯片的能力并未充分挖掘出来。例如实现一个矩阵乘法,普通程序员写的程序和懂体系架构的专家写的程序性能上甚至会有63000倍的差距。因此,面向某个特定领域将专家知识实现到芯片中,就有可能提升几百甚至几千倍的性能功耗比,从而充分挖掘芯片上晶体管的潜力。但这种领域专用体系结构(DSA)会带来碎片化问题,需要从芯片设计成本与周期两个维度同时降低门槛,才能应对种类繁多的领域专用加速器。

(2)激发创新活力、繁荣芯片产业的市场需求:长期以来芯片研发成本高、周期长,导致了该领域的高门槛,严重阻碍了创新。即使研制一款中档芯片,也往往需要数百人年、数千万甚至上亿的研发投入,导致资本不愿投资。因此,只有少数企业才能承担,资本市场对芯片投资也是极其谨慎保守,制约了芯片领域的创新活力。

构建开源芯片生态与敏捷开发方法一个长期的系统工程,面临着诸多挑战,但也是一个不管是学术上还是商业上都值得探索的方向,也需要各界的支持与参与。

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 复杂SoC芯片设计中有哪些挑战?

- 2 进迭时空完成A+轮数亿元融资 加速RISC-V AI CPU产品迭代

- 3 探索智慧实践,洞见AI未来!星宸科技2024开发者大会暨产品发布会成功举办

- 4 重磅发布:日观芯设IC设计全流程管理软件RigorFlow 2.0