[原创] 台积电加速进入3nm,晶圆代工双王争霸时代开启

日前,据ANANDTECH报道,台积电上周表示,“在3nm上,技术开发进展顺利,我们已经与早期客户就技术定义进行了接触,”台积电首席执行官兼联合主席CC Wei在与投资者和金融分析师的电话会议上表示。“我们希望我们的3纳米技术能够进一步扩展我们在未来的领导地位”,看来,台积电的制造技术已经脱离了寻路模式,而且开始与早期客户合作。

在台积电加速前进的同时,另一边厢三星也在快马加鞭,晶圆代工的双雄争霸时代正式开启。

台积电的衔枚疾走

由于其3nm技术尚处于早期开发阶段,因此台积电目前尚未谈及该流程的具体特征及其优于5nm的优势。但事实上,台积电已经确认3nm是一种全新的工艺技术,而不是5nm的改进或迭代。台积电表示,公司已经评估了3nm所有可能的晶体管结构选择,并为其客户提供了“非常好的解决方案”。该规范正在开发中,该公司相信它将满足其领先的合作客户的要求。

2019年4月18日,在台积电召开第一季度财报会议中,台积电指出3nm技术已经进入全面开发的阶段。分析师王兆利认为,强大的3nm芯片的主要应用将是云计算,人工智能和5G。苹果,华为,谷歌和Nvidia可能成为台积电新芯片的潜在客户。

同时,可以肯定地说,台积电的3纳米节点将同时使用DUV和EUV光刻设备。由于台积电的5nm使用了14个EUV层,因此3nm的使用层数可能会更高。这家全球最大的半导体合约制造商似乎对其EUV进展感到非常满意,并认为该技术对其未来至关重要。

虽然3nm技术的细节并没有太多披露,但在工厂上面,台积电进展神速。

2018年12月,根据 台湾新闻 报道,台积电已经获准在台南南部科学园开始建设新的芯片工厂。台积电计划投资6000亿新台币(约合195亿美元)用于新工厂的建设,计划于2020年开始。该芯片制造商预计将于2021年进入生产试运行,并于2022年开始量产,准备让他们进入最新的 手机 和 平板电脑 。新工厂计划在台南南台科技园建设,并将与台积电的5nm芯片工厂并列,该工厂将于2020年初完工。

2019年7月,台湾相关部门发表公告指出,他们已经审议通过台积电3 纳米宝山厂都市计划变更案件,对于台积电预计投资超过六千亿元兴建3 纳米宝山厂。这加速了台积电的工厂建设。

三星的亦步亦趋

在晶圆代工领域,领先的代工厂大抵是这几家,三星、台积电、英特、GlobalFoundries、联电等,然而早在2018年8月13日台湾第三大晶圆代工厂联电宣布停止12nm以下先进工艺的研发,8月28日全球第二大晶圆代工厂Global Foundries官宣搁置7nm的FinFET项目。至此,7nm以下的角逐场中仅剩下了英特尔、三星和台积电。

因为英特尔主要是一个IDM,那就意味着现在能与台积电一搏的只剩下三星。

三星是世界上最大的科技公司之一,但它的野心远不能止步于此。三星不能忍受台积电在晶圆代工领域独自称霸,希望在台积电吞噬的代工蛋糕中分得更大的一块。目前,台积电占据了约50%的合同制造市场,而三星则以略低于15%的份额落后。

台积电在2018年初达到了一个重要的里程碑,当时它成为世界上第一家出货7nm的供应商。后来,三星进入了7nm的比赛。工艺到了3nm,三星似乎比台积电更快一步。2017年,三星推出了3nm的所谓多桥通道FET(MBCFET)。

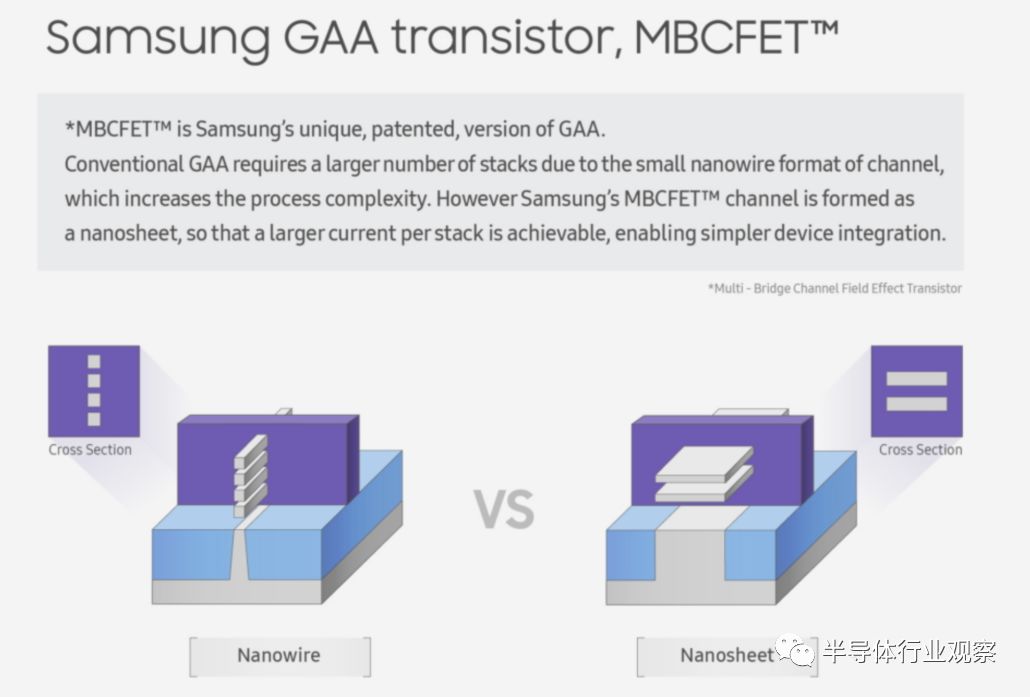

韩国联合通讯社报道指出,2019年5月,在圣克拉拉的三星铸造论坛上,三星邀请了800名半导体研发人员和客户参观其新工艺技术的进展,并宣布了其下一代半导体制造工艺的计划。最大的宣布是三星的3nm GAA的发展,栅极全能场效应晶体管GAAFET(Gate-All-Around)是三星与IBM合作开发的工艺节点,也一度被三星认为是FinFET的继任者。现在三星宣布了对早期工艺的定制,已将其注册为MBCFET(多桥通道FET)。不过三星的3nm制程将使用GAA技术,并推出MBCFET,目的都是为了确保3nm的实现。

根据三星的说法,它可以通过用纳米片取代Gate All Around,从而使每一层的电流更大。这种替换增加了传导面积,并允许在不增加横向足迹的情况下添加更多的栅极。与传统的FinFET设计相反,GAAFET允许栅极材料从所有侧面环绕通道。三星声称,MBCFET的设计将改善工艺的开关行为,并允许处理器将工作电压降低到0.75V以下。MBCFET关键点是,该工艺完全兼容FinFET设计,不需要任何新的制造工具。与7nm FinFET相比,3nm MBCFET将功耗和表面积分别降低30%和45%,这一过程还将比目前高端设备的性能节点提高40%。

为了抢占台积电的市场,这家韩国巨头为其先进的3nm GAAFET工艺发布了工艺设计套件,以便潜在客户尽早开始艰难的设计工作。

三星还强调了其6nm,5nm和4nm工艺节点的计划。据该公司介绍,三星将在2019年下半年开始6nm批量生产,同时,该公司将完成其4nm制造工艺的开发。三星还透露,该公司的5纳米工艺的产品设计将在2019年下半年完成,该节点将在2020年进入批量生产,而且 与台积电的5纳米工艺大致相同 。

三星一直以来都拥有强大的研究基础,而现在所有这一切都在通过他们的新技术推动市场的发展,这项新技术将在2021年开始进入市场。咨询公司International Business的首席执行官认为:“ 三星强大的材料研究计划正在取得成功,三星在GAA中领先于台积电大约12个月,英特尔可能比三星落后两到三年 。”

但是三星的野心不止于此,目前尚未有公司宣布3nm之后的半导体工艺,目前大家都认为摩尔定律在3nm之后就要彻底失效,遭遇量子物理的考验,而三星则希望借助GAA工艺开发2nm工艺,未来甚至要实现1nm工艺。

3nm的困难重重

玩芯片,不但要有技术,还要有钱。由于每个新节点的优势已经缩小,采用成本增加,半导体行业在过去几年中越来越难以提供新的工艺节点。台积电,GlobalFoundries,三星和英特尔等成为最后四家领先的代工厂的最大原因之一就是将极紫外光刻(EUV)引入即将到来的工艺节点,因为不使用EUV 的成本已经变得不可持续。

虽然预计EUV会通过减少每个设计所需的掩模数量来降低制造处理器的成本,但它并无法降低芯片设计的成本,而且芯片设计成本上升得如此之快。

国际商业战略(IBS)的下图显示了5纳米的预期设计成本,3纳米数据点尚未出现在图表中。将“16nm”色谱柱视为迄今为止我们在市场上看到的各种12/14 / 16nm芯片,它意味着构建新的GPU,CPU或SoC的成本约为1亿美元。即使在7nm,设计成本也增加了两倍。但是从7纳米移动到3纳米将意味着将成本提高5倍。

据手机晶片大人分享,台积电5nm全光罩流片费用大概要3亿元,这还不含ip授权。半导体芯片的设计费用包含IP、Architecture、检查、物理验证、软件、试产品制作等。据IBS称,设计3nm器件的成本从5亿美元到15亿美元不等,而工艺开发成本从40亿美元到50亿美元不等,工厂的开发成本在150亿到200亿美元之间,所以我们也看到台积电斥资190亿美元建3nm工厂也是合理之中。“基于相同的成熟度,3nm晶体管的成本预计将比5nm高出20%至25%,”IBS'Jones说。

因此,随着芯片设计成本的增加,3nm工艺节点处于危险之中。随着迁移到新节点的成本上升,改进旧节点作为提供给客户改进的手段的相对价值也会上升。我们也看到了市场的一些变化,很多厂商有时强调对旧节点的改进或使用较旧的节点与新的制造技术相结合。例如,当三星转而构建3D NAND时,它就采用了40nm工艺。通过使用较旧的工艺节点,三星能够改善其TLC NAND的特性。虽然美光和英特尔没有具体说明他们用于 四电平单元 (QLC)NAND的工艺节点,但几乎可以肯定它也建立在较旧的工艺节点上。GlobalFoundries拥有 22nm节点和FDSOI - 明显的尝试是迎合希望转向28nm以下改进工艺节点的客户,但与14 / 16nm FinFET相比,需要低功耗和低设计成本。(FinFET的设计成本较高,FD-SOI的晶圆成本较高)。

国内厂商任重道远

众所周知,由于我国在芯片领域的起步较晚,相对落后于西方发达国家,芯片制造企业亦是如此。作为大陆绝对龙头的中芯国际,承载着国家对于上游晶圆制造的决心。最近几年,中芯国际在先进制程的研发上奋力推进,取得了不错的成就,2019年2月中芯国际14nm工艺量产更是引起了巨大关注。

2017年10月,曾任职台积电研发部门领头人的梁孟松博士加入中芯国际,加快了企业向先进制程的转型,14nm就是其转型的成果。2019年2月中芯国际采用内部开发的14纳米FinFET制造技术开始批量生产。值得注意的是,这至少比最初的预期提前了几个季度,表明中芯国际显然提前了。而且据悉中芯国际14nm的产量已达到95%,足以开始大规模生产。

在过去的14nm工艺中,中芯国际已经开始研究其10nm和7nm工艺,正如公司在2018年所证实的那样。这两种工艺设计成本极高,但由于半导体工业总体上正在发展,中芯国际这几年也在加紧布局。2018年中芯国际以1.2亿美元的价格从ASML购买了EUV极紫外光刻机,用于7纳米工艺开发并最终大规模生产。事实上,在国际高端手机行列,无论是华为麒麟系列、高通的骁龙系列处理器,亦或是苹果的A12处理器,都是采用的7nm的制程工艺。

据ANANDTECH报道,“中芯国际正在筹集100亿美元用于14nm,10nm和7nm的扩产。国际商业战略(IBS)首席执行官亨德尔·琼斯(Handel Jones)表示,到2021年,它们将在第四季度每月生产70,000片晶圆。

中芯国际的联席首席执行官梁博士针对第一季度的财报也说讲到:“我们的FinFET技术研发进展顺利,12nm正在进入客户互动,我们下一代FinFET的研发进展顺利,基于我们积累的技术发展,中芯国际的FinFET Fab的建设已经成功完成,我们已经开始进行容量部署。我们将为客户技术迁移的快速转变做好准备,以应对不断变化的行业环境。”

如今,中芯国际14nm,12nm工艺开发也已经进入到客户导入阶段,下一代FinFET研发在过去积累的基础上进度喜人。与三星、台积电相比,中芯国际作为后来者确实在制程上相对落后,但其研发支出毫不逊色,自2013年触底反弹后,研发占收入的比例持续提升,2018年时,该比例为16.52%,是台积电的一倍。

随着摩尔定律放缓,制程的不断压缩,即在越接近1nm的制程上,花费的时间越多,在3nm 的领地中,中芯国际作为大陆最大的代工厂,任重道远,未来可期。

3nm以下工艺一直被公认为是摩尔定律最终失效的节点,如今3nm 已经离我们很近了,3nm之后的2nm,1nm还会远吗?你认为未来半导体技术的演进路径是怎样的?