台积电强攻先进封装,芯片未来靠它了

TSMC(台积电)在不久前的芯片领域顶级会议VLSI Symposium上一连发布了两篇与高级封装有关的论文,论文标题是《3D Multi-chip Integration with System on Integrated Chips (SoICTM)》和《A 7nm 4GHz Arm-core-based CoWoS Chiplet Design for High Performance Computing》,分别对应了其高端3D和2.5D封装技术。 近来,高级封装领域正在变得越来越热,本文将分析其中的趋势。

台积电的高级封装技术

台积电本次在VLSI Symposium发表的3D集成技术是其SoIC技术。 去年下半年,台积电就已经发布了SoIC技术,并宣布计划于2021年投入大规模量产。 在今年早些时候的TSMC技术论坛上,SoIC也是重点之一,而此次在VLSI Symposium上发表的论文则从技术上再次强调了TSMC对于该技术的重视。

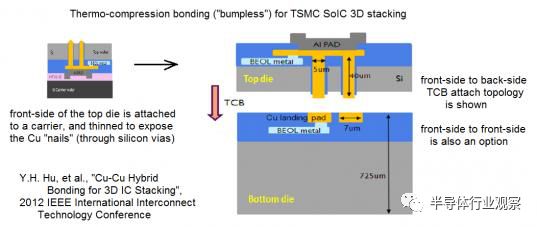

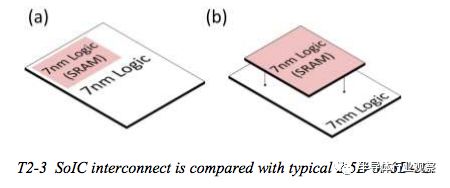

3DIC技术到今天已经发展了大约10年的时间。 相比最初人们对于3DIC的期待,今天的3DIC技术的发展事实上差强人意,并没有得到一开始预期规模的应用。 其中一个要点就是传统3DIC技术的连线密度受到bump尺寸的限制,从而限制了集成总线的带宽和互联成本。 而TSMC展示的SoIC技术一个关键创新就是无须bump,只要将两块要堆叠的芯片的铜互联做部分裸露并对准,之后即可通过热处理工艺完成两块芯片的电路连接。 这样一来,两块堆叠芯片之间的走线密度以及信号传输功耗都可以大大改善。

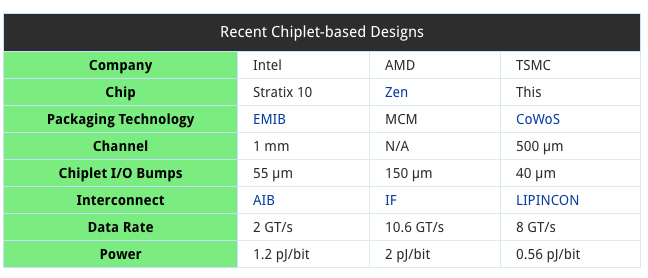

在3DIC之外,TSMC在2.5D封装领域也发表了使用CoWoS技术搭配低电压封装内互联(LINPINCON)技术的处理器系统,该处理器系统包含了两块ARM Cortex-A72核芯片粒,并且用CoWoS技术实现芯片粒之间的互联。 芯片粒中的ARM核可以跑在4GHz,而芯片粒间互联可以实现8GT/s的高速数据传输速度,且能效比极高(0.56pJ/bit)。

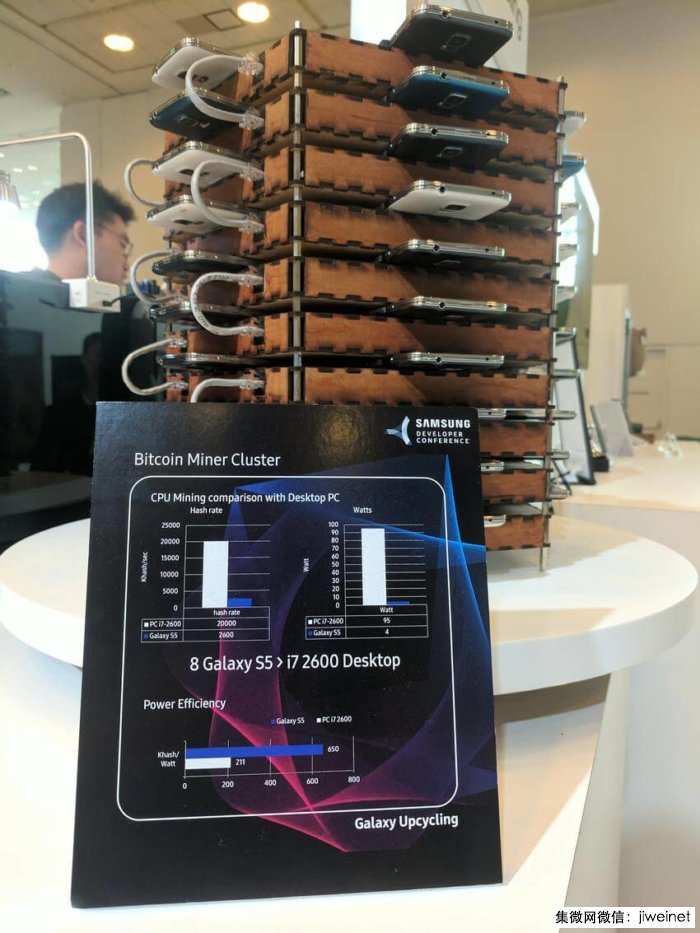

事实上,CoWoS技术是TSMC已经研发了数年的技术,在之前已经多次公布,并且已经进入了多款设计; 此次发表论文除了与同样使用2.5D封装实现高性能处理器的Intel打对台之外,我们认为另一个重点是宣传其LIPINCON PHY的设计。 简单回顾一下3DIC、2.5DIC和互联PHY之间的历史,我们可以看到最初3DIC的第一波潮流由三星引导,在2012年时三星发布了基于其3DIC技术的内存并公布了相应的Wide-IO接口标准(与DDR相对应),在当时可谓是震撼了业界。 TSMC也希望能打三星的组合拳: 发布高级封装,并且建立对应的信号互联标准从而建立强大的生态。 三星的3DIC和Wide-IO标准最后的结果可以说是喜忧参半,其3DIC技术得到了业界的一些应用,然而Wide-IO标准最终并未得到业界广泛采用。 这并不是说三星的高级封装+互联标准战略有错,而是由于十年前的技术和市场都没有完全起来导致的。 TSMC在3DIC方面并非抢跑者,但是却通过对市场的精确把握在两年后推出2.5D封装一炮而红,当年2.5D封装技术InFO成功进入苹果的芯片供应链,成为高级封装技术走向大规模商用的标志性事件。 TSMC在2.5D封装技术成功后,还是想通过“封装+互联标准”的战略来打造生态,因此在过去的几年中也发表了多篇关于其基于高级封装的互联PHY的论文,这次在VLSI Symposium上发表的论文可以说是系列论文中的最新更新。 相比Intel和AMD的互联标准(AIB和Infinity Fabric),TSMC的LINPINCON互联的能效比要好上数倍,因此更适合低功耗设计。

高级封装已成高性能芯片不二之选

高级封装技术在最近几年热度上升,已经成为高性能芯片的必选项。 历数最近发布的芯片,Intel的下一代AgileX FPGA架构使用了EMIB技术,其下一代处理器芯片可望用上最新的3D堆叠Foveros技术; AMD的Zen处理器架构也是基于高级封装+芯片粒的设计。

高性能处理器芯片使用高级封装技术的主要原因有两点。 第一是处理器发展至今,对于性能的限制一大半来自于内存带宽,内存带宽的发展速度远远低于处理器逻辑电路的速度,因此有“内存墙”的问题。 在传统PCB封装中,内存带宽增长缓慢主要是由于PCB上的走线密度难以提升,此外信号传输速率也很难进一步提升。 而高级封装则解决了这两个问题,一方面高级封装可以大大提升互联密度,另一方面由于高级封装的走线距离很近,因此信号传输速率有很大的提升空间。 两者结合,高级封装技术是解决内存墙问题的主要手段之一,因此在高性能处理器上得到了广泛应用。 高级封装对于高性能芯片重要的另一个原因是良率提升。 高性能处理器的架构越来越复杂,晶体管数越来越多,然而先进半导体工艺的价格却很贵,良率提升速度也差强人意。 为了能降低使用先进半导体技术的成本并提升良率,一种做法就是把大芯片切割成多个小的芯片粒,并且用先进封装技术连接到一起。 在半导体制造中,一般芯片面积越小则良率越高,因此使用芯片粒可以大大提升良率并降低成本。

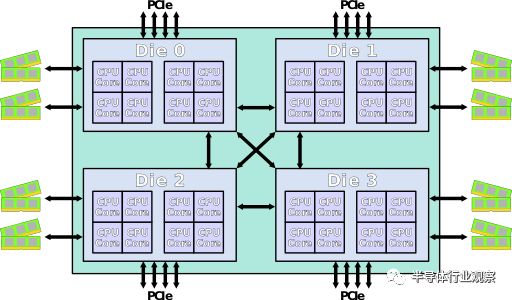

与TSMC相比,AMD是高级封装的态度是积极使用; 因为AMD并没有隶属于自己的封装工艺,因此其在高级封装领域的技术主要是处理器架构方面。 在AMD发布的Zen架构中,高级封装和芯片粒扮演了相当重要的角色: AMD将多个核+L3缓存组成的芯片粒单元称为Zeppelin,使用不同Zeppelin的组合并且使用AMD研发的互联标准Infinity Fabric可以快速实现多种不同规格(处理器核数量)的处理器。

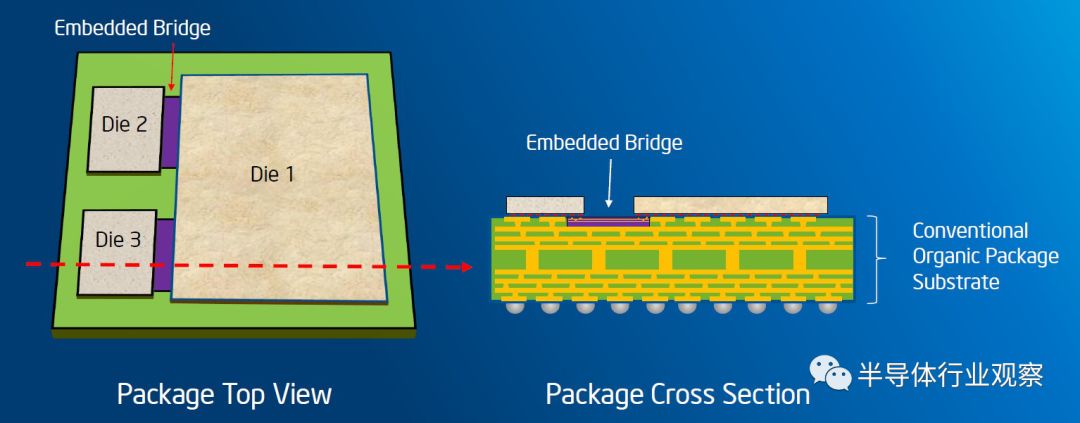

Intel是TSMC在高级封装领域最强的竞争对手。 从技术上说,Intel的2.5DIC技术和3DIC都并不逊色于TSMC。 在2.5DIC方面,Intel主推的是EMIB。 EMIB最大的优势是成本低: 传统2.5DIC在专门设计的硅载片上做互联,而EMIB技术则可以使用传统的封装介质上,只需要在两块芯片粒间需要互联的区域植入embedded bridge即可,从而无须使用整块专用硅载片。

在3DIC领域,Intel则推出了Foveros技术。 该技术除了有很高的bump密度(32um)之外,最大的创新在于使用了有源硅载片,即把使用先进半导体工艺实现的高性能逻辑芯片堆叠在使用成熟半导体工艺实现的有源硅载片上,该有源硅载片本身也是一块芯片,上面实现了IO接口电路,未来可望还能集成其他适合使用成熟工艺实现的电路(如电源管理等)。

台积电与Intel在高级封装领域的战斗

在高级封装领域,目前主要的竞争在台积电和Intel之间展开。 除了我们之前分析的技术差异之外,Intel和TSMC最大的区别在于商业生态。

TSMC是全球首屈一指的半导体代工厂,其主要业务模式就是帮助客户一起成功。 因此,在高级封装领域,TSMC不遗余力地推广开放生态,包括封装技术、互联接口标准以及相关的IP,希望能给客户带来更多价值。 在未来几年,随着下一代半导体工艺越来越贵,出于成本等考虑,一定会有越来越多的公司选择芯片粒生态,因此TSMC这几年的布局显然是在用户认知、技术和IP积累领域希望营造一个开放生态,从而延续之前在半导体业的成功。

Intel则是IDM厂商,其传统是工艺主要开放给自己的设计以及少数合作伙伴,换句话说其商务模型并不开放。 高级封装技术也是如此,主要供自己使用。 近来,随着Intel在半导体工艺方面落后于三星和TSMC,其处理器性能也渐渐被AMD追上,因此必须靠高级封装逆转战局。 此外,Intel的传统业务——CPU市场增长不再强劲。 这几项因素相结合,Intel靠领先的独家工艺打造强势CPU,并靠主导CPU市场来获取增长的战略不再有效,因此Intel的一个选项是靠自己在高级封装技术上的技术积累来获取新的增长点。 为了将高级封装技术变现,最好的方法就是培养相关的生态并开放给客户使用来获取利润,这也是Intel目前大力推广芯片粒生态的原因,并开放了其互联标准AIB,前一阵发布的AgileX FPGA架构更是直接鼓励用户继承定制的芯片粒以做用户定制化的系统。 然而,芯片粒技术需要设计和加工厂的支持,Intel如果想要真正培养其芯片粒生态必须也要进一步开放代工业务。 目前看来Intel的开放主要方式仍然是合作式的,即有选择地和一些设计公司合作一起开发基于芯片粒的设计,这样的开放程度似乎还不足以真正培养生态。 另外,一个需要处理的点是Intel的传统CPU业务和开放高级封装技术之间的矛盾——半导体设计公司都希望代工厂是中立的,但是Intel因为自己有CPU业务所以不太可能中立(例如不会把工艺开放给AMD),如果这个矛盾处理不好Intel能打造的也只是围绕自己CPU/FPGA业务为中心,并且招揽一些商业上的盟友加入的生态(类似之前的AgileX系统),这样的生态注定难以做大。 在这一点上,TSMC存在天然的优势,即使EMIB技术目前在成本上领先,Foveros技术或许也不输TSMC的SoIC技术,但是Intel的商业模型和制度天然与生态需要的开放性和中立性相矛盾。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 共筑国产汽车芯片未来,中国汽车芯片联盟全体大会即将开启

- 2 国产EDA突破,关键一步

- 3 汽车大芯片,走向Chiplet:芯原扮演重要角色

- 4 英特尔至强6强势驱动,火山引擎g4il服务器性能飙升