LithoVision 2019——半导体技术趋势及其对光刻的影响

今年,我再次被邀请出席Nikon的“LithoVision”活动。LithoVision是SPIE先进光刻会议前一天举行的,地点同样在圣何塞。接下来是我演讲的总结。

演讲的要点是:

-

NAND – 用层实现微缩

-

DRAM – 外围微缩和新选择

-

Logic – 高性能和物联网

-

结论

NAND—用层实现微缩

3D NAND的位出货量现在已经超过了2D NAND。并且正在迅速成为NAND Flash存储器的主导形式。3D NAND已经将NAND微缩形式从光刻驱动转换到由堆叠层驱动的沉积和蚀刻。

图1展示了三星和东芝这两家最大的3D NAND生产商使用的TCAT工艺。

图1:3D NAND TCAT工艺

在3D制作中,有三个主要部分:

-

CMOS制造——制造电荷泵,读写和存储器寻址电路。

-

存储器阵列的形成——可以是一串或多串。例如,在64层单串制造顺序中,所有64层都会沉积,然后形成图案。在64层双串制造顺序中,先沉积32层并形成图案,然后沉积另外32层并形成图案。

-

Interconnect——CMOS和存储器阵列是互连的。

存储器阵列串形成顺序是:

-

沉积氧化物和氮化物的交替层(Deposit alternating layers of oxide and nitride)。 这是栅极的最后一道工序,三星和东芝都在使用。英特尔沉积氧化物和多晶硅的交替层。

-

应用沟道孔掩模,并向下蚀刻通过堆叠(The channel hole mask is applied and etched down through the stack)。 沟道孔填充氧化物—氮化物—氧化物(ONO)薄膜,然后再填充氧化物的多晶硅沟道。这种蚀刻非常具有挑战性,特别是对于氧化物/聚合物而言,这就是为什么英特尔比三星或东芝更早地进行串堆叠(string stacking)。

-

应用厚的光刻胶,并使用阶梯式掩模形成图案(A thick photoresist is applied and patterned with the stair-step mask.)。 蚀刻和收缩顺序用于创建一组阶梯。在必须剥离掩模并应用新掩模之前,可以创建大约8个阶梯。64层器件通常需要8个掩模来制造整个阶梯。

-

应用slot 掩模,并向下蚀刻通过堆叠。(A slot mask is applied and etched down through the stack)。 使用湿法蚀刻蚀刻出氮化物层,然后用氧化铝和氮化钛存储单元膜代替,然后用钨填充水平层。将钨蚀刻回slot 中,沉积氧化物,并用钨填充沟槽。可能还有第二个浅slot 。

-

现在应用通孔掩模并蚀刻到阶梯(The via mask is now applied and etched down to the stair steps)。

-

在沟道和slot掩模之前可能需要清除掩模,因为硬掩模和层堆叠难以对准。清除是指在层上蚀刻的大面积正方形,以此来暴露对准目标。

上图左下角的图表显示了按公司排列的串。英特尔—美光开始在64层进行串堆叠,东芝预计将在128层进行串堆叠,三星预计将生产128层的单串。

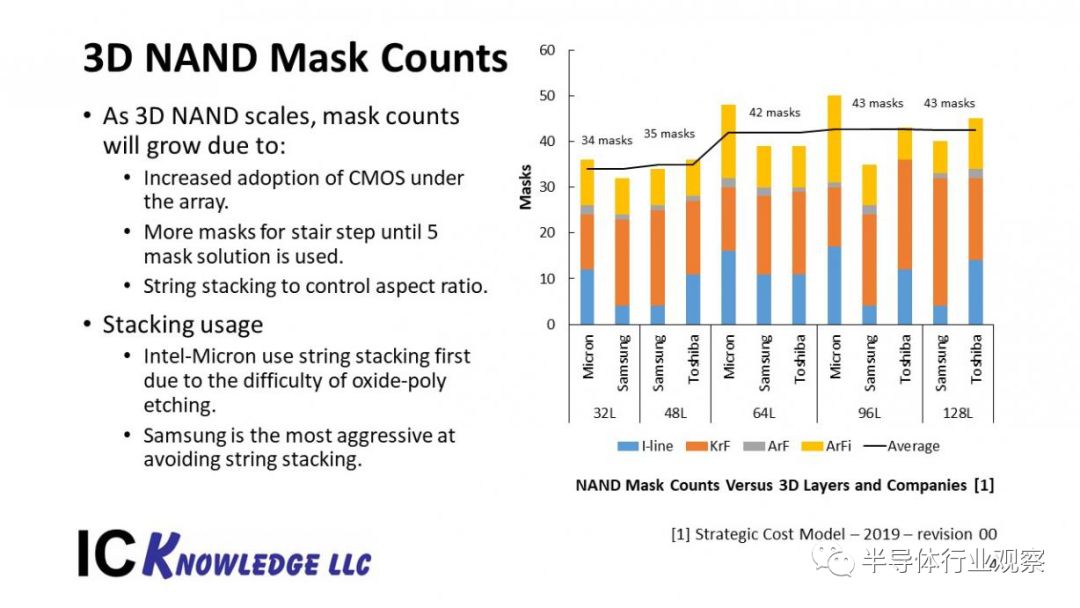

图2展示了各公司的3D掩膜数量:

图2:3D NAND掩膜数量

此处有一对相互竞争的趋势。在存储器阵列下进行串堆叠和移动某些CMOS会增加掩模数量,而使用较少掩模的精简阶梯的方案会减少掩模数量。

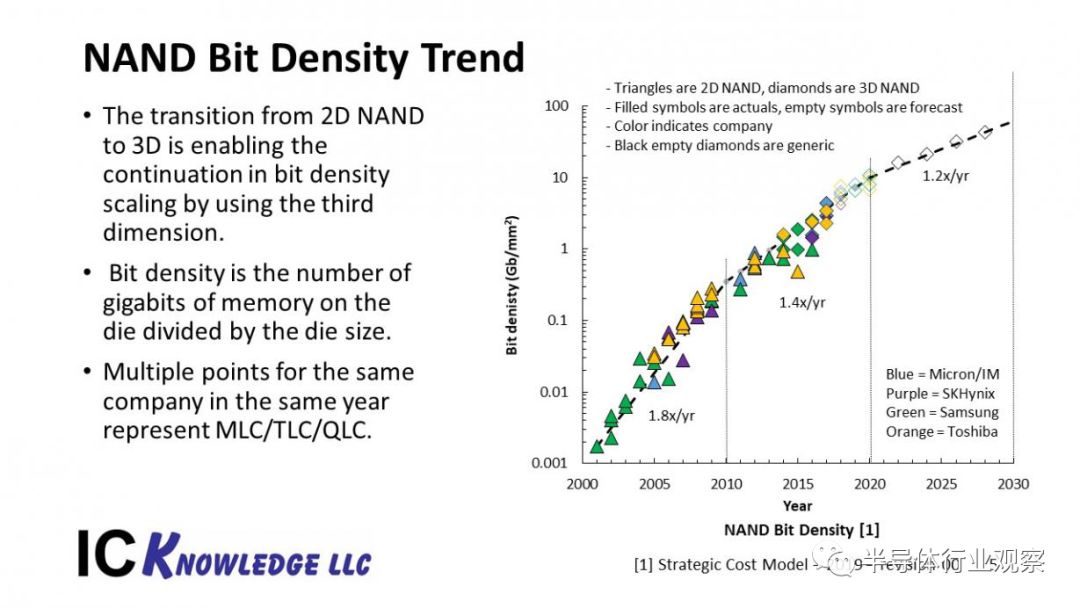

图3展示了各年份的NAND位密度。

图3:NAND位密度趋势

从2000年到2010年,2D NAND由光刻驱动的微缩带来了1.8倍/年的位密度增长。2010年后,由于器件微缩问题,2D NAND光刻驱动微缩速度减慢,位密度增长放缓至1.4倍/年。21世纪10年代中期,3D NAND被引入,并在这个十年的接下来的时间中延续了1.4倍/年的微缩趋势。在20世纪20年代,由于制造如此高的存储器堆栈的挑战,我们预测微缩将进一步放缓到1.2倍/年。

DRAM—外围微缩和新选择

DRAM微缩一直面临着试图缩小电容的基本挑战,外围微缩已成为关键因素。

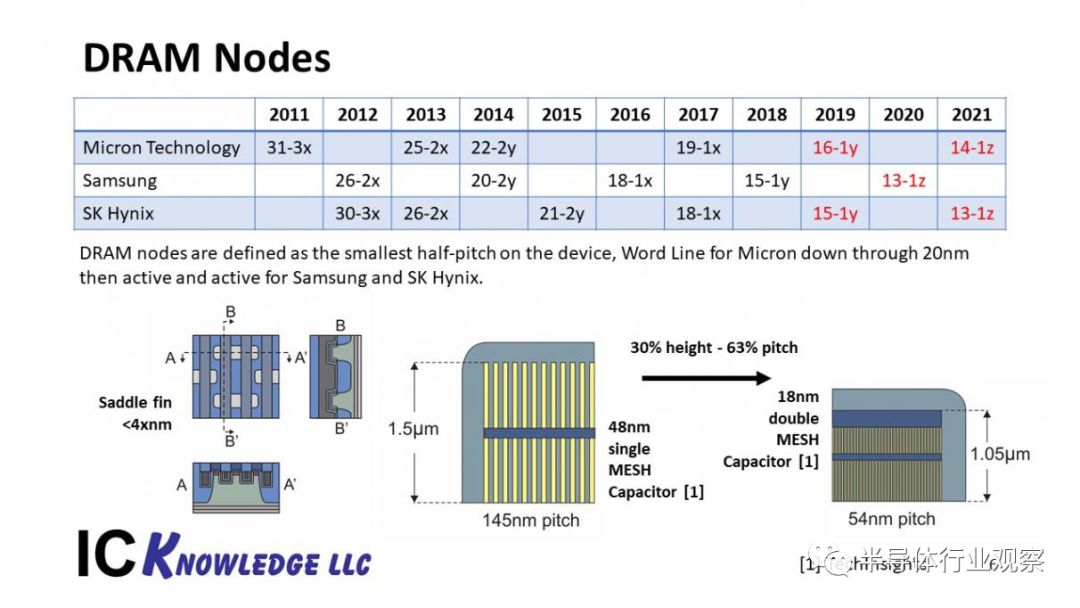

图4展示了各公司的DRAM节点微缩情况。

图4:DRAM节点

图4中可以看到各公司的DRAM节点。在幻灯片底部列出了一些关键的技术成果。左下角是马鞍形存取晶体管(Saddle Fin access transistor),目前在DRAM中普遍使用。右下角列出了从48nm节点到18nm节点的电容微缩。

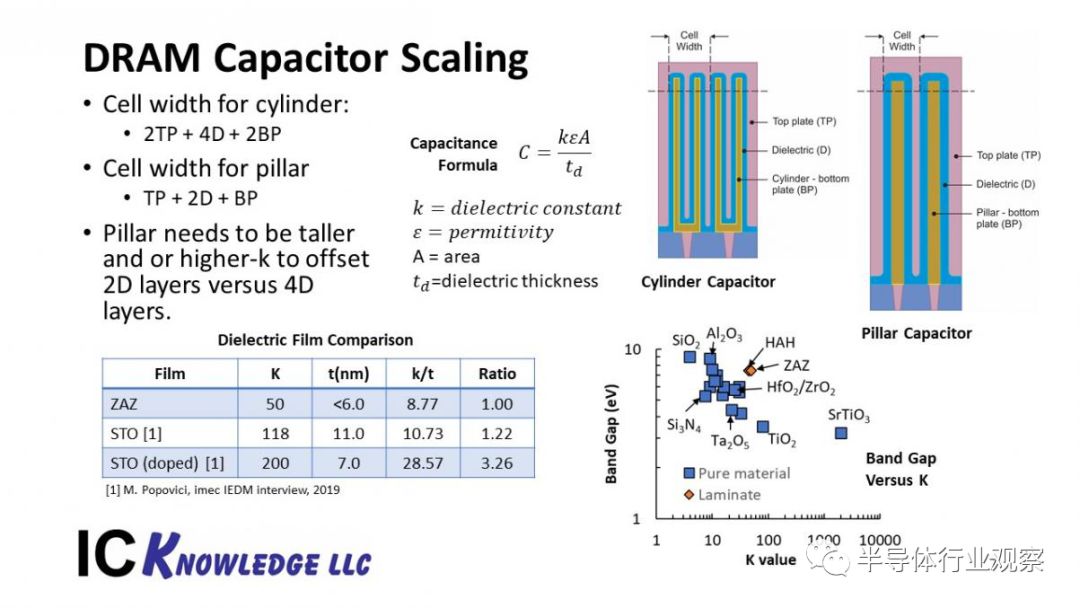

图5展示了DRAM电容的微缩。

图5:DRAM电容微缩

DRAM将数值存储为电容器上的电荷或缺少电荷。为了保持这个值并可靠地感知它,我们需要一个最小电容值。电容器的电容由薄膜的k值乘以一个常数和电容器的面积除以薄膜厚度得到。理想情况下,我们希望电容器更小,以缩小DRAM,但这会降低电容。我们使用垂直尺寸来增加电容器的3D面积,同时缩小水平面积,但我们面临着高度上的机械限制。电介质的薄膜厚度已经在没有太多泄漏的情况下尽可能地薄了。从右下角的图中可以看出,随着k值的增大,带隙通常会减小,而带隙的减小会增加泄漏。

Imec在IEDM 2019会议上报告的一个有趣的最新结果是,一种基于钛酸锶的薄膜具有较高的k值,如果足够厚,可以达到可接受的泄漏。当然,使薄膜变厚会降低电容,因此薄膜的品质因数变为k / t,其中t是可接受泄漏的厚度。左下方的表格列出了目前的氧化锆—氧化铝—氧化锆(ZAZ)薄膜、目前的Imec STO薄膜,以及Imec认为可以实现的掺杂STO薄膜。目前ZAZ薄膜的品质因数是8.77,Imec为10.73,提高了1.22倍,如果Imec能够实现它们的预期薄膜,品质因数将是28.57,提高3.26倍。

要想获得更厚的薄膜,就需要改变电容的结构。目前的圆柱结构在每个单元中具有2个底部存储板厚度,4个介质膜厚度和2个顶部存储板厚度。为了适应介质膜的厚度,单元需要改变,以满足所需的单元尺寸。柱状结构具有1个顶部存储板厚度、2个介质膜厚度和1个底部存储板厚度。这使得缩小单元更容易,但它只有2个而非4个介质膜厚度,因此你得到的电容只有一半,除非你使支柱更高。柱子在机械上更坚固,应该可以更高,但可能不能高出两倍。然而,如果一种薄膜可以达到像Imec预计的STO(掺杂)那样的效果,那么它的品质因数是3.26,即使在相同的高度下也会增加电容。

图6展示了其他一些DRAM微缩问题。

图6:其他DRAM微缩问题

图6总结了其他一些DRAM扩展问题,特别是:

-

最小电容值已从一度被认为是最小电容值的20-25fF缩小到10fF左右。这是通过优化驱动电路和感应放大器实现的。

-

如右上角的表格所示,核心和外围电路占DRAM裸片的大约50%,缩小这些电路有助于缩小DRAM裸片。最终,这些晶体管将转变为高k金属栅极(HKMG)和FinFET,但这需要以较低的成本来完成。

-

正如前面所讨论的,圆柱形电容器可以改为柱状电容器,以便为介质薄膜提供更多的空间。

-

如果薄膜晶体管能够以足够低的漏电率开发,那么DRAM电容在晶体管上的堆叠逻辑就可以成为一次性微缩的助推器。

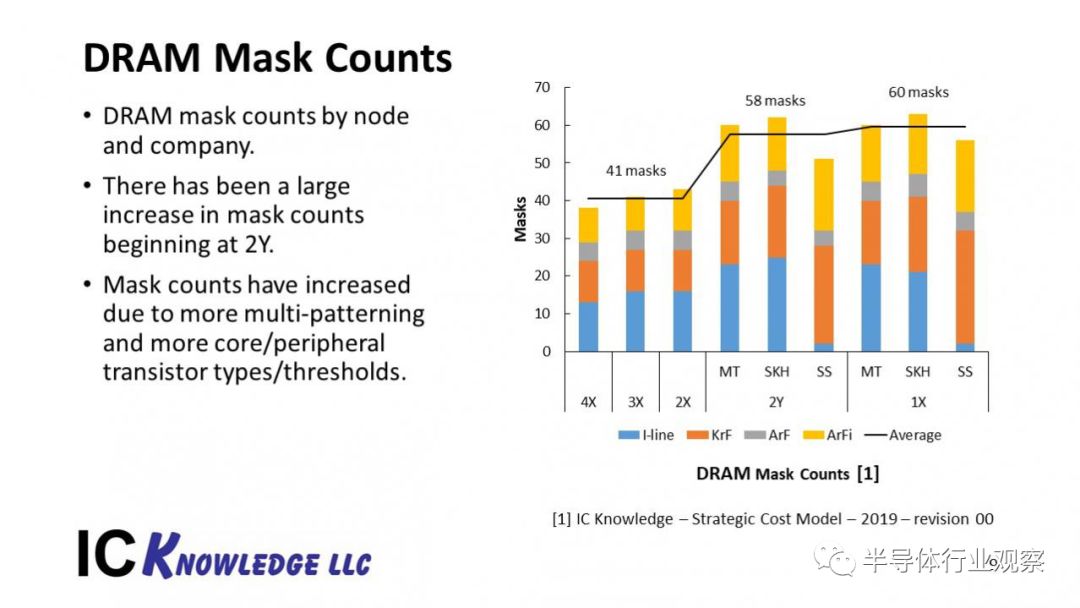

图7展示了DRAM的掩模数量。

图7:DRAM掩模数量

优化外围晶体管和核心晶体管的需求使得多种晶体管类型和阈值电压的晶体管数量大幅增加。这是从去年的演示中更新的,在去年的演示中,我们低估了两年及以后的DRAM的掩模数量。

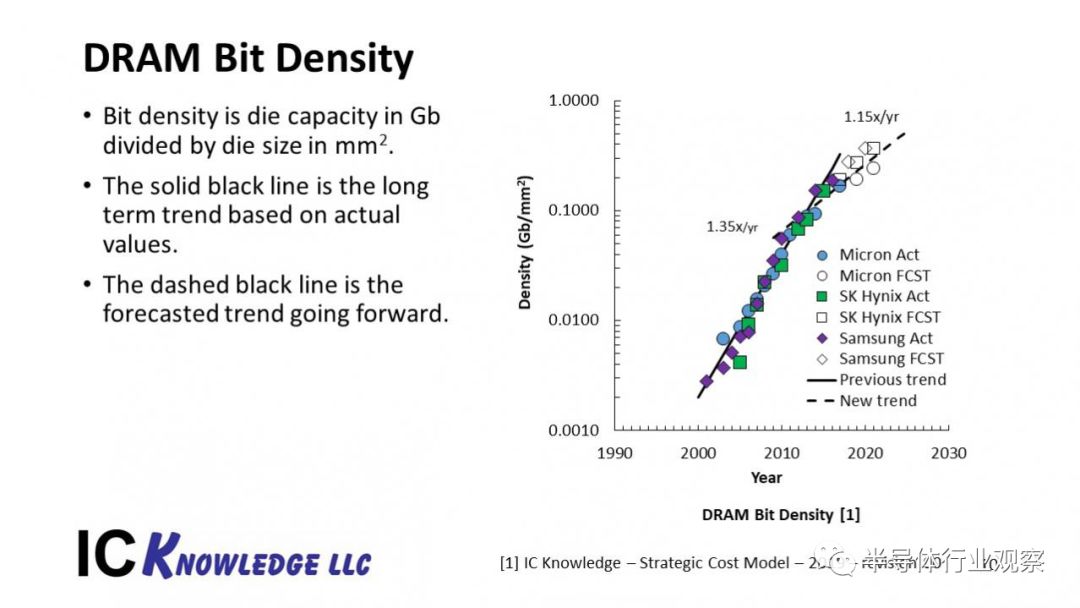

图8展示了DRAM的位密度趋势。

图8:DRAM位密度

从图8中我们可以看到,2010年之前,DRAM的位密度以每年1.35倍的速度增长,此后,位密度的增长已经放缓到1.15倍/年左右。

逻辑—高性能和物联网

前沿逻辑已经从平面晶体管发展到分裂的路线图,FinFET用于高性能,FDSOI用于物联网。更长远的“环绕栅极”(gate-all-around)即将到来。

图9展示了逻辑的环绕栅极(GAA)。

图9:逻辑的环绕栅极(GAA)

从图9可以看出,对于平面晶体管,有效栅宽(Weff)是由晶体管栅宽决定的。对于FINFET,Weff取决于鳍的宽度和高度的2倍,因此Weff只能以离散的增量变化。对于GAA,Weff为厚度的2倍,宽度的2倍。改变宽度的能力可以再次启用可变Weff,并实现晶体管优化。例如,从右下角我们可以看到,水平纳米线(HNW)的静电性能最好,但单位面积的Weff小于FinFET。随着水平的纳米片的变化,宽度可以提供比具有更好静电的FinFET更高的单位面积的Weff数值,尽管不如HNW好。

图10展示了从2D到3D的前沿逻辑路线图

图10:从2D到3D的前沿逻辑路线图

图10展示了从28nm和20nm节点的2D平面晶体管到FinFET,然后是HNS,以及最终堆叠3D CFETS的路线图。直到N7的典型代工逻辑尺寸全都如表所示。

对于N5和N3.5,我们对三星和台积电有具体的预测。在N2.5,我们有一个通用的预测,两家公司都集中在HNS上。

对于3D,我们可以从宽松的14nm设计规则CFET(7层)开始,以及更激进的3.2、3.3和3.4 CFET(3nm光刻,2、3、4层)。图中显示了单层器件的nFET和pFET,然后是用于2层CFET的pFET和nFET。

图11展示了不同公司的掩膜数量,并通过2层CFET进行了预测。

图11:前沿逻辑掩模数量趋势

此图的一个有趣特性是EUV如何有助于减少掩模数量的增加。1.75nm节点的CFET也有助于通过高度自对准来控制光刻难度。

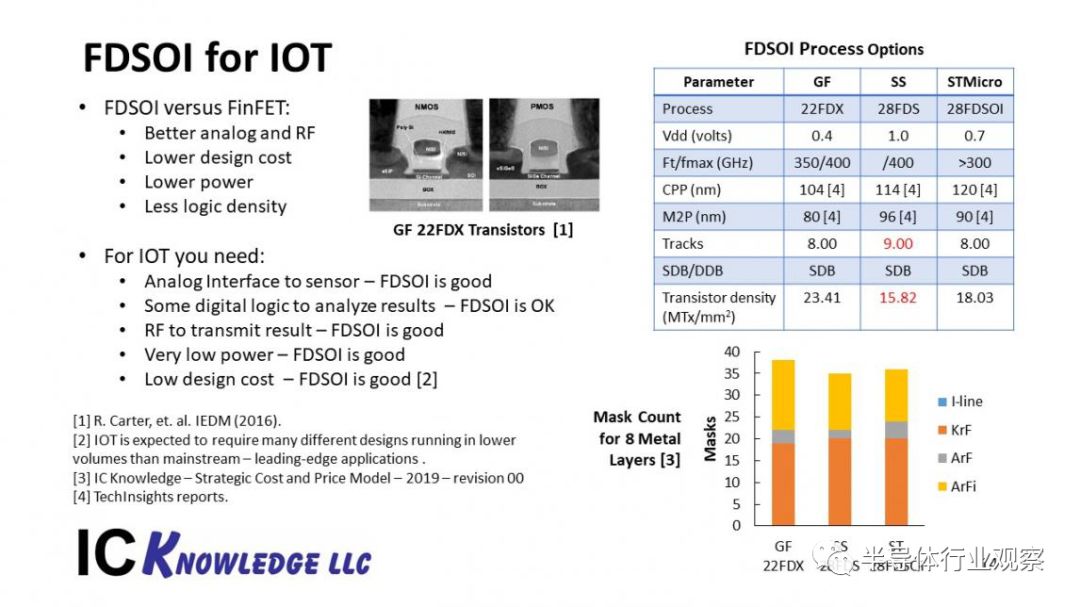

图12展示了物联网应用的FDSOI工艺。

图12:物联网应用的FDSOI

物联网需要有模拟传感器接口,处理结果、存储结果,并进行无线传输,这与FDSOI工艺非常匹配。与FinFET相比,更简单的FDSOI工艺的设计和生产成本也更低。

右边的表格总结了三家领先供应商的FDSOI工艺,GLOBALFOUNDRIES最密集、功率最低,射频性能更高。右下角的图表列出了工艺的掩模数量。将30年代中期的掩模数量与60年代的FINFET工艺和掩模数量进行比较会是一件很有趣的事情。

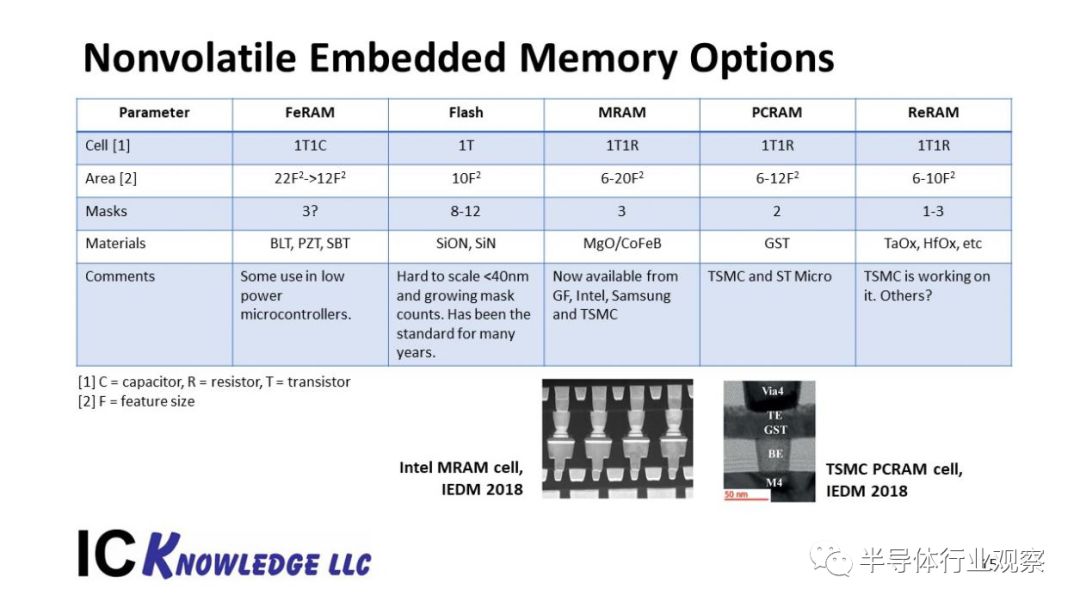

图13展示了各公司正在探索或提供的非易失性嵌入式存储器选择。

图13:非易失性嵌入式存储器选择

图13展示了嵌入式非易失性存储器的五种主要替代方案。从历史上看,Flash已被广泛使用,FeRAM已经在低功耗微控制器中得到了一些应用。目前,MRAM得到了最多的关注,英特尔和所有领先的代工厂都支持它。PCRAM和ReRAM正在引起人们的注意,但还没有那么成熟。

结论

NAND已经从2D光刻驱动工艺迁移到3D蚀刻和沉积驱动工艺。pitch从2D值放宽,未来不太可能变得更严格。由于串堆叠,掩模数量将会增加。

DRAM微缩是电容器的限制,并面临基本的物理限制。微缩的重点是核心和外围的改进,潜在的新的高k电介质即将到来。微缩速度正在放缓。

逻辑继续以光刻方式进行微缩,但2D收缩的基本限制正在迫近。CFET提供了一种可能的3D微缩路线,可以产生与3D NAND类似的不严格的光刻尺寸。物联网和其他应用正在引起人们对更简单的FDSOI工艺和新兴嵌入式存储器的兴趣。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根