[原创] 代工厂备战22nm

在过去一两年中引进了新的22nm工艺后,代工厂正在加速生产技术,并为最后的决战做准备。

GlobalFoundries、英特尔、台积电和联华电子都在开发和扩大各自的22nm工艺,有迹象表明,22nm节点可能为汽车、物联网和无线等应用带来大量业务。但代工客户面临一些艰难的选择,因为并非所有22nm工艺都是相同的。此外,并非所有22nm工艺都有完整的EDA工具或IP。

尽管如此,代工厂商仍在推动22nm工艺,原因有很多。首先,28nm经过多年的增长后,代工业务在28nm面临着放缓和产能过剩。所以代工厂商们认为22nm工艺可以带来新的收入。

此外,22nm填补了代工客户的空白。许多28nm及以上的客户正在考虑迁移到16nm/14nm及更先进的节点。但在这些节点上,只能选择finFET晶体管,而finFET比传统的平面晶体管更昂贵。

图1:FinFET vs 平面 (来源:Lam Research)

因此,对于28nm及以上的代工客户而言,22nm是极具吸引力的选择。它提供了比28nm更好的性能,但它比16nm/14nm及更先进节点的FinFET更便宜。

但是,从一家代工厂选择的22nm技术可能与另一家代工厂的22nm技术大不相同。不同的代工厂推出了三种不同版本的22nm:

-

台积电和联华电子正在开发一种22nm bulk CMOS工艺。

-

GlobalFoundries正准备采用一种22nm平面FD-SOI技术。

-

英特尔正在推出一种低功耗22nm finFET技术。

这还不够,三星正在开发一种18nm平面FD-SOI技术。不管是22nm还是18nm,代工厂的目标客户都是一样的,这意味着代工厂之间的竞争将会升温。

“22nm会成为下一个流行节点吗?我认为是的。”代工资深人士,Arm公司后端物理设计部门营销副总裁Kelvin Low表示,“我不相信哪个阵营会赢,或者另一个阵营会赢。有几个阵营将会胜出,因为设计上的考虑非常不同。”

当然,22nm和18nm并不适合所有人或所有应用。与以前一样,芯片制造商可以选择停留在28nm及以上,或跳过22nm和18nm,直接迁移到16nm/14nm及更先进的节点。决策基于应用以及传统指标,如功率、性能、面积微缩、交付计划和成本。

为了帮助行业走在潮流的前沿,Semiconductor Engineering考察了22nm工艺和供应商基础。

Bulk CMOS

今天,一些人认为22nm是一个独立的市场,而另一些人认为22nm是28nm的一个子集。

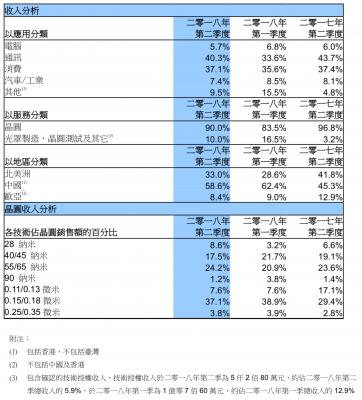

国际商业战略(IBS)是一家研究公司,它将28nm、22nm、20nm和18nm这四个节点归为同一类。IBS的数据显示,2018年,这个市场(包括所有工艺类型)的总规模将达到115亿美元,比2017年下降2.8%,预计到2019年,22nm市场仅增长0.6%。此节点的实际增长预计将在此之后发生。

在这一点上,28nm是这一类别中最大的一块。IBS的数据显示,2017年,仅28nm代工工艺市场的规模就高达100亿美元。然而,到了2018年,28nm是持平的,并且受到产能过剩的困扰。一些(但不是全部)28nm客户正在迁移到先进节点。而中国正在建设更多的28nm晶圆厂产能,从而加剧了市场的困境。

最重要的是,22nm开始蚕食28nm。IBS首席执行官Handel Jones表示:“2018年,22nm代工市场是28nm的10%。我们认为,随着时间的推移,22nm将成为一个大节点。”

在22nm的三种主要风格(平面bulk CMOS、FD-SOI和finFET)中,bulk CMOS是最著名的,因为它多年来一直是芯片行业的支柱。CMOS用于平面晶体管和FinFET晶体管,而FD-SOI使用专用的绝缘体上硅晶圆,在衬底中加入了薄绝缘层。

每种技术都有其自身的优点和缺点。Bulk CMOS是最便宜的,但2D CMOS晶体管容易发生静态泄漏,这是引入FinFET的关键原因之一。控制泄漏可以使芯片制造商提高时钟频率,但速度必须与动态功率密度保持平衡。与此同时,FD-SOI使用平面结构实现了相同的功能,同时增加了衬底偏置选项来控制功率。缺点是FinFET和FD-SOI都比CMOS昂贵。

所有这些22nm的选择都是为了赢得新业务,再无需多重曝光,因为多重曝光既费时又昂贵。这就是为什么2011年推出的28nm节点已经成为许多先进IC设计的最佳选择。它平衡了应用的性能和成本。

IBS数据显示,28nm平面器件的平均设计成本为5130万美元,而16/14nm芯片的平均设计成本为1.063亿美元。因此,虽然GlobalFoundries、台积电、联华电子以及其他公司提供16/14nm finFET,但是大多数设计仍然在较老的节点上进行。

图2:IC设计成本逐渐上升 (来源:IBS)

IBS的琼斯说:“当你迁移到finFET时,你的掩膜和设计成本会大幅增加。finFET对数字器件有好处,但你不能真的做RF。混合信号是一个挑战。”

finFET是高性能应用的理想选择,但finFET技术在其他方面受到限制。它很难集成RF和大规模模拟电路。因此,为填补这一空白,不久前几家代工厂商开始开发22nm。22nm为那些希望性能超过28nm,但不需要或负担不起16nm/14nm以及更先进节点的客户提供了一个选择。

22nm是物联网、混合信号和RF的理想选择。根据IBS的数据,它的价格低于16nm/14nm,因为22nm器件的平均IC设计成本为7030万美元。

联华电子公司营销总监John Chen表示:“我们预计22nm的生命周期会很长,而且产量合理。客户不是直接从28nm迁移到14nm finFET,而是有一个极具吸引力的超低泄漏工艺选项,可以从现有的28nm设计中迁移出来。22nm从更低的掩模和设计成本中获益比14nm更多。”

对于采用65nm、55nm和40nm设计的芯片制造商而言,22nm还提供了相对轻松的升级途径,这是许多对成本敏感的设计正在进行的地方。Arm公司的Low说:“当这组产品迁移到下一个节点时,22nm会出现一波大浪潮。当成本合适时,就会发生这种情况。这同样与IP可用性有关。一旦二者俱备,市场就会起飞。”

在众多22nm的选择中,由台积电和联华电子开发的平面bulk CMOS基本上是当今28nm平面bulk CMOS技术的缩小版。与28nm一样,它采用高k /金属栅极,铜互连和低k电介质。

这种方法有一些优点和缺点。优点是,它是28nm的延伸,芯片制造商可以使用相同的设备和工艺流程。缺点是,bulk技术在接近20nm时会受到讨厌的短沟道效应的影响。这反过来会降低器件中的亚阈值斜率或关断特性。

然后,在传统晶体管中,栅极下方的沟道区耗尽了移动电荷,使掺杂原子电离。IBM公司半导体专家和前技术人员Terry Hook解释说:“来自这些原子的电荷和栅极功函数(gate work function)一起设置了阈值电压。耗尽区的深度控制静电。耗尽区下面是带有大量移动载流子的中性硅。”

但随着技术的推进,bulk CMOS晶体管容易出现一种被称为随机掺杂波动的现象。简单地说,这会导致沟道中的掺杂原子发生变化。因此,bulk CMOS晶体管可能表现出与其标称特性不同的性能,并且还可能在阈值电压方面产生随机差异。

GlobalFoundries产品线管理高级主管Jamie Schaeffer在最近的一段视频中表示:“平面bulk 技术受到大量随机掺杂波动的限制,这种波动控制着先进节点上晶体管的失配和变化。”

解决这个问题的一种方法是转向完全耗尽的晶体管类型,如FD-SOI和finFET。芯片专家Hook说:“在FinFET和FD-SOI中,通道掺杂物被减到最小,你可以在匹配上得到一次性的好处。”

不过,两家代工厂商台积电和联华电子计划用22nm技术突破bulk CMOS的极限。尽管存在挑战,但22nm bulk正在取得一些进展。

Gartner的分析师Samuel Wang表示:“据我了解,一些客户正在利用密度/速度/功率的优势,从28nm迁移到22nm。台积电预计,约20%的28nm/22nm客户将选择22nm。FD-SOI适用于低功耗小众应用。22nm bulk是流行的28nm的缩小版本。大多数设计人员习惯于这种设计方法,它有更广泛的后端物理IP。”

与此同时,台积电最近公布了其先前宣布的22nm技术的更多细节,该技术涉及两个工艺平台。第一种技术是22nm超低功耗(ULP),适用于需要更高性能的低功耗应用。第二种是22nm超低泄漏(ULL),适用于超低功耗器件。

台积电研发副总裁Cliff Hou表示:“对于物联网和RF/模拟应用,应用领域非常广泛。一项技术很难同时涵盖这两种应用。这就是我们需要分别优化它们的原因。”

22nm ULP的工作电压为0.8~0.9伏。台积电透露了22nm ULL的新规格——0.6伏。该版本将于2019年4月发布。

除了技术规格,代工客户还必须检查EDA工具和工艺的IP支持。这变得很棘手,因为一些代工厂在22nm工艺提供了比其他代工厂更多的EDA/IP支持。

代工厂依赖第三方EDA工具。然后,对于给定的流程,代工厂开发了一些自己的IP,但它们也依赖于第三方IP。EDA供应商和IP技术有很多。但在一个主要的IP开发中,22nm标志着台积电进入了嵌入式MRAM和电阻RAM空间。

嵌入式存储器集成在微控制器(MCU)中。MCU将NOR flash用于嵌入式存储器应用,如代码存储。

然而,NOR flash难以微缩到28nm以下,这促使了对下一代内存技术如MRAM和RRAM的需求。新的存储器类型结合了SRAM的速度和flash的非易失性,具有无限的耐用性。

尽管如此,Microchip仍计划将其名为SuperFlash的嵌入式flash技术延伸到22nm。Microchip的子公司Silicon Storage Technology(SST)营销总监Vipin Tiwari表示:“一旦28nm技术合格,我们计划支持FD-SOI和22nm技术。因为22nm是28nm的微缩节点,所以这些节点很可能需要SuperFlash技术。 eMRAM和SuperFlash技术可以共存,具体取决于最终应用。”

然后,在另一个第三方IP前端,Arm为台积电的22nm工艺开发了物理IP,例如标准单元库、通用I / O和存储器编译器。

在EDA方面,大型EDA供应商支持台积电的22nm技术。西门子Mentor事业部产品营销总监Michael White表示:“22nm的实现方式因代工厂的不同而有所不同,它们在光刻的方式和提供的DFM支持程度方面存在一些细微的差异。需要注意的是,因为这是一个新的节点变体,所以最终签收(golden Signoff)和后续工具之间总是存在时间延迟/质量差异。无晶圆厂的客户希望利用这个行业的优势,或者在流片时出现的问题上承担更高的风险。”

联华电子还在开发一种22nm bulk CMOS工艺。联华电子的Chen 说:“联华电子目前正在最后确定我们22nm工艺的客户规格,我们预计将在2020年投入生产。该技术节点具有性能和功率优化,与28nm相比约10%的面积微缩,超低功耗和RF/毫米波优势。联华电子的22nm平台将成为一种经济高效的解决方案,可为平面高k /金属栅极技术提供广泛的应用,包括移动通信(5G和其他无线)、物联网和汽车行业。”

FD-SOI

GlobalFoundries是第一个参加22nm工艺竞赛的厂商。三年前,该公司推出了22nm FD-SOI技术。一段时间以来,三星已经开始提供28nm FD-SOI,18nm版本也在进行中。

此外,GlobalFoundries正在开发12nm平面FD-SOI,预计将于2022年上市。通常,22nm或18nm FD-SOI不与16nm/14nm finFET竞争,它们服务于不同的市场,几乎没有重叠。

FD-SOI使用专用SOI晶圆,它在衬底上集成了薄绝缘层(20-25nm厚)。该层将晶体管与衬底隔离,从而阻断器件中的泄漏。

FD-SOI也是基于平面的、完全耗尽的架构。GlobalFoundries的Schaeffer说:“这基本上消除了随机掺杂的波动,提供了优异的失配和静电特性来改善亚阈值斜率。”

图3:Bulk vs FD-SOI。FD-SOI不仅通过栅极控制晶体管的状态,还通过极化器件下面的衬底控制晶体管的状态。 (来源:意法半导体)

GlobalFoundries的22nm FD-SOI技术称为22FDX,将高k/金属栅极与沟道中的硅锗结合在一起。与28nm相比,它的性能提高了30%,功耗降低了45%。它于2017年初获得了生产资格。

最近,GlobalFoundries增加了更多的功能。Schaeffer说:“Sub-6GHz RF、毫米波、超低泄漏和超低功率扩展都通过了认证。”

使FD-SOI具有吸引力的两个特点是低功耗和衬底偏置。它可以在0.8伏下实现910μA/μm(856μA/μm)的驱动电流,电压操作可降至0.4伏。

Soitec公司产品营销经理Manuel Sellier说:“衬底偏置是通过极化晶体管的背栅极,动态地完全控制晶体管的阈值电压(Vth)的能力。Vth是一个只有通过复杂的掺杂技术才能确定的参数,现在可以通过软件动态地编程。设计人员可以使用这一功能动态管理电路中的泄漏,并有效地补偿静态(过程)和动态变化(温度、电压和老化)。其结果是,在超低功耗下,能源效率提高了4~7倍。”

FD-SOI还支持正向衬底偏置。据意法半导体称,当衬底的极化为正时,晶体管的开关速度会更快。

然而,FD-SOI有三个缺点——成本、生态系统和采用。多年来,FD-SOI的采用有限。英特尔、台积电、联华电子等公司从未采用FD-SOI,它们表示bulk CMOS能以更低的成本实现高性能器件。例如,SOI晶圆的售价为每片370~400美元,而bulk CMOS晶圆则为100~120美元。

但FD-SOI确实具有较小的掩模次数,这可以补偿晶圆成本。根据IBS的数据,FD-SOI有22~24个掩模步骤,而类似的bulk CMOS工艺有27~29个掩模步骤。

FD-SOI也在缩小差距。IBS的Jones说:“我们现在看到的是我们所认为的bulk CMOS的极限。22nm FD-SOI的晶体管成本仅为22nm HKMG(高k/金属栅极)晶体管成本的5%。与22nm HKMG相比,22nm FD SOI的功耗降低了30%~50%,这对于可穿戴和物联网器件非常重要。”

然而,FD-SOI在EDA / IP生态系统方面落后。Jones说:“22nm FD-SOI的IP生态系统正在加强,但22nm HKMG bulk CMOS具有更广泛的IP生态系统。”

潮流正在转变。Cadence、Mentor和Synopsys已获得GlobalFoundries的FD-SOI技术的各种EDA工具认证。

Mentor总裁兼首席执行官Wally Rhines表示:“例如,集成FD-SOI的RF有一些独特的功能,用其他方法很难与之匹敌。”

FD-SOI还有其他优点。Rhines说:“虽然finFET几乎零泄漏,但动态功耗仍然存在。FD-SOI的一个优点是动态功耗。如果你能把电压从1伏降低到0.6伏,那就会降低65%的功耗。FD-SOI在动态改变功耗和平衡性能方面具有一些优势。”

其他选择

去年,英特尔推出了22nm finFET技术的低功耗版本。此后,英特尔一直对此产品保持沉默。不过,在即将举行的IEDM活动中,英特尔计划发表一篇关于22nm嵌入式MRAM技术的论文

围绕着22nm有很多活动,但目前还不清楚这个市场会有多大,哪种技术会流行。现在说22nm将成为热门还是小众还为时过早。每种技术都有自己的位置,但有些技术可能会比其他技术获得更大的发展。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英伟达,又挖了一道护城河

- 2 江波龙全球最小尺寸eMMC,为AI穿戴设备“减负”

- 3 汽车芯片需求激增,南芯科技加速推进“第二增长曲线”

- 4 Solidigm宣布与博通拓展大容量SSD控制器在AI领域的应用合作