[原创] 晶圆代工三强的NVM技术新进展

目前,GlobalFoundries(格芯)及其合作伙伴,包括三星、索尼、STM(意法半导体),在FD-SOI方面的投入力度越来越大。

作为行业3大晶圆代工厂商之一,GlobalFoundries这几年一直在大力推广FD-SOI技术。该公司于2015年提出了22FDX(22nm工艺)产品规划,并于2016年举行的第三届上海FD-SOI与RF-SOI论坛上,发布了12FDX(12nm工艺)平台计划和路线图。该公司也是业界第一个推出下一代FD-SOI技术路线图的厂家。

近期,有消息称,Globalfoundries正在研究新的非易失性存储器(NVM)技术,很有可能用在22nm的FD SOI上。

该公司首席技术官Gary Patton称,Globalfoundries已经在其22FDX制程中提供了磁性RAM(MRAM),目前正在研究另一种内存技术选择。

以上信息,是上个月在安特卫普举行的IMEC技术论坛上披露出来的。

台积电和三星等晶圆代工竞争对手正在努力推出先进的7nm工艺,还涉及射频电路和功率效率。在这种情况下, Globalfoundries会不会在先进制程工艺的竞争中落后,并开始失去客户呢?

对于这个问题,Patton强调,“我们全力推行双路线图发展战略,”

Patton表示,在双路线图发展策略的指引下,Globalfoundries将在2018下半年流片出7nm FinFET工艺产品,并在2019年实现产量,而且会在2019年进一步迭代。Patton表示,首批客户包括AMD、IBM和其他一些ASIC设计公司。

对于Globalfoundries来说,成功实现FinFET制程量产很重要,因为只有这样,才能保证其位于纽约Malta的Fab 8厂的产能利用率,并以较小的几何尺寸(例如3nm)带来收入以支付研发费用。该公司在先进制程方面的一直在投入资金,但短期内回报有限,这带给了它巨大的压力。

与此同时,Globalfoundries双路线图的另一分支,即FD SOI,也在与三星的28nm FD SOI工艺进行竞争,而后者在去年宣布将推出18nm FD SOI。对此,Globalfoundries表示,我们很高兴看到三星也参与其中,这有助于让更多的人进入该市场。

三星向18FDS进发

三星是FD-SOI的重要推动力量。由于摩尔定律发展到28nm工艺节点的时候,出现了不同以往的情况,即从28nm开始,再向更高节点发展,如20、16、14、10、7nm等等,每集成电路当中每个晶体管的成本不再下降,而是提升。

所以该公司认为28nm工艺更适合物联网(IoT)在成本、功耗和性能方面的要求,特别是MCU和传感器产品。因此,三星LSI推出了“28FDS”技术和产品,并于2016年开始量产。

三星Foundry业务部门的发展路径主要分为两条,从28nm节点开始,一条是按照摩尔定律继续向下发展,不断提升FinFET的工艺节点,从14nm到目前的10nm,进而转向下一步的7nm。

另一条线路就是FD-SOI工艺,该公司还利用其在存储器制造方面的技术和规模优势,着力打造eMRAM,以满足未来市场的需求。

实际上,三星在MRAM研发方面算是起步较早的厂商,2002年就开始了这项工作,并与2005年开始进行STT-MRAM的研发,之后不断演进,到了2014年,生产出了8Mb的eMRAM。

三星28FDSOI嵌入式NVM分两个阶段。 第一个是2017年底之前的电子货币风险生产,第二个是2018年底之前的eMRAM风险生产。并同时提供eFlash和eMRAM(STT-MRAM)选项。

代工厂在给客户进行风险生产时,制程和设计仍可能发生变化,用以优化性能并提高产量。 由于制程尚未最终确定,因此此类生产由客户承担风险。 风险生产阶段可能需要几个月的时间,这意味着eFlash将在2018年批量供货,eMRAM将在2019年批量供货。

提供28nm嵌入式非易失性存储器具有挑战性。公认的观点认为,将闪存转换为28nm是不现实的,MRAM,相变存储器(PCM)和电阻性RAM(ReRAM)等其他选项缺乏工程成熟度。

eFlash的问题包括28nm的耐用性和功耗方面的困难。

这可能是三星首先推出eFlash的原因之一,但预计客户将长期使用STT-MRAM。 由于CMOS具有工艺优势,长期来看,MRAM是最受欢迎的。

三星于2017年研制出了业界第一款采用28FDS工艺的eMRAM测试芯片。

另外,据三星Foundry业务总经理ES Jung介绍,该公司已经不像2016年那样,只是固守在28FDS,而是开始向18FDS(18nm的FD-SOI)进发。看来,三星对SOI的乐观程度有增无减,估计今年会看到更新的SOI产品推出。

商业风险

对于商业风险,Patton表示,FD SOI已经具备了足够的抗风险能力。 “现在,路线图不是问题,IP可用性也不是问题,所以,风险已经降到最低。另一个衡量标准是我们的FDXelerator合作伙伴计划,其在2016年第三季度与7个合作伙伴一起启动,现在已经增加到了47个。我们最新的目标是今年年底之前将合作伙伴增加到75个。我们已经在22FDX上进行了几次真正的IC流片,而不是测试芯片。我们预计到2020年实现12FDX的流片,并在2021年交付给客户。“

Patton强调,FD SOI上的射频元件和毫米波电路是世界级的,这使得该制程工艺非常适用于汽车雷达。 事实上,其22FDX工艺刚获得AEC-Q100二级生产认证。 作为AEC-Q100 Grade 2认证的一部分,器件必须在很宽的温度范围内长时间成功承受可靠性压力测试。

据悉,Globalfoundries还提供AutoPro平台,以帮助客户将其汽车微控制器和ASSP迁移到22FDX,并充分利用RF和mmWave功能,以及逻辑,非易失性存储器(NVM)和高压设备。

ST基于FD SOI的PCM

Globalfoundries一直关注嵌入式MRAM,但其他公司正在提供替代品,例如,三星在其28nm FDSOI上提供嵌入式MRAM和闪存选项,意法半导体(STMicroelectronics)已选择28nm FDSOI上的相变存储器(PCM),并实现了汽车应用的高端微控制器出样。STMicroelectronics的ADG总裁Marco Monti在伦敦ST金融分析师日发表讲话时透露了这一消息。

据悉,意法半导体即将推出的用于电子控制单元(ECU)的微控制器,将包含多达6个Cortex-R52处理器内核,其运行频率高达400MHz,嵌入式PCM的速度为16或32Mbytes。

Monti将该技术描述为“颠覆性技术”,具有高时钟频率的6核心芯片可提供15倍于典型单核ECU的性能。

Monti说样品已经提供给一位主要的汽车客户。

与此同时,根据报告,台积电正在其22nm FinFET工艺中提供MRAM和ReRAM的变种作为嵌入式存储器。台积电将于2019年提供嵌入式ReRAM。

报告称,这两种技术将用于22nm FinFET制程工艺。

台积电通吃eMRAM和eReRAM

台积电将与三星和Globalfoundries分别在28nm CMOS和22nm FDSOI工艺上分别提供eMRAM,然后在2019年与ReRAM产品一起实现跨越。无论是三星还是Globalfoundries都没有采取任何行动转向嵌入式ReRAM。

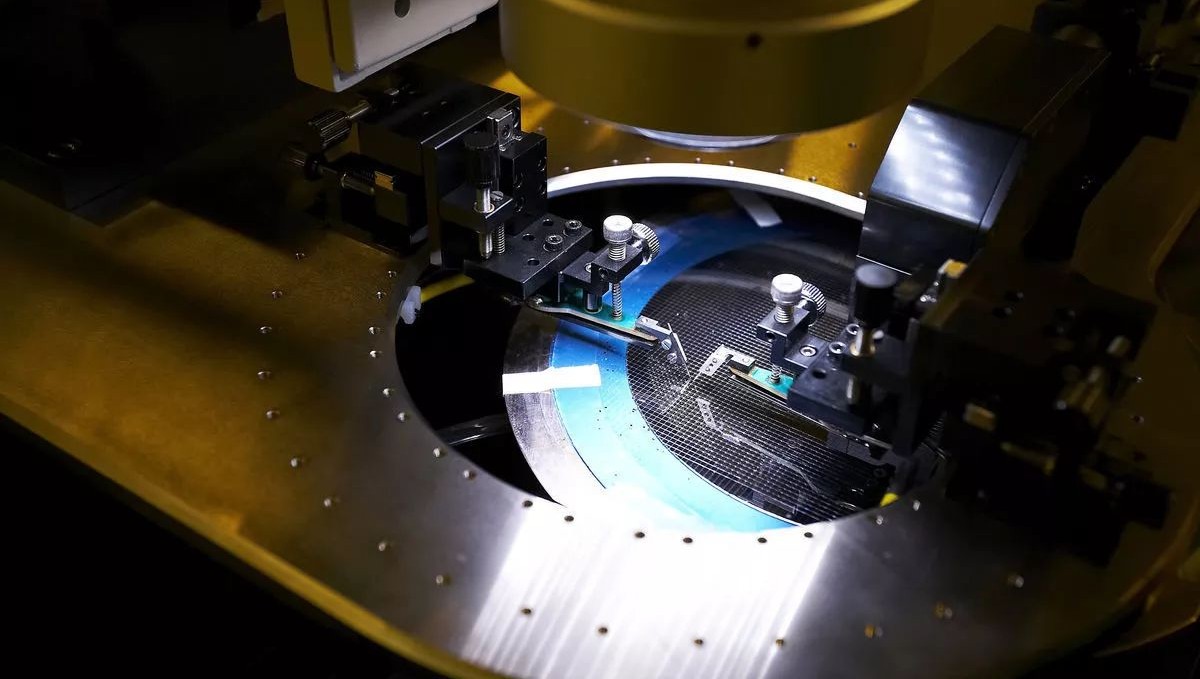

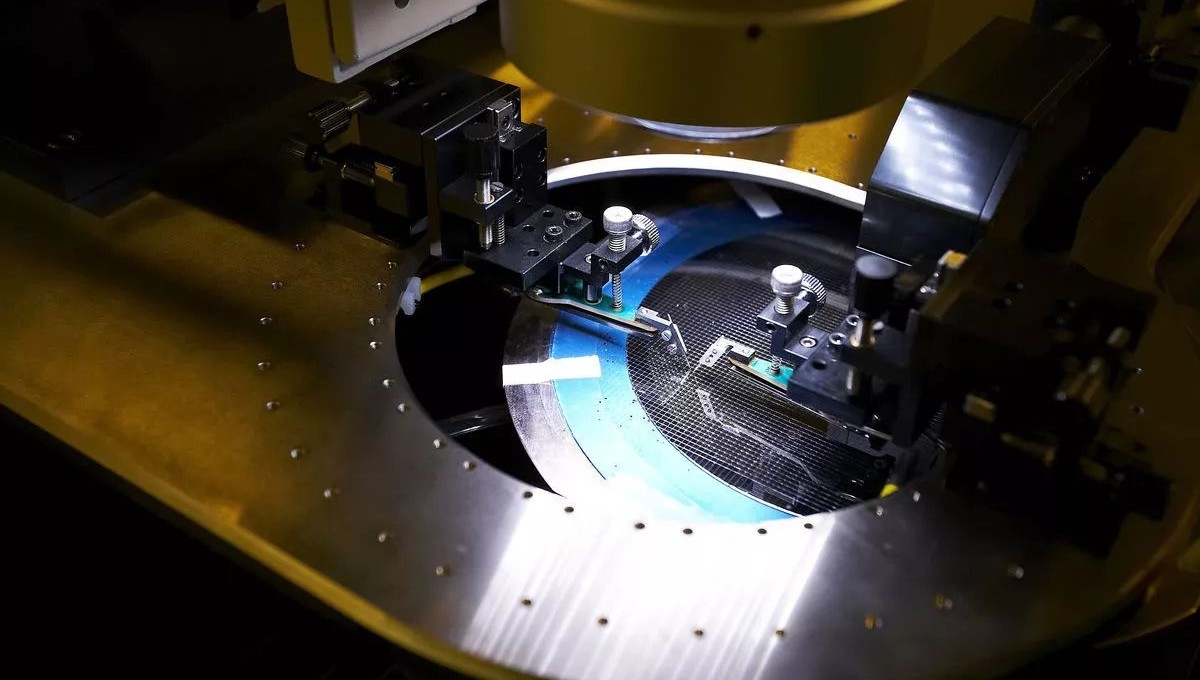

图:根据中国经济日报(EDN)的一份报告,台积电计划在2018年提供嵌入式MRAM作为SoC的非易失性存储器选项,并在2019年提供嵌入式电阻式RAM。

据台积电首席技术官Jack Sun称,台积电计划在2018年采用eMRAM芯片的“风险生产”,2019年生产采用22nm制程的eReRAM芯片。

三星已经看到恩智浦半导体采用的28nm eMRAM,Globalfoundries的22FDX eMRAM原计划于2017年提供给客户原型设计,并于2018年量产。

关于ReRAM的详细信息,未包括在台积电提供的ReRAM报告中,但该公司已发表了许多基于金属氧化物结构的ReRAM论文。

特别是台积电已经报道了在16nm FinFET的高k金属栅极(HKMG)中使用的二氧化铪高k介电材料,也可以用作电阻存储器件。虽然IEDM 2015论文的第一作者来自台湾清华大学,但也是由于台积电的多位作者。

制程工艺的下一站

“我们正在研究其他非易失性存储器选项,”Patton说,但他拒绝透露更多信息。值得注意的是,意法半导体已经选择了PCM,并且选择Globalfoundries作为FDSOI代工合作伙伴,但Patton似乎对此热情并不高。无晶圆厂芯片设计公司正在为代工合作伙伴发出大量的电阻RAM选择权。 Patton表示:“22FDX将是一个长寿命的节点,因此我希望能够改进许多技术。”

谈到市场的变化,Patton表示,2019年7nm工艺采用极紫外光刻(EUV)技术的计划一直没有变。 “我们在纽约的Malta有两台EUV生产设备,此外,还可以补充两台,我们的第三台机器已经在ASML总部Veldhoven进行着升级工作。”

虽然EUV在光源方面取得了进展,但仍然需要在光通量和线路边缘粗糙度处理吞吐量和掩模方面开展研究工作,因为仍然担心诸如掩模缺陷和开发205W兼容的保护膜等问题。

据悉,Globalfoundries将推出光学浸没式光刻技术,将能够为7nm技术提供性能增强。该公司认为FinFET 14nm和7nm是“主要”节点,跳过了10nm。

业界认为,5nm是另一个过度节点,3nm很可能是下一个完整节点。5nm可能是最后一个FinFET节点,而3nm将需要大量的晶体管工程。 这对于真正的节点改进来说将是一大笔支出,纳米片(扁平的横向纳米线,每个纳米线鳍片都有栅极环绕在周围)可能是3nm工艺节点的候选者。这是三星刚刚宣布的、在2022年或之后推出GAA工艺技术。

上个月,在美国举行的三星工艺论坛SFF 2018 USA之上,三星更是宣布将连续进军5nm、4nm、3nm工艺。 其中,4 纳米工艺仍会使用现有的 FinFET 制造技术,这一制造技术在高通骁龙 845 和三星 Exynos 旗舰芯片中均有使用。但到了3nm工艺结点,三星便开始抛弃 FinFET 技术,转而采用GAA(Gate-All-Around)纳米技术。

图:三星电子已经宣布路线图并更新其制程节点,并引入了3纳米全栅(GAA),将在2022年或之后推出。

Gate-All-Around就是环绕栅极,相比于现在的FinFET Tri-Gate三栅极设计,将重新设计晶体管底层结构,克服当前技术的物理、性能极限,增强栅极控制,性能大大提升。三星的GAA技术叫做MBCFET(多桥通道场效应管),正在使用纳米层设备开发之中。

结语

特征尺寸的微缩正在变得越来越慢,3nm技术将在7nm量产之后的三到四年后成熟。从7nm开始,进一步的研究就像是在玩儿一项极限运动,特别像在高空进行极限运动,空气会变得越来越稀薄,难度也越来越大。

文/半导体行业观察 张健

今天是《半导体行业观察》为您分享的第1617期内容,欢迎关注。

★ FPGA的新选择

关注微信公众号 半导体行业观察(ID:icbank) ,后台回复以下关键词获取更多相关内容

华虹 | 摩尔定律 | 材料 | 面板 | 晶体管 | 开源 | 韦尔股份 | 封装 | 展会

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!

点击阅读原文了解摩尔精英

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根