[原创] RISC-V成功在望?

来源:内容来自「semiengineering」,谢谢。

RISC-V 指令集架构最早是加州大学伯克利分校一个为了提升能源效率的项目,现在在整个行业中的发展势头强劲。

RISC-V 基金会的会员名册能让我们一窥推动这一发展的背后力量,其中包括谷歌、英伟达、高通、Rambus、三星、恩智浦、美光、IBM、GlobalFoundries、UltraSoC 和西门子。

SiFive 联合创始人兼首席架构师及 RISC-V 基金会主席 Krste Asanovic 说:这项技术的一大关键市场是很多公司的存储控制器。他描述说这是与内存的集成,加上插在服务器后面的 PCIe 从属设备,可以提供性能非常高的闪存存储。

另一个活跃领域是人工智能/机器学习的向量扩展。Asanovic 一直在 RISC-V 基金会领导这方面的工作,而且 SiFive 也正在开发支持 AI 机器学习的向量的内核。

他说:“很多公司都对这个领域有兴趣。现在有很多用于 AI 核心部分的硬连线的(hard-wired)专用加速器,但硬连线模块的问题在于这一领域内的算法变化非常快。这是一个非常活跃的领域。人们想要非常高效又可编程的东西,所以我们看到的用例类型既有硬连线的模块,也有增加一些补充性的东西来处理硬连线模块无法处理的部分的工作,还有试图完全使用向量来做的。希望我们正在研发的先进向量扩展能够非常接近专用功能单元,同时又能有适用于这一领域大量不同算法的灵活性。”

Asanovic 认为 AI 机器学习是 RISC-V 的一个重要注入点,尤其是因为这一领域目前还没有提供软内核(soft core)的公司。“我们定义的向量扩展比其它 ISA 更加先进。这是导致人们进入 RISC-V 领域的一个原因。”

图 1:SiFive 的 HiFive1 开发套件,来自 SiFive

第三个活跃的领域涉及到 minion 内核(即管理内核)。他解释说:“现在大多数 SoC 都需要一个 64 位的地址空间,因为它们有非常大的带有 DRAM 的内存,而且客户们也正在寻找能在大型 SoC 上‘干家务活’的嵌入式控制器。在大型 SoC 上通常有数十个这种内核,但它们需要有一个 64 位的地址空间,而且需要紧凑。现在这一领域确实还没有任何东西,所以 64 位嵌入式空间是 SiFive 重点关注的地方之一。在这一领域,英伟达已经公开宣布他们正在设计他们自己的内核,但那是他们的用例,他们也正在为这些微控制器而转向使用 RISC-V。”

Cadence 的 Digital & Signoff 组的产品管理总监 Dave Pursley 对 RISC-V 架构的扩散有相似的看法。他说:“这个领域各个地方都表现出了这种现象,到处都是,也就是整个市场。很多小型公司已经在谈论 RISC-V 了,但一些大公司对此也有准备。所以解决方案不止一种,而且它们都各有优劣。”

ANSYS 公司半导体事业部首席软件开发者 Allen Baker 说,RISC-V 规范的开放性促进了大量开放式处理器设计的发展。这些处理器有很广泛的应用范围,从适用于重型 Linux 服务器的 Berkeley Out-Of-Order Machine(BOOM)CPU 到具有 32 位 PicoRV32 的微型嵌入式微控制器。

Baker 说:一些实现已经成功流片,并且工作状态良好。从 EDA 开发者的角度看,开放式 RISC-V 设计为现代设计的构建方式提供了很有价值的见解,并且可用作工具测试的灵活测试案例。我们已经观察到了一个趋势:使用高级参数(比如内核数量、缓存大小)来实现对设计的轻松配置并使用定制 RTL 模块来扩展它们。这与由GNU 工具链生成的,几乎能提供无穷无尽的活动向量的RISC-V 软件结合起来,可以使设计分析和优化更容易获得,也更加的便宜。

实现的应用也各有不同,Cadence 的 Pursley 说:“有些人只是想以一种简单直接的方式使用指令集架构,而且你可以使用来自很多来源的 IP 来做到这一点,其中包括开源。这些正在向前推进的公司真的很喜欢它的可扩展性和可定制性。你可以去除一些代码,也可以加入一些代码。在这方面进行推进的往往是一些小公司,它们正在寻找一种为机器学习等应用得到定制指令集的快速简单方法。他们想做的基本上就是尽可能地剥离掉一切,与此同时又在激活函数等部分内增加一些东西,或者也许会根据最终应用加入加密函数、张量操作(数组和数据空间操作)等。这些都是他们希望加入的东西,取决于确切的应用。这也是 RISC-V 架构的一大优势。它允许你去掉和加入东西,同时仍然能使用已有的 RISC-V 工具链。”

Asanovic 指出在设计用于实现 RISC-V 的工具上并没有任何特定的需求。“有一大优势是我们可以用Chisel生成Verilog,并且我们知道Verilog有很多工具都可以应用)我们没有你必须理解这些 Verilog 的含义这种恼火问题(我们不用为生成Verilog难以理解而头疼)。我们生成的 Verilog非常清楚简明,可以与供应商工具良好地协同工作,所以,比如说我们不依赖花哨的 Verilog 新功能在这些工具中是正确的(Chisel生成的Verilog非常清楚简明,与EDA工具兼容性很好)。这是我们发现处理器生成器生成 Verilog 的一大好处。实际上,我们在后端和仿真流程中也都发现了这一点,客户对生成非常简明的Verilog的速度特别惊讶。它基本上可以像其它任何软内核一样使用,这是很好的。”

UltraSoC 公司 CEO Rupert Baines 说 RISC-V 有一个吸引人的地方:公司可以根据自己的特定需求优化内核设计。“实际上,每个想要架构许可的人都有许可。”

尽管有一些商业内核供应商在关注低功耗,但也有一些 SoC 公司在为自己的特定应用进行非常紧密地优化。比如说,Codasip 去年就演示了优化指令可以显著降低功耗,这是 SoC 公司降低功耗的非常明显的途径。

Tensilica 等一些公司一直在为 DSP 这么做。Baines 说,区别在于 RISC-V是一个基于行业标准的 ISA 和生态系统,而不是专门定制的架构设计。

EDA 供应商和大型芯片公司已经这么做了很多年:降低功耗的最好方法是在架构层面。实际上,功耗需要在设计过程中预先考虑,这样在调整设计时会更容易。

西门子旗下 Mentor 的设计验证技术部市场总监 Neil Hand 说:“RISC-V 吸引人的地方在于设计者可以修改指令集,可以修改实现方式,可以和不同的供应商合作。但在做这些事情时,设计者必须确保那是可行的。要确保这些东西真的有用,所以我们在 RISC-V 上的很大一部分关注重点都是检验和验证。”

几年以来,Mentor 和其它 EDA 提供商的团队都已经与 RISC-V 供应商建立了新的关系或增强了已有的关系。Hand 说:“当你想要为一项 RISC-V 设计进行低功耗优化时,这实际上就是最大的那个难题;实际上任何设计都是这样,甚至高性能优化也是如此。你必须确保这些东西仍然有效,这可不容易。”

RISC-V 设计和验证流程与其它流程(比如基于 ARM 的流程)可能会有怎样的差异?这是个显而易见的问题。其中最大的难题是知道需要检查什么以及理解如何评估设计。Hand 说:“如果你需要一个 ARM 设计,你可以选一个现成的 ARM 设计,你可以肯定自己不必担心黑箱中是怎样的。如果你需要一个标准的 RISC-V IP,如果你选择了一家优良的 IP 供应商,你也不必担心黑箱中是怎样的。RISC-V 的不同之处是你可以让有许可证的 IP 供应商修改黑箱中的内容,从而增加或修改某些东西。然后你就确实必须了解黑箱中是怎样的了。你必须验证它,而且你有各种真正有趣的技术可以用。其中大多数都直接建立在已经得到良好证明的验证标准上,需要有专业知识并且需要知道这究竟是在做什么。任何有验证难题的地方都存在机会,RISC-V 的有趣之处在于改变一种处理器设计存在大量风险。然后问题就变成了:如何解决这个风险?在低功耗方面,你可以修改一些东西,在你的设计中得到一个数量级乃至更多的性能提升,这是很有吸引力的。”

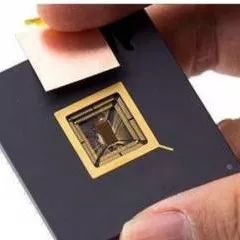

比如说,他记得 Microsemi 在 DAC 2017 上展示了其工程开发团队为一项 IoT 设计而对一款音频处理器进行了一些微小的修改。“这为它们带来了 63 倍的性能提升,这实际上意味着他们可以用更老的工艺,实现更低功耗,从而获得巨大的功耗优势。一旦他们这么做了,就必须验证其指令集是否还是一样,结果是否有效,能否在软件上运行。

图 2:Microsemi 的带有 RISC-V 内核的 IGLOO2 FPGA 架构,来自 Microsemi

尽管如此,Hand 还是坚称这个架构还处于比较早期的阶段。“我们在 RISC-V 的验证上已经完成的所有工作要么是通过 IP 合作伙伴完成的,要么就是直接通过标准方法和标准环境完成的。但真正吸引人的是:我们可以怎么实现一站式方案?当 Mentor 像西门子一样加入 RISC-V 基金会时,其很大一部分工作是理解我们怎么向这个生态系统增添价值。我们希望达到这样一个目标:一旦合规性得到了良好的定义,我们就可以开始提供现成的验证环境。只要你能做到这一点,只要你能去除定制这些内核的风险——你要通过验证来去除这些风险,那你就会看到更多采用这项技术的设计。”

想要真正实现这些预期设计的创业公司需要解决这些挑战。

Hand 说:“我从实现和验证两个方面都谈了这个问题。这正在催生一种新型的创业公司,而且这让公司能做一些相当创新的事情。你可以使用开源内核码或低成本的提供商来开发一款 IoT 设备。现在,如果有人需要找一家 EDA 供应商,而我们说:‘那没什么问题。现在你需要向我们支付 300 万美元软件费。’他们会说:‘这太贵了。’其中一小部分费用是为工具的license支付的,因而我们可以尝试将一种新的产品推向市场,这种产品具备授权成本很低的特点,不需要支付昂贵的license费用,能够修改内核意味着现在你可以做一些真正酷的东西,即使使用的是传统的节点,这显然比使用前沿节点便宜许多。它的风险更低而且现在你也可以看到我们 EDA 公司也开始同样创新——我们让人们获取他们需要的工具,从而真正将这些产品推向市场。”

尽管从当前市场中已有的情况看 RISC-V应用场景比较单一,但这个架构也在开辟一些新的市场选择,这些选择要么仍旧不成熟,要么才刚刚开始得到关注。这种设计的灵活性能增加这些领域的创新能力。但也可能增加不确定性和新的难题,因为这种架构的不同实现之间可能差异很大,为一个版本开发的 IP 在另一个版本上可能效果就会不一样。

尽管如此,RISC-V 已经站稳了足够的根基,现在有知名的公司在支持它成为系统内部的又一选择。尽管取代其它公司或处理器设计看起来还不太可能,但看起来它本身有很强的发展势头和增长空间,可以与其它供应商的处理器内核一同发展。但要真正发挥它的潜力,可能还需要在设计工具上实现新型的授权模式。

致谢

本文由电子科技大学低功耗集成电路与系统研究所黄乐天老师和明小满同学协助校对,特此感谢!

阅读原文: https://semiengineering.com/risc-v-gains-its-footing/

今天是《半导体行业观察》为您分享的第1517内容,欢迎关注。

R

eading

推荐阅读(点击文章标题,直接阅读)

★ 芯仑光电创始人兼董事长陈守顺:从汽车开始,重塑机器之眼 | 摩尔领袖志

关注微信公众号 半导体行业观察 ,后台回复关键词获取更多内容

回复 面板 ,看更多面板行业的文章

回复 比特币 ,看更多与比特币、挖矿机相关的文章

回复 晶圆 ,看晶圆制造相关文章

回复 士兰微 ,看更多与士兰微公司相关的文章

回复 ISSCC ,看《从ISSCC论文看半导体行业的走势》

回复 华为 ,看更多与华为公司相关的文章

回复 A股 ,看更多与上市公司相关的文章

回复 展会 ,看《2017最新半导体展会会议日历》

回复 投稿 ,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根