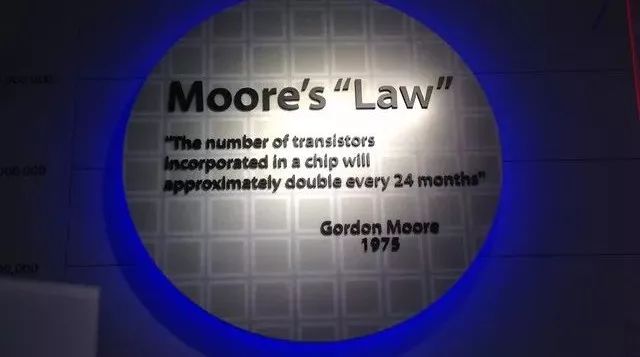

摩尔定律在7nm以下的挑战和解决办法

2017-09-15

10:48:11

来源: Ctimes

点击

7纳米制程节点将是半导体厂推进摩尔定律(Moore's Law)的下一重要关卡。半导体进入7纳米节点后,制程将面临更严峻的挑战, 不仅要克服晶圆刻蚀方面、热、静电放电和电磁干扰等物理效应,同时要让信号通过狭小的线也需要更大的电力,这让芯片设计,检查和测试更难。

KLA-Tencor:7纳米以下制程需有效降低显影成型误差

KLA-Tencor针对7纳米以下的逻辑和尖端记忆体设计节点推出了五款显影成型控制系统,以帮助芯片制造商实现多重曝光技术和EUV微影所需的严格制程公差。在IC制造厂内,ATL叠对量测系统和SpectraFilm F1薄膜量测系统可以针对finFET、DRAM、3D NAND和其他复杂元件结构的制造提供制程表征分析和偏移监控。

Teron 640e光罩检测产品系列和LMS IPRO7光罩叠对位准量测系统可以协助光罩厂开发和鉴定EUV和先进的光学光罩。5DAnalyzer X1高级资料分析系统提供开放架构的基础,以支持晶圆厂量身定制的分析和实时制程控制的应用。这五款新系统拓展了KLA-Tencor的多元化量测、检测和资料分析的系统组合,从而可以从根源上对制程变化进行识别和纠正。

对于7纳米和5纳米设计节点,芯片制造商在生产中找到叠对误差,线宽尺寸不均和热点(hotspot)的根本起因变得越来越困难。KLA-Tencor公司行销长暨资深副总Oreste Donzella表示,除了曝光机的校正之外,客户也在了解不同的光罩和晶圆制程步骤变化是如何影响显影成型的。

透过提供全制造厂范围的开放式量测和检测资料,IC工程师可以对制程问题迅速定位,并且在其发生的位置直接进行管理。我们的系统,例如今天推出的五款系统,让客户能够降低由每个晶圆、光罩和制程步骤所导致的显影成型误差。

Brewer Science:先进封装可解决现阶段制程微缩挑战

今日的消费性电子产品、网路、高效能运算(HPC) 和汽车应用皆仰赖封装为小型尺寸的半导体装置,其提供更多效能与功能,同时产热更少且操作时更省电。透过摩尔定律推动前端流程开发,领先的代工和积体装置制造商(IDM) 持续不断挑战装置大小的极限,从7 纳米迈向3 纳米。同时,众所期待由外包半导体组装和测试(OSAT) 公司开发的创新先进封装方法,提供了另一种实现这些需求的强大方法。

Brewer Science半导体制造副技术长James Lamb指出,Brewer Science 明白产业需要透过先进节点逻辑和记忆体才能达到的高度运算能力,以及需要先进封装创新的异质整合功能。目前Brewer Science持续加重投资在开发专门材料和制程来支持这两者,包括针对扇出型封装(FO) 和3D IC 制程的健全暂时性贴合/剥离材料和制程的组合,到用于先进微影制程的EUV 和DSA 材料。

台湾的半导体制造产业致力于先进节点微影,以及先进晶圆级封装的高量制造(HVM)。此外,这个地区拥有强大的显示器产业基础设施,因此具备执行面板级进阶封装制程的优势。

James Lamb认为,透过先进封装,将可延续摩尔定律的生命周期。这对于解决现阶段制程微缩技术的极限有非常大的帮助。放眼目前台湾的先进代工、研究机构和OSAT,一向被视为半导体制造的领导者。Brewer Science也将致力于支援台湾从装置设计到高量制造的创新。透过先进的材料组和制程,解决前端矽和后端先进晶圆级封装架构中的供应链需求。

责任编辑:星野

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 2 江波龙全球最小尺寸eMMC,为AI穿戴设备“减负”

- 3 英伟达,又挖了一道护城河

- 4 NVIDIA重磅出击:三台计算机助力人形机器人飞跃