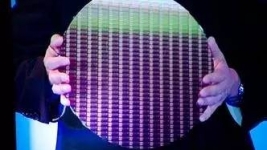

5年内进入3纳米,台积电真能做到吗?

版权声明:本文内容来自工商时报,如您觉得不合适,请与我们联系,谢谢。

台湾地区科技部长陈良基9日表示,半导体为产业竞争力核心,台积电10纳米制程已进入量产,2年后将进入7纳米,不到5年将进入3纳米、2纳米,届时将面临物理极限,必须要透过基础研究突破。

陈良基在行政院新首长上任联合记者会上表示,上任后将推动3件工作,第一支援学术研究;第二提振与推动产业技术创新,将相关技术透过研究转化成产业产品;第三建置国内相关科技研究环境,支持及维运科学园区发展。

他强调,负责科研奖助的科技部并非冷门单位,他所提供的研究是与民众未来切身相关的产品,例如目前手机上的虚拟实境与未来的人工智慧技术。

科技研究对台湾非常重要,陈良基说,他对自己立下使命标竿,期持续以科技研究创造台湾的价值,也期盼于任内首先要连结学界研发成果与科技业界紧密结合,持续打底基础研究。

以台积电为例,10纳米制程已进入量产,2年后将进入7纳米,不到5年将进入3纳米、2纳米,届时将面临物理极限,须透过基础研究突破。除半导体外,其他业界也需要基础研究支撑,科技部未来将结合学术界、产业界,共同推动产学联盟,期每年组成5-10个产学联盟。

台积电百人团队投入3nm

去年下半年,台积电共同CEO刘德音首次透露了3nm制程的进度,他表示,目前组织了300~400人的团队研发中。根据规划, 台积电的10nm、7nm都会用上EUV极紫外光刻技术,更遥远的5nm也会如此,而且还会加入新的多重电子束技术(multipe e-beam)。

这两年业界在进入FinFET时代之后速度有所放慢,Intel的14nm制程延期一两年,直接导致他们放弃了Tick-Tock战略。Intel最初对制程进展的时间表还很乐观,上面这张前几年的路线图中,10nm制程预计在2015年之后量产,但实际上是在明年下半年,延期了差不多2年,后面的7nm制程尚未公布具体量产时间,5nm等制程就更不用说了。因为就物理原理而言,7纳米的晶体管堪称物理极限,一旦晶体管的大小低于这一数字,晶体管之间就会产生所谓“量子隧穿”效应,使数据的交换紊乱,为芯片制造带来巨大挑战。也体了现在台积电深厚的技术底蕴。今年年底量产的10nm工艺上台积电就使用了EUV极紫外光刻技术,再往后的7nm、5nm也会采用这一技术,其中5nm还将使用多重电子束技术,以解决以上的物理难关。

目前的情况是,包括Intel、TSMC、三星在内,他们的10nm制程早已研发完毕,已经在准备量产。下下代的7nm制程已经在规划中了,技术研发也差不多了,已经准备在明年开始流片。再具体一些,TSMC公司联席CEO刘德音之前透露了该公司的制程路线图——2017年Q1正式量产,7nm制程投产也在计划中。

至于更先进的5nm制程,目前还在积极规划,而3nm制程也组建了300-400人的团队在攻关了。如果没记错的话,这应该是首次有半导体公司提到3nm制程进展,此前见诸报导中最多提到5nm制程,3nm制程鲜有人提及——话说连厂商现在也不能保证3nm制程到底何时推出吧,从5nm进展来看,小编估计至少是2025-2030年的事了。

技术面临的挑战

但那么先进的制程,会面临多方面的挑战,首先就是来自材料本身的极限。

产业顾问机构IC Knowledge总裁Scotten Jones认为,纳米节点将在2019年开始在某些制程步骤采用EUV技术,或许仍得采用某种形式的FinFET晶体管;至于再往下到3.5纳米节点,将会进展至采用水平纳米线(horizontal nanowire),而该节点应该会是经典半导体制程微缩的终点;其后2.5纳米节点堆栈n型与p型纳米线,可望在2025年将晶体管密度增加60~70 %。

而EUV光刻机也是一大障碍。

Globalfoundries技术长Gary Patton在2016年10月来台与本地媒体分享该公司最新技术与策略方向时则表示,他预期EUV微影技术要到2019年才会迈入成熟,而Globalfoundries在该时间点之前就会量产的7纳米制程应该不会采用该技术。

市场研究机构Semiconductor Advisors的分析师Robert Maire认为:「EUV微影真正开始量产应该是会在2020年;」他指出,台积电(TSMC)已经宣布了将在5纳米节点采用EUV微影的计划;而英特尔则可能会在7纳米采用EUV微影,与台积电的5纳米节点量产时程相当, 时程预计是在2019年。

Patton表示,人工智能、云端运算、高速通讯等应用,目前最尖端的3D晶体管FinFET制程是理想选择,目前该技术进入14纳米节点量产、已经成熟而且对高阶应用有价值;至于对运算性能要求较低、也以较低功率运作的各种嵌入式装置,例如物联网设备,其实就不一定要用到最尖端的FinFET制程,否则并不符合成本效益。

GlobalFoundries提供的其他技术选项是全空乏绝缘上覆硅(Fully depleted silicon-on-insulator,FD-SOI)制程;Patton指出,该公司准备在2017年量产的22纳米FD-SOI制程,在成本上与成熟的28纳米平面晶体管制程相当,但能达到类似FinFET制程的性能,而且功耗更低、 封装尺寸更小,也更适合与RF组件的整合。

在封装技术方面,Patton表示在过去一年来,Globalfoundries看到2.5D与3D芯片堆栈的客户需求有大幅成长的趋势;目前该公司可提供应用于32~22纳米深度沟槽式晶圆的「智能中介层」(interposer),具备去耦电容,能支持低功率应用的芯片堆栈。

在芯片堆栈技术方面,台湾半导体产业协会(TSIA)理事长、钰创科技董事长卢超群表示,过去15年来IC产业已经达成了「类似以微观建筑技术造高楼」的突破,发明3D甚至超越3D的异质性晶粒排列或堆栈方法;再加上半导体厂商在晶圆级封装技术(WLP)上的研发成果──例如台积电的整合型扇出(Integrated Fan-out,Info)与整合型扇出-封装内建封装技术(InFO-PoP)。

将IC制造与封测一体化,是工艺前进的保证,也会是让摩尔定律延续更长寿命的关键。

R

eading

推荐阅读(点击文章标题,直接阅读)

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 摩尔斯微电子推出MM8108:全球体积最小、速度最快、功耗最低、传输距离最远的Wi-Fi芯片

- 2 全球首款NFC PSSD亮相CES 2025,江波龙创新产品备受业界瞩目

- 3 VCSEL行业研究报告,洞悉市场发展趋势

- 4 一文看懂高速发展的2.5D/3D封装