7nm后,这个技术将接替FinFET延续摩尔定律

版权声明:本文来自《digitimes》,如您觉得不合适,请与我们联系,谢谢。

比利时微电子(IMEC)在2016国际电子元件会议(IEEE International Electron Devices Meeting ; IEDM)中首度提出由硅纳米线垂直堆叠的环绕式闸极(GAA)金属氧化物半导体场效电晶体(MOSFETs)的CMOS集成电路,其关键技术在于双功率金属闸极,使得n型和p型装置的临界电压得以相等,且针对7纳米以下技术候选人,IMEC看好环绕式闸极纳米线电晶体(GAA NWFET)会雀屏中选。

比利时微电子研究中心与全球许多半导体大厂、系统大厂均为先进制程和创新技术的合作伙伴;其中,在CMOS先进逻辑微缩技术研究的关键伙伴包括有台积电、三星电子(Samsung Electronics)、高通(Qualcomm)、GlobalFoundries、美光(Micron)、英特尔(Intel)、SK海力士(SK Hynix)、Sony、华为等。

针对半导体7纳米以下制程,究竟谁可以接棒FinFET技术?比利时微电子研究中心表示,目前看起来环绕式闸极纳米线电晶体(GAA NWFET)是最有可能成功突破7纳米以下FinFET制程的候选人。

比利时微电子进一步分析,因为GAA NWFET拥有高静电掌控能力,可以实现CMOS微缩,在水平配置中,也是目前主流FinFET技术的自然延伸,可以通过垂直堆叠多条水平纳米线来最大化每个覆盖区的驱动电流。

再者,比利时微电子研究中心也研究新的结构对于原来静电放电(ESD)表现的影响,且发表静电放电防护二极体,让GAA纳米MOSFETs的发展有突破,间接帮助鳍式场效电晶体(FinFET)持续往更先进制程技术发展。

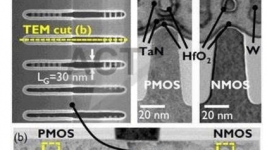

2016年比利时微电子研究中心展示了垂直堆叠、由直径8纳米的硅纳米线所制成的GAA FET,这些电晶体的静电控制由n-FETs和p-FETs制作而成,具有n型和p型元件的相同临界电压,因为积体电路技术中的关键是双功函数金属闸极的使用,使得n-FET和p-FET的临界电压得以独立设置。

且在该步骤中,P型功函数金属(PWFM)在所有元件中的沟槽式闸极使用,然后使用选择性蚀刻P型功函数金属到纳米结晶性铪氧化物(HfO2)到n-FET,随后利用N型功函数金属。

另外,针对关键静电放电(ESD)影响,比利时微电子提出两种不同的静电放电防护二极管,分别为闸二极体和浅沟槽隔离(STI)二极体。其中,STI二极体因为在二次崩溃电流(It2)与寄生电容的比率上表现较佳,所以认为是较好的静电放电防护元件。

再者,测量和TCAD模拟也证明,与块状基板式鳍式电晶体(Bulk FinFET)二极体相比,GAA纳米线二极体维持了静电放电的表现。

比利时微电子研究中心的逻辑装置与积体电路总监Dan Mocuta表示,在GAA硅质CMOS技术、静电放电防护结果方面的积体电路技术,是实现7纳米或以下制程的重要成就。

图1-(a) PWFM 被 n-FET 蚀刻后的 Top View 扫描电子显微镜(SEM)影像,和 (b) p-FET和 n-FET 在制程结束后的穿透式电子显微镜(TEM)影像 (LG = 30nm)

*〈搭载双功函数金属栅极的垂直堆栈环绕式栅极(GAA)硅纳米 CMOS 晶体管〉H. Mertens 等,IEDM 2016

**〈以本体硅环绕式栅极垂直堆栈之水平纳米线技术中的静电放电二极管〉S.-H. Chen 等,IEDM 2016

延伸阅读:台积电7nm制程新技术,速度提升4倍

在12月3~7日于美国举行的IEEE国际电子元件会议上,台积电宣布以其最新版3D FinFET电晶体,可用于生产更新一代智能手机及其他移动装置处理器的首个全新7纳米制程技术,借此正式加入全球7纳米制程技术竞争战场,并彰显其较英特尔更快的制程技术进展,显示晶圆代工厂…

OFweek电子工程网讯 据海外媒体报道,即使近年摩尔定律(Moore’s Law)进展速度趋缓,但全球各家芯片制造商仍持续开发新一代制程技术。在12月3~7日于美国举行的IEEE国际电子元件会议(IEDM)上,台积电宣布以其最新版3D FinFET电晶体,可用于生产更新一代智能手机及其他移动装置处理器的首个全新7纳米制程技术,借此正式加入全球7纳米制程技术竞争战场,并彰显其较英特尔(Intel)更快的制程技术进展,显示晶圆代工厂具备的技术优势。

根据科技网站ZD Net及EETimes报导,台积电为了展示7纳米制程技术,在会议中介绍一款由7纳米制程生产的全功能256MB SRAM测试芯片,据称该芯片存储器细胞(Memory Cell)尺寸仅0.027平方微米,可提供相较于现有16纳米FinFET制程高达4成的性能速度提升,以及高达65%的功耗节省。

台积电7纳米制程技术采用当前的193纳米浸润式微影技术(Immersion Lithography),与三星、GlobalFoundries以及IBM等竞争业者宣布的7纳米制程技术,是采用新型态极紫外光微影技术(EUV)有所差异。有鉴于EUV技术至少要等到2018~2019年以后才可能见到量产就绪,因此要等到EUV技术成熟问世可能仍需一段时间,不过EUV具备成本降低等优势。

值得注意的是,台积电7纳米制程技术并非与目前最新的10纳米制程技术做比较,而是与16纳米进行规格比较,这意谓台积电等于一次跳了2个甚至3个制程世代达7纳米技术水准。台积电在会中也透露,该公司7纳米制程SRAM良率已达50%,外媒分析称这是值得注意的成就。

外界多半认为10纳米只是一个寿命短的过渡制程技术,目前三星电子(Samsung Electronics)已开始以10纳米制程量产,首款10纳米处理器可能将于2017年初发布;GlobalFoundries计划直接跳过10纳米,直攻7纳米制程技术,并计划将从2018年初开始进行7纳米制程风险生产。

台积电则计划从2016年第4季开始采10纳米制程技术量产,预计2017年底才会见到7纳米制程导入生产,台积电强调,该公司正将重心放在协助客户尽速面向市场推出7纳米芯片产品。

由此快速的制程技术进展步伐,也意谓晶圆代工厂商已在半导体制程技术上取得技术领先优势,如英特尔已延后10纳米生产进程,并预计2017年底以后才会发布首款桌上型电脑(DT)处理器“Cannonlake”。作为此进程延后下的过渡权宜策略,英特尔改发布采14纳米制程的Kaby Lake处理器。

另外,虽然ASML的EUV系统至今仍仅在量产前的发布阶段,不过台积电已宣布自有5纳米制程节点将开始采用EUV技术。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

点击阅读原文加入摩尔精英

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根