芯片验证挑战日益突出,西门子EDA携全新Veloce CS系统迎战!

2024-04-30

18:34:56

来源: 互联网

点击

在芯片设计流程中,验证环节是至关重要的一环,它不仅可以确保芯片功能正确、提高可靠性、降低成本,还可以符合标准和规范、提升竞争力。

因此,在芯片设计过程中,验证环节正在受到更大的重视,以确保芯片的性能和可靠性得到有效保障。

尤其是在当前,我们已经迈入了芯片集成度迅速提升的阶段。随着5G、自动驾驶、人工智能等领域的飞速发展,对芯片性能的需求也急剧增加。

这种挑战驱动芯片走向更高的集成度,使得验证在大型芯片设计中的关键地位愈发凸显。过去多年来,验证成本和工作的增长速度远高于设计环节。业内有数据表明,在芯片设计中,70%都是与验证相关。

在此趋势下,为了帮助芯片设计和验证工程师更好地应对这一挑战,近日西门子EDA召开了新品发布会,推出了全新的Veloce CS系统。

西门子EDA硬件辅助验证产品管理高级总监Vijay Chobisa表示,随着芯片制造工艺尺寸的不断缩小和演进、性能和功耗的指标要求日益提升、特定用途的SoC和AI加速器架构需求,以及软件定义产品的趋势,使得硬件仿真加速和原型验证变得至关重要,芯片验证对于平台的要求也越来越高。

对此,作为功能验证工具演进方面的领先企业,西门子EDA一直致力于将更多跨领域的知识融合、集中在一起,助力客户加速芯片的设计、验证。

此次西门子EDA新推出的Veloce CS系统,整合了硬件加速仿真、企业原型验证和软件原型验证于一体,这是业界首款融合了三个系统的解决方案,希望能够为设计团队带来新的生产力和创新水平,使设计和过程完整性达到新高度。

据Vijay Chobisa介绍,Veloce CS系统包含三款新产品,解锁三款新品助推硬件加速仿真和原型验证:

Veloce CS系统针对三个平台的一致性、速度和模块化而打造,支持的设计规模从4000万门电路扩展到超过400亿门。此外,Veloce CS可根据每项任务的特殊要求选择合适的工具,以出色的可观测性和一致性高效运行整个系统的工作负载,以此加快项目收敛,并降低每个验证周期的成本。

作为新一代硬件仿真加速与企业原型验证平台,Veloce Strato CS和Veloce Primo CS在多个关键环节上都带来了数倍的性能提升:

之所以能够实现性能的大幅提升,Vijay Chobisa指出,Veloce CS系统背后的技术依托于两大行业领先的芯片——用于硬件仿真的西门子专用 CrystalX 加速器芯片,以及用于企业和软件原型验证的 AMD Versal Premium VP1902 FPGA 自适应 SoC。

其中,Veloce Strato CS硬件搭载的CrystalX芯片是西门子推出的专为硬件仿真加速而设计的一款全新芯片。CrystalX芯片提供快速、可预测的编译能力,帮助用户实现最快的设计启动和迭代;自带原生调试功能,能够让搭载这颗芯片的系统实现最佳调试效率;具有优化的连接性,帮助相关设备实现超大容量的可扩展性和高性能。

VP1902自适应SoC则是AMD最新推出的FPGA产品,在密度、连接性、容量和处理速度方面带来了巨大的提升。将AMD Versal Premium VP1902纳入Veloce Primo CS和Veloce proFPGA CS系统,提高了整体的性能和可扩展性。AMD 全球院士 Alex Starr 表示,Veloce CS还能同时与加装了AMD EPYC CPU 的 HP DL385 gen11 服务器配合运行,这既是西门子快速响应客户需求的体现,同时也表明了Veloce团队在持续不断地创新。

Vijay Chobisa强调:“Veloce Strato CS和Veloce Primo CS可在相同的操作系统上运行,并能在不同平台之间无缝移动,显著加快启动、设置、调试和工作负载执行的速度。”Veloce Strato CS和Veloce Primo CS双机运行可提高6-10倍生产力与收益。

整体而言,创新的Veloce CS架构整合了硬件加速仿真、企业原型验证和软件原型验证,将验证和确认周期加快10倍,整体成本降低5倍;Veloce CS可在所有平台复用,实现无缝迁移,将系统工作负载的执行和调试速度加快10倍;模块化且可扩展的互连刀片安装方式,无需使用固定尺寸机箱,可为各种规模的设计提供硬件辅助工具。

具体来看,作为新一代硬件仿真加速器平台,Veloce Strato CS相较于Veloce Strato+,带来了4倍的系统容量提升,5倍的性能提升和5倍的调试效率提升;作为新一代企业原型验证平台,Veloce Primo CS相较于Veloce Primo,带来了4倍的容量提升,5倍的性能提升和50倍的调试效率提升;作为新一代软件开发用原型验证平台,Veloce proFPGA CS相较于Veloce proFPGA,带来了2倍的容量提升,2倍的性能提升和50倍的调试效率提升。

此外,可扩展性和模块化也是Veloce CS系统的核心优势之一。

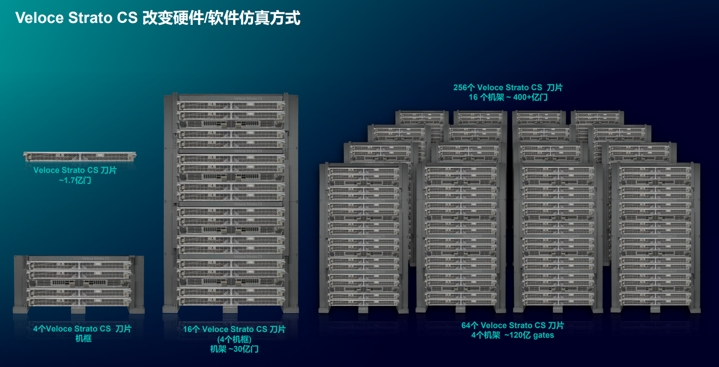

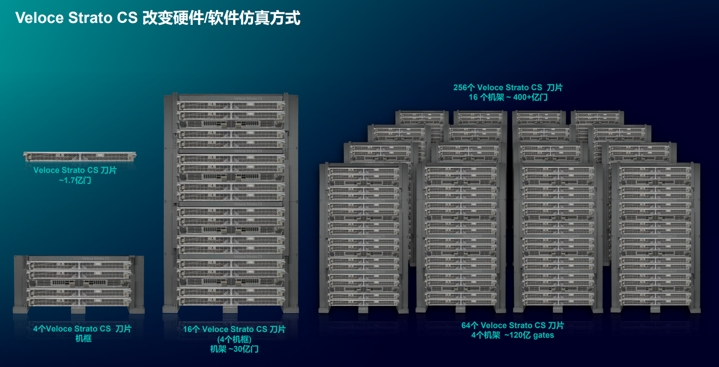

Vijay Chobisa指出,无论是Veloce Strato CS、Veloce Primo CS,还是Veloce proFPGA CS均采用可扩展的互连刀片安装方式。其中,Veloce Strato CS支持1-256个刀片模块,支持能力从4000万门电路扩展到超过400亿门电路,带来更快速高效的联合仿真调试的Co-model通性能力;

Veloce Primo CS同样可从4000万门电路扩展到超过400亿门电路;

Veloce proFPGA CS则支持从单个FPGA桌面板到多刀片机架系统,每个机架可支持高达40亿门的设计容量,过程中所有FPGA I/O用户均可访问,保证了方案具有高度的灵活性。

据悉,Veloce proFPGA CS同样基于AMD的Versal Premium VP1902 FPGA自适应SoC,打造高速、全面的软件原型验证解决方案,可从一个FPGA扩展到数百个。这种性能加上高度灵活的模块化设计,可以帮助客户显著加快固件、操作系统和应用程序的开发以及系统集成任务的执行。

此外,Veloce proFPGA CS解决方案还提供桌面实验室版本,可进一步提高使用灵活性。Veloce CS可与AMD EPYC HP DL385g11服务器同步运行。

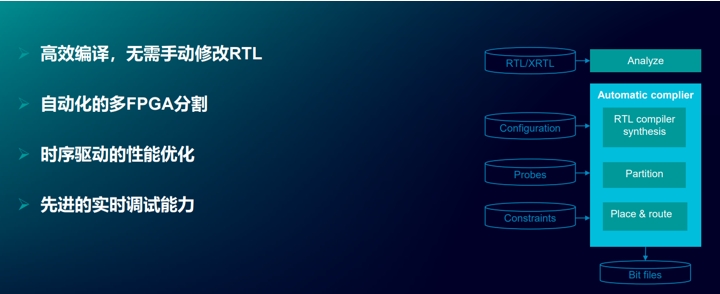

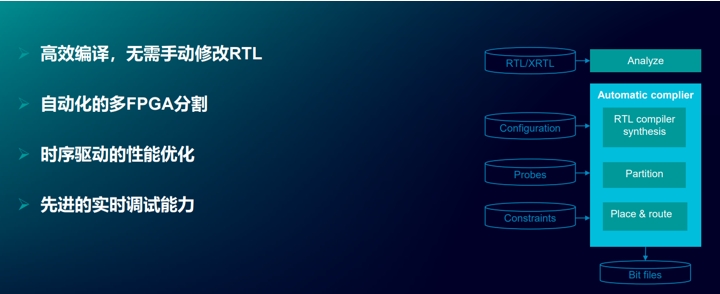

针对用于软件原型验证的Veloce proFPGA CS硬件,西门子EDA还提供用于软件原型验证的Veloce操作系统(VPS),帮助加速设计的bring up。VPS是一套高效的生产力工具,提供高效编译的能力,用户无需手动修改RTL;支持自动化的多FPGA分割;提供时序驱动的性能优化和先进的实时调试能力。

综合来看,proFPGA CS的优势首先就是快速,可高达100兆赫兹运行时性能以及高速的接口;有非常好的扩展性,整个系统的设置可以根据设计的大小或者用户数量的多少,来决定系统的大小,从单颗的FPGA到多刀片架构;而且它提供非常高的灵活性,通过VPS可以实现设计的bring up,而且可以通过手动更改线缆或者分割,以及是否要把它上传到云端,来满足终端用户的需求;需要注意的是,西门子EDA是唯一一家提供VPS操作软件的供应商,这样用户就可以快速实现这个环境,之后可以更好地优化性能。

Veloce CS系统的刀片式架构、高度可扩展性以及出色的能耗表现,能够帮助用户实现最佳TCO(整体拥有成本),主要体现在降低能源预算、与现代数据中心兼容和高系统利用率等方面。

Vijay Chobisa指出,Veloce CS系统整体能耗预算是更低的,因为Veloce CS平台使用的是风冷系统,不需要额外的液体或水冷,所以在10亿门的容量上大概是10千瓦的能耗。同时,Veloce CS系统符合数据中心要求的占地面积、承重和功率,能够和现代数据中心兼容。此外,Veloce CS系统能够大幅提升研发团队的效率,多用户、异构的工作负载可在不同的平台上全天候同步运行。

需要强调的是,仅从用电和冷却方面Veloce CS系统就可帮用户节省数百万美元。

正如上文所述,作为功能验证工具演进方面的领先企业,西门子EDA一直致力于将更多跨领域的知识融合、集中在一起,助力客户加速芯片的设计、验证。

经过Veloce系统的再度升级,西门子EDA推出的Veloce CS系统是业界首款融合了三个系统的解决方案,旨在实现更快的计算速度,更高的可扩展性、 一致性和灵活性,帮助客户达到最高生产效率和最佳ROI。

随着半导体技术的迅猛发展,面对芯片设计与验证中日益增长的挑战,业界亟需更为先进的设计验证工具。

西门子EDA在验证技术上持续创新,特别是通过Veloce CS系统的技术创新,再加上其在异构技术、云技术等方面的持续探索与突破,可以帮助芯片工程师更为高效和精确地完成设计验证。这不仅确保了产品的质量和稳健可靠性,而且为当下的芯片物理验证流程注入了创新活力,也更进一步的为整个半导体产业带来了更大的效率提升和成本节约。

因此,在芯片设计过程中,验证环节正在受到更大的重视,以确保芯片的性能和可靠性得到有效保障。

尤其是在当前,我们已经迈入了芯片集成度迅速提升的阶段。随着5G、自动驾驶、人工智能等领域的飞速发展,对芯片性能的需求也急剧增加。

这种挑战驱动芯片走向更高的集成度,使得验证在大型芯片设计中的关键地位愈发凸显。过去多年来,验证成本和工作的增长速度远高于设计环节。业内有数据表明,在芯片设计中,70%都是与验证相关。

在此趋势下,为了帮助芯片设计和验证工程师更好地应对这一挑战,近日西门子EDA召开了新品发布会,推出了全新的Veloce CS系统。

- 全球首款芯片验证三合一方案,Veloce CS优势何在

西门子EDA硬件辅助验证产品管理高级总监Vijay Chobisa表示,随着芯片制造工艺尺寸的不断缩小和演进、性能和功耗的指标要求日益提升、特定用途的SoC和AI加速器架构需求,以及软件定义产品的趋势,使得硬件仿真加速和原型验证变得至关重要,芯片验证对于平台的要求也越来越高。

对此,作为功能验证工具演进方面的领先企业,西门子EDA一直致力于将更多跨领域的知识融合、集中在一起,助力客户加速芯片的设计、验证。

此次西门子EDA新推出的Veloce CS系统,整合了硬件加速仿真、企业原型验证和软件原型验证于一体,这是业界首款融合了三个系统的解决方案,希望能够为设计团队带来新的生产力和创新水平,使设计和过程完整性达到新高度。

据Vijay Chobisa介绍,Veloce CS系统包含三款新产品,解锁三款新品助推硬件加速仿真和原型验证:

- 用于硬件加速仿真的Veloce Strato CS硬件

- 用于企业原型验证的Veloce Primo CS硬件

- 用于软件原型验证的Veloce proFPGA CS硬件

Veloce CS系统针对三个平台的一致性、速度和模块化而打造,支持的设计规模从4000万门电路扩展到超过400亿门。此外,Veloce CS可根据每项任务的特殊要求选择合适的工具,以出色的可观测性和一致性高效运行整个系统的工作负载,以此加快项目收敛,并降低每个验证周期的成本。

作为新一代硬件仿真加速与企业原型验证平台,Veloce Strato CS和Veloce Primo CS在多个关键环节上都带来了数倍的性能提升:

- 快速:与上一代硬件仿真加速器相比,使用Veloce Strato CS 执行工作任务的速度快5倍,使用Veloce Primo CS执行工作任务的速度快15倍;

- 扩展性:从4000万门扩展到超过400多亿门,专为数据中心化部署优化了的刀片式硬件架构;

- 可靠:满足现代数据中心要求的风冷、节能、占地面积(无需水冷);

- 工具一致性:可在Veloce Strato CS和Veloce Primo CS之间无缝切换。

之所以能够实现性能的大幅提升,Vijay Chobisa指出,Veloce CS系统背后的技术依托于两大行业领先的芯片——用于硬件仿真的西门子专用 CrystalX 加速器芯片,以及用于企业和软件原型验证的 AMD Versal Premium VP1902 FPGA 自适应 SoC。

其中,Veloce Strato CS硬件搭载的CrystalX芯片是西门子推出的专为硬件仿真加速而设计的一款全新芯片。CrystalX芯片提供快速、可预测的编译能力,帮助用户实现最快的设计启动和迭代;自带原生调试功能,能够让搭载这颗芯片的系统实现最佳调试效率;具有优化的连接性,帮助相关设备实现超大容量的可扩展性和高性能。

VP1902自适应SoC则是AMD最新推出的FPGA产品,在密度、连接性、容量和处理速度方面带来了巨大的提升。将AMD Versal Premium VP1902纳入Veloce Primo CS和Veloce proFPGA CS系统,提高了整体的性能和可扩展性。AMD 全球院士 Alex Starr 表示,Veloce CS还能同时与加装了AMD EPYC CPU 的 HP DL385 gen11 服务器配合运行,这既是西门子快速响应客户需求的体现,同时也表明了Veloce团队在持续不断地创新。

Vijay Chobisa强调:“Veloce Strato CS和Veloce Primo CS可在相同的操作系统上运行,并能在不同平台之间无缝移动,显著加快启动、设置、调试和工作负载执行的速度。”Veloce Strato CS和Veloce Primo CS双机运行可提高6-10倍生产力与收益。

整体而言,创新的Veloce CS架构整合了硬件加速仿真、企业原型验证和软件原型验证,将验证和确认周期加快10倍,整体成本降低5倍;Veloce CS可在所有平台复用,实现无缝迁移,将系统工作负载的执行和调试速度加快10倍;模块化且可扩展的互连刀片安装方式,无需使用固定尺寸机箱,可为各种规模的设计提供硬件辅助工具。

具体来看,作为新一代硬件仿真加速器平台,Veloce Strato CS相较于Veloce Strato+,带来了4倍的系统容量提升,5倍的性能提升和5倍的调试效率提升;作为新一代企业原型验证平台,Veloce Primo CS相较于Veloce Primo,带来了4倍的容量提升,5倍的性能提升和50倍的调试效率提升;作为新一代软件开发用原型验证平台,Veloce proFPGA CS相较于Veloce proFPGA,带来了2倍的容量提升,2倍的性能提升和50倍的调试效率提升。

此外,可扩展性和模块化也是Veloce CS系统的核心优势之一。

Vijay Chobisa指出,无论是Veloce Strato CS、Veloce Primo CS,还是Veloce proFPGA CS均采用可扩展的互连刀片安装方式。其中,Veloce Strato CS支持1-256个刀片模块,支持能力从4000万门电路扩展到超过400亿门电路,带来更快速高效的联合仿真调试的Co-model通性能力;

Veloce Primo CS同样可从4000万门电路扩展到超过400亿门电路;

Veloce proFPGA CS则支持从单个FPGA桌面板到多刀片机架系统,每个机架可支持高达40亿门的设计容量,过程中所有FPGA I/O用户均可访问,保证了方案具有高度的灵活性。

据悉,Veloce proFPGA CS同样基于AMD的Versal Premium VP1902 FPGA自适应SoC,打造高速、全面的软件原型验证解决方案,可从一个FPGA扩展到数百个。这种性能加上高度灵活的模块化设计,可以帮助客户显著加快固件、操作系统和应用程序的开发以及系统集成任务的执行。

此外,Veloce proFPGA CS解决方案还提供桌面实验室版本,可进一步提高使用灵活性。Veloce CS可与AMD EPYC HP DL385g11服务器同步运行。

针对用于软件原型验证的Veloce proFPGA CS硬件,西门子EDA还提供用于软件原型验证的Veloce操作系统(VPS),帮助加速设计的bring up。VPS是一套高效的生产力工具,提供高效编译的能力,用户无需手动修改RTL;支持自动化的多FPGA分割;提供时序驱动的性能优化和先进的实时调试能力。

综合来看,proFPGA CS的优势首先就是快速,可高达100兆赫兹运行时性能以及高速的接口;有非常好的扩展性,整个系统的设置可以根据设计的大小或者用户数量的多少,来决定系统的大小,从单颗的FPGA到多刀片架构;而且它提供非常高的灵活性,通过VPS可以实现设计的bring up,而且可以通过手动更改线缆或者分割,以及是否要把它上传到云端,来满足终端用户的需求;需要注意的是,西门子EDA是唯一一家提供VPS操作软件的供应商,这样用户就可以快速实现这个环境,之后可以更好地优化性能。

Veloce CS系统的刀片式架构、高度可扩展性以及出色的能耗表现,能够帮助用户实现最佳TCO(整体拥有成本),主要体现在降低能源预算、与现代数据中心兼容和高系统利用率等方面。

Vijay Chobisa指出,Veloce CS系统整体能耗预算是更低的,因为Veloce CS平台使用的是风冷系统,不需要额外的液体或水冷,所以在10亿门的容量上大概是10千瓦的能耗。同时,Veloce CS系统符合数据中心要求的占地面积、承重和功率,能够和现代数据中心兼容。此外,Veloce CS系统能够大幅提升研发团队的效率,多用户、异构的工作负载可在不同的平台上全天候同步运行。

需要强调的是,仅从用电和冷却方面Veloce CS系统就可帮用户节省数百万美元。

正如上文所述,作为功能验证工具演进方面的领先企业,西门子EDA一直致力于将更多跨领域的知识融合、集中在一起,助力客户加速芯片的设计、验证。

经过Veloce系统的再度升级,西门子EDA推出的Veloce CS系统是业界首款融合了三个系统的解决方案,旨在实现更快的计算速度,更高的可扩展性、 一致性和灵活性,帮助客户达到最高生产效率和最佳ROI。

- 结语

随着半导体技术的迅猛发展,面对芯片设计与验证中日益增长的挑战,业界亟需更为先进的设计验证工具。

西门子EDA在验证技术上持续创新,特别是通过Veloce CS系统的技术创新,再加上其在异构技术、云技术等方面的持续探索与突破,可以帮助芯片工程师更为高效和精确地完成设计验证。这不仅确保了产品的质量和稳健可靠性,而且为当下的芯片物理验证流程注入了创新活力,也更进一步的为整个半导体产业带来了更大的效率提升和成本节约。

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根