3D封装,全产业链缺一不可

2022-09-08

14:53:43

来源: 杜芹

点击

1971年英特尔发布的第一款CPU 4004内部晶体管数约有2300个,5年后,英特尔的Ponte Vecchio处理器将47个小芯片超过1000亿个晶体管封装到一个处理器中,过程中同时使用2.5D和3D技术。

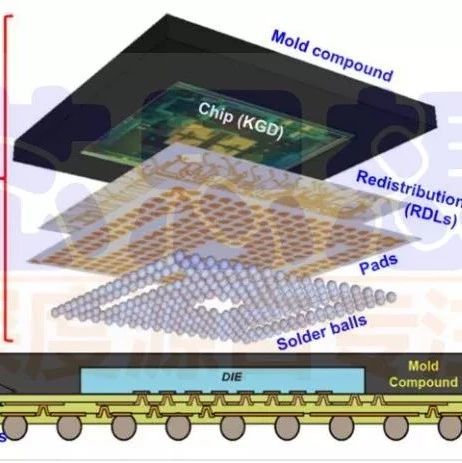

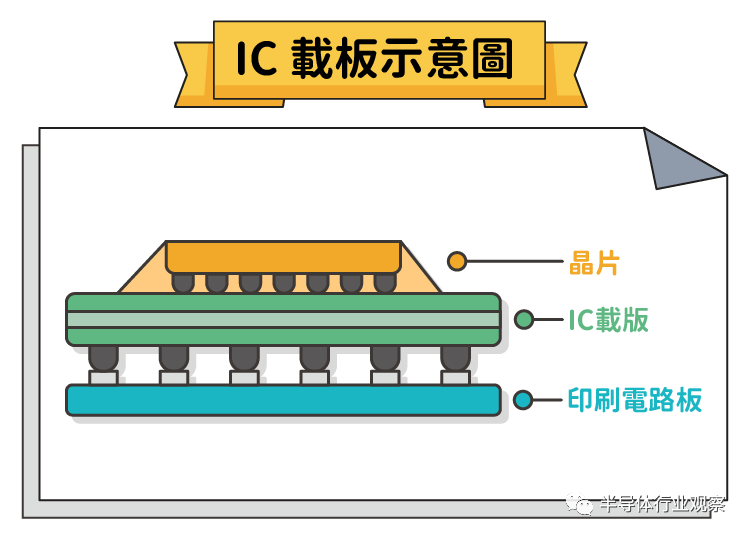

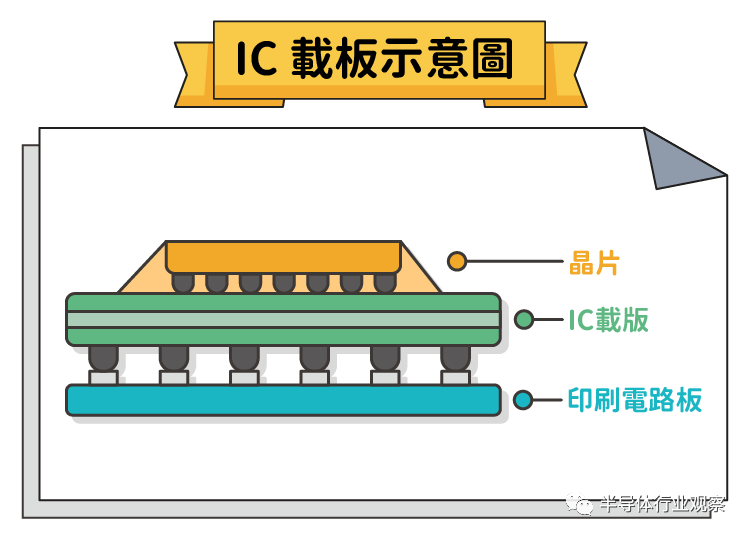

IC载板是一种介于IC半导体及PCB之间的产品,作为芯片与电路板之间连接的桥梁,可以保护电路完整,同时建立有效的散热途径。

2022年1月5日,AMD发布首款3D堆叠的桌面处理器Ryzen 7 5800X3D,益于3D芯片堆叠,相比Zen2,Zen 3的平均性能提高了19%。

2022年3月4日,AI芯片公司Graphcore的Bow IPU芯片采用3D堆叠技术将AI速度提高40%。

2022年3月9日,苹果发布了计算机最高端处理器芯片M1 Ultra,将横向排列的2枚芯片相互连接,配备了1140亿个晶体管。

种种示例表明,2.5D/3D封装技术正成为芯片性能提升的一大重要手段。通过以最低成本实现最高水平的硅集成和面积效率,3D堆叠技术的重要性正在提高。全新的应用也不断涌现,3D堆叠技术已成为满足人工智能、机器学习和数据中心等应用程序所需性能的有利可图的解决方案。

3D封装成大势所趋,技术挑战不容小觑

随着芯片微缩愈加困难,而市场对芯片高性能的追逐不减,业界开始探索在封装领域寻求突破,所以这几年,诸如2.5D/3D的先进IC封装技术已经成为代工厂、封测厂、IDM、芯片设计厂商以及EDA厂商都竞相关注的一环。

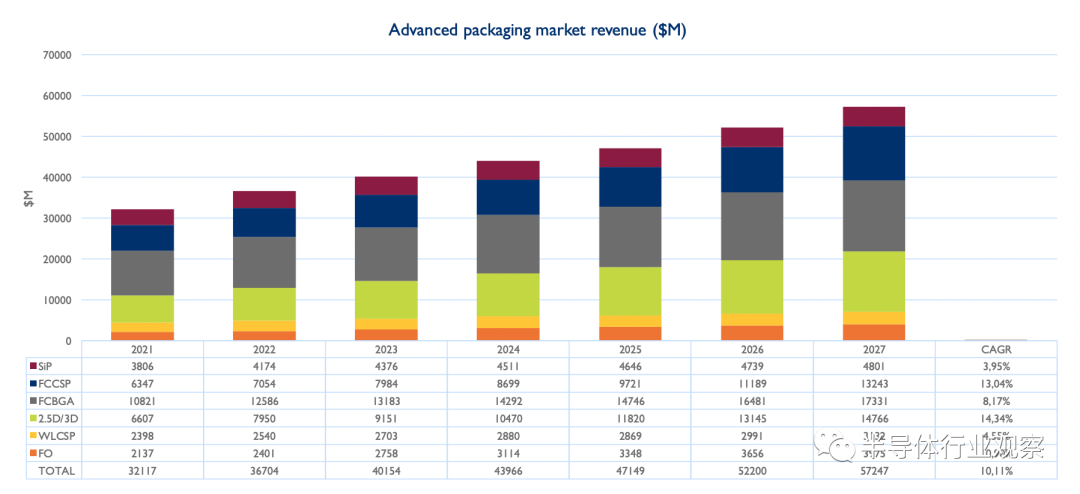

但由于成本的原因,高级封装主要用于高端、面向利基市场的应用,如HPC等。3D封装技术在HPC等主要的产业推动下迎来快速发展。据Yole 2022Q1发布的先进封装市场分析报告,先进封装市场的整体收入预计将以10.11%的年复合增长率增长,从2021年的321亿美元增长到2027年的572亿美元。而封装的各个细分类别中,尤以2.5D/3D封装市场的年复合增长率最大,从2021年的67亿美元增加到2027年的147亿美元,高达14.34%。

先进封装市场营收及预测情况

(图源:Yole)

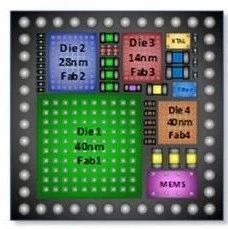

不仅仅是芯片制造过程的最后一步,封装正在成为芯片创新的催化剂。3D封装技术允许将不同的芯片如CPU、加速器、内存、IO、电源管理等像乐高积木一样拼凑起来,其主要优势是能实现更好的互连能效,减少访问延迟。例如3D封装技术允许在计算核心附近放置更多的内存,因此可以减少总的布线长度,提高内存访问带宽,改善延迟,提升CPU性能,也因此大大提高了产品级性能、功耗和面积,同时实现对系统架构的全面、重新思考。

如今,3D封装已成为行业顶尖的芯片企业如英特尔、AMD、NVIDIA、苹果等致胜的关键技术之一。虽然以3D IC为代表的异构封装已经成为未来的重点发展方向,但落实新技术要面对不少棘手的问题。相比传统的封装技术,2.5D/3D IC异构封装不仅仅是封装厂技术的革新,更为原有的设计流程、设计工具、仿真工具等带来挑战。

首先,在进行2.5D/3D堆叠之后由于集成度的大幅度提升,发热量变得更为集中,散热是一大问题;其次,在芯片、中介层、基板膨胀、冷缩的过程中,需要保障机械应力的可靠性;再者, 芯片之间的高频信号,需要满足时序、信号完整性要求等问题;最后,芯片堆叠完成后,还需要测试上层芯片是否能正常工作,接线是否良好,堆叠过程中没有被损坏等等。这些都是3D封装需要面对的难题和挑战。

3D封装是全产业链共同配合的大业

因此,在这样的背景下,3D封装就需要供应链多个环节的支持,包括代工厂、封装厂、EDA厂商、材料厂商等等。

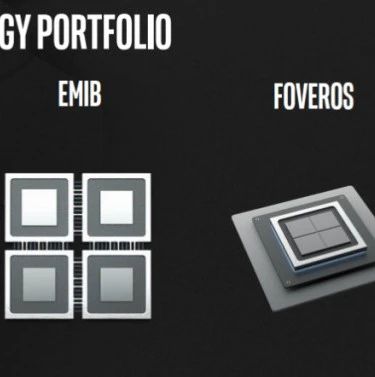

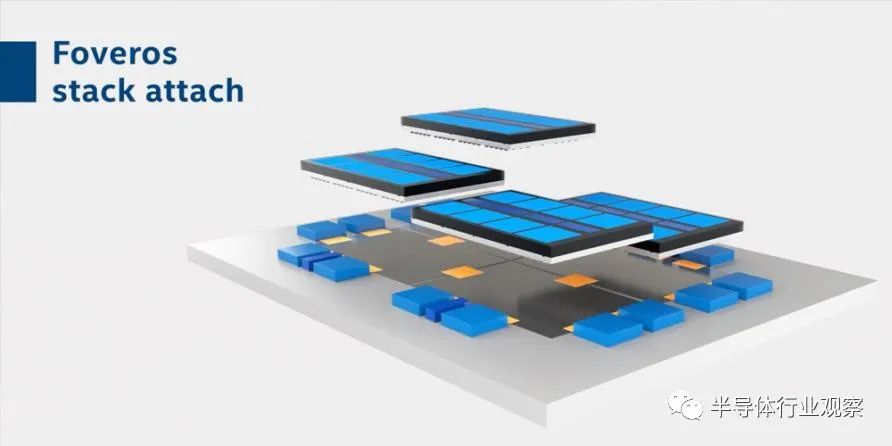

在3D封装方面,台积电、三星和英特尔这样的晶圆代工厂是中流砥柱。台积电的“3D Fabric”、英特尔的“Foveros”以及三星的“X-cube”是三大代表的3D封装技术品牌。根据市场研究公司 Yole Development 的数据,在2022年先进封装的投资排名中,英特尔和台积电分别占2022年全球先进封装投资的32%和27%,三星电子排名第四(第三是日月光)。

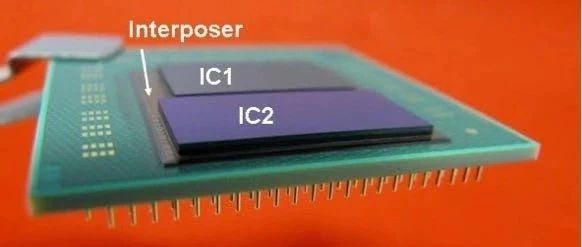

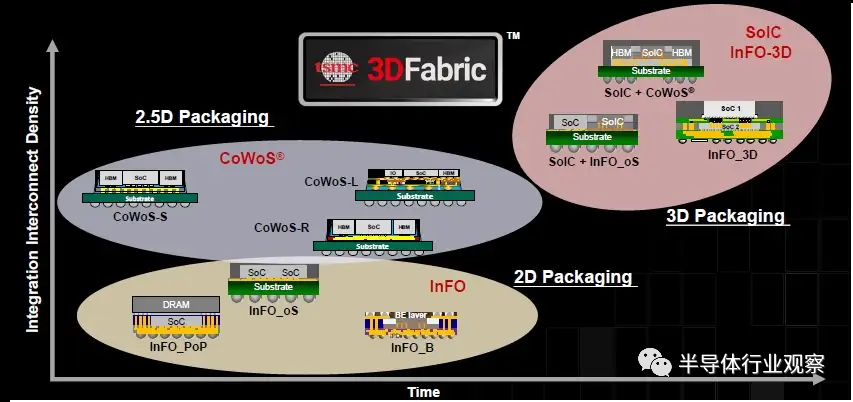

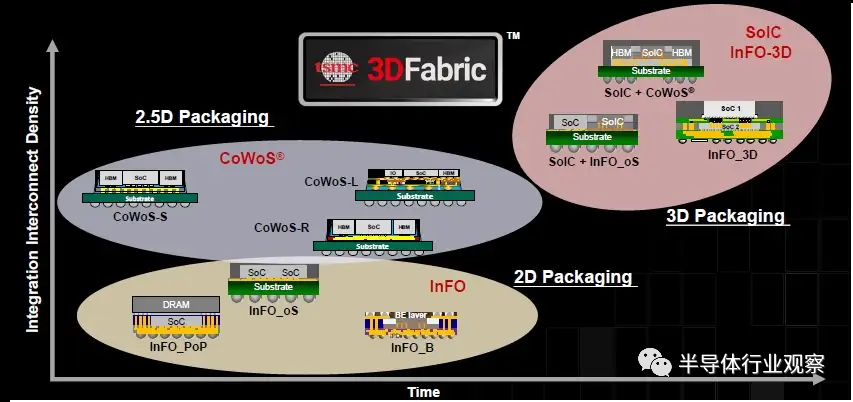

2.5D和3D封装解决方案细分领域一览

(图源:Yole)

熟悉台积电的都知道,台积电将其SoIC(系统整合芯片)、InFO(整合型扇出封装技术)、CoWoS(基板上晶圆上芯片封装) 等2.5D和3D先进封装与芯片堆栈技术整合成为了“3D Fabric”品牌。据台积电2022Q2财报说明会,目前台积电为HPC应用开发的3DIC、SoIC技术已经大部分开始被客户采用,台积电还在日本成立了3DIC中心,并于今年6月份举行了开幕仪式。

图源:SemiWiKi

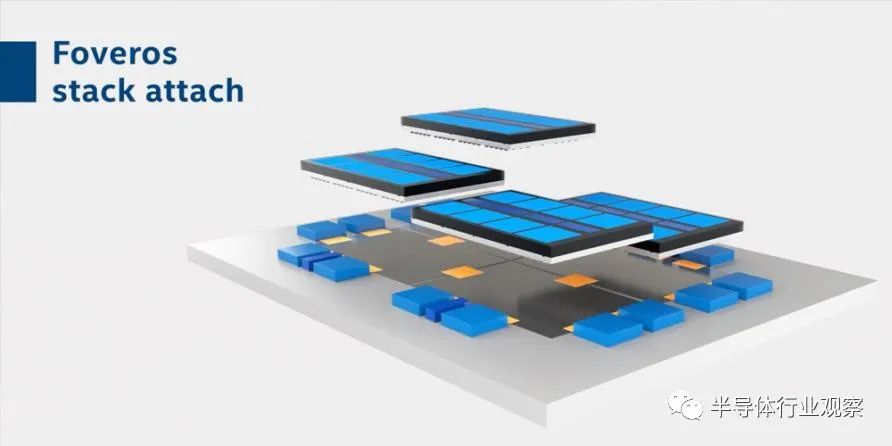

英特尔已将Foveros 3D封装技术用于其Ponte Vecchio和Rialto Bridge GPU 以及 Agilex FPGA中,英特尔表示,采用 3D Foveros 封装生产的芯片与标准单片(单芯片)芯片设计相比,在某些情况下具有极强的价格竞争力。英特尔于2021年5月宣布将斥资35亿美元用于新墨西哥Foveros晶圆厂。

图源:英特尔

三星在3D封装方面的核心竞争力来自于TSV和 PoP技术。2022年6月,三星成立半导体封装工作组,显示了三星对包括3D封装在内的先进封装的看重。

除了代工厂,传统的封装厂商也在积极向3D封装技术过渡。封测龙头日月光是较具实力的一员。2022年6月封测龙头日月光推出VIPack 3D先进封装平台,它是由六大核心封装技术组成,包括日月光基于高密度RDL 的Fan Out Package-on-Package (FOPoP)、Fan Out Chip-on-Substrate (FOCoS)、Fan Out Chip-on-Substrate-Bridge (FOCoS-Bridge) 和Fan Out System-in-Package (FOSiP),以及基于硅通孔(TSV) 的2.5D/3D IC 和Co-Packaged Optics。其他封测厂如安靠、长电科技、通富微电等也在3D封装领域蓄力。

此外,要制造3D芯片,需要在制造设备和原材料领域出现新的技术创新。关键的重要材料之一是用于多枚芯片连接的ABF载板。ABF载板是IC载板中的一种,ABF载板可做线路较细、适合高脚数高讯息传输的IC,具有较高的运算性能,主要用于CPU、GPU、FPGA、ASIC等高运算性能芯片。近几年如Chiplet等技术的发展进步,对ABF载板的需求加大,另外也存在如何提高连接速度、改善散热性和成本削减等课题。目前包括欣兴、景硕、南电、Ibiden、Shinko、AT&S等主要ABF载板供应商都进行了一定的扩产。

IC载板是一种介于IC半导体及PCB之间的产品,作为芯片与电路板之间连接的桥梁,可以保护电路完整,同时建立有效的散热途径。

图源:stockfeel

但是3D IC封装所面临的难题,有时候单靠制造端是解决不了的,需要在芯片设计的一开始就提前规划。3D IC封装将不仅仅是“封装”一个环节的事情,其更多体现在芯片和封装的协同配合。

3D IC封装最根本的挑战来自于应用工具数据库的转变。芯片通用的GDS格式与PCB使用的Gerber格式有着根本上的差别,需要重新整合解决方案,以满足先进封装要求。此外,规模增长带来的复杂性也是需要重点关注的问题。在做多晶粒(multi-die)时,面对日益庞大的系统,需要考虑能否承担并验证。还有一个值得注意的就是设计规划,将多个芯片怎样连接起来,用哪些工具去规划,哪个文档是正式“黄金参考”版本,都是需要事先确立的。只有确立了规划,才能够进行后续的设计、验证。此时就凸显出EDA工具的重要性。

而这些正是西门子EDA这样的EDA厂商的价值所在,西门子EDA有一套成熟的端到端的EDA解决方案,结合其Xpedition, HyperLynx和Calibre技术,实现了快速有效的设计至GDS 签核。例如,在芯片仿真验证阶段,结合西门子HyperLynx和Calibre系列工具,可以处理die、package和PCB仿真的协同问题,而不再是专注于单一设计领域;在芯片封装设计布局阶段,西门子Xpedition Package Designer提供高效能的先进封装技术支持,以及智能布局功能,能提升封装设计布局效率并缩短布局时间;在测试阶段西门子EDA Tessent 工具平台基于工业分析,为3D IC提供集成并且流畅的EDA解决方案,通过灵活而完备的测试组合,实现提高测试覆盖率、降低测试成本、追踪良率问题的目标。

与此同时,EDA厂商与代工厂和封装厂的协同合作也愈发重要。在这方面,西门子EDA已与台积电、三星以及日月光等积极展开合作,为他们提供生态上的支持。

其中,早在2020年,西门子EDA就获得台积电“联合开发3DIC设计生产力解决方案”年度OIP合作伙伴奖,2021年双方在云上 IC 设计以及台积电 3D 硅堆叠和先进封装技术系列——3DFabric™方面达到了关键里程碑。再者,西门子EDA的高密度先进封装解决方案已通过三星Foundry最新封装工艺认证。西门子EDA还利用其Xpedition™ Substrate Integrator 软件和 Calibre® 3DSTACK 平台与日月光推出新一代高密度先进封装设计的支持技术,据日月光集团副总裁洪志斌博士表示:“双方的合作使客户可以减少2.5D/3D IC和FOCoS的封装规划和验证周期,在每一次设计周期中,大约可以减少30%到50%的设计开发时间。”

结语

随着整个产业链逐渐日趋完善,并且不断推出各领域新的支持的技术,如2.5D和3D封装技术将成为接下来芯片性能提升过程的中流砥柱,也将是半导体产业的未来。3D封装正在改变半导体世界,这一次将引起全产业链的变革。

责任编辑:sophie

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 首次!芯联集成2024年度毛利率转正

- 3 摩尔斯微电子推出MM8108:全球体积最小、速度最快、功耗最低、传输距离最远的Wi-Fi芯片

- 4 收藏,半导体一些术语的中英文对照