芯片固定成本飙升:半导体成为高风险游戏!

来源:内容由半导体行业观察(ID:icbank)编译自semianalysis , 谢 谢。

我们正处于半导体设计的复兴之中。世界上几乎每家大公司都有自己的硅战略,因为它们试图实现垂直整合。也有比以往更多的芯片初创公司。该行业正在迅速从使用英特尔 CPU 转变为一切。

随着摩尔定律的放缓,设计正涌向异构架构,这些架构更适合其特定任务。如果解决了软件挑战,专业化芯片的性能将大大优于 CPU,但这种专业化策略也有不利的一面。固定成本正在爆炸式增长,并且这些设计的数量大幅下降。半导体是一个规模经济的行业,随着每一代新技术的发展,这一点变得越来越明显。

晶圆制造是一个通过光刻定义特征并通过沉积、蚀刻和其他工艺步骤构建特征的循环。半导体的前沿涉及使用 60 多个独特的光刻层和伴随的步骤。这些层中的每一层都需要一个独特的光掩模。所有掩码的集合称为掩码集(mask set)。这些光掩模组将设计从芯片架构师转变为物理特征。用大多数外行的话来说,掩模组可以被认为是一组包含芯片设计的模板。每个独特的芯片设计都需要自己的掩模组。

有许多巧妙的技巧被用来降低设计该芯片的成本,但将该设计推向市场的最大障碍是掩模组的成本。在 90nm 到 45nm 的代工工艺节点上,掩模组的成本约为数十万美元。在 28nm 时,它超过了 100 万美元。对于 7nm,成本增加超过 1000 万美元,而现在,随着我们跨越 3nm 的障碍,掩模组将开始推向 5000 万美元的范围。

晶圆价格正在上涨,但掩模组的成本增长得更快。来自 IC Knowledge 的上图说明了这个难题。跨工艺技术时代的产量必须显着提高,才能利用晶体管缩小带来的经济改善。

有些人的印象是晶体管成本在 28nm、7nm、5nm 等各种工艺节点停止下降。声称晶体管成本已经停止下降并开始增加的人数似乎比摩尔定律快了一倍。需要明确的是,即使在 5nm 甚至 3nm 代工厂,每个晶体管的成本也会继续下降,但这归咎于那些拥有大晶圆量的企业。芯片设计很昂贵,但与 IDC 和麦肯锡所声称的相差甚远。请参阅下面的错误图表。

我们与多家芯片初创公司合作,他们在台积电 7nm 上创造了 5000 万至 7500 万美元的领先芯片。该成本包括他们的整个软件、设计和流片成本。这些成本将根据制造的芯片类型而有很大差异。

随着行业在工艺技术方面的进步,成本不断增加。更多的公司将没有足够高的产量来摊销与掩模组相关的固定成本,以利用每晶体管成本的提高。

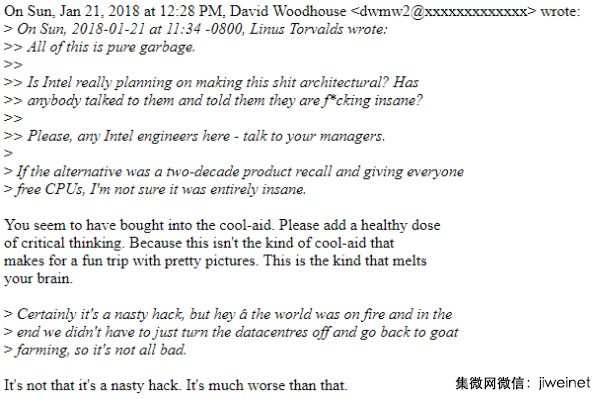

刚刚开始设计芯片之旅的初创公司和非半导体公司不仅要应对达到更高水平的收支平衡,还必须应对巨大的风险。最大的单项成本是design validation和verification。如果validation和verification pipelines达不到要求,公司将面临大量产品延迟的风险。这些问题也适用于业内最大的企业。

英特尔在制程技术方面落后,但随着台积电在 3nm 上的进展缓慢( stumbles ),如果英特尔能够快速提升节点,Intel 4 和 3 制程节点可能会与台积电的最佳节点竞争。即使英特尔在制程技术上与台积电相提并论,他们还有其他可能被证明无法克服的障碍。在我们看来,英特尔面临的最大问题是他们的design validation和verification流程。为了演示,让我们看一下英特尔的数据中心芯片。

英特尔目前的服务器芯片 Ice Lake 于 2018 年 12 月首次上电。产品发布时间为 2021 年 4 月,直到 2021 年第三季度/第四季度才开始量产。英特尔可能首先在2018 年初为 Icelake 提供流片(聚合 IP 开始制作掩模组)。在tape-in 之后,tape out 是指第一批晶圆使用新创建的掩模组通过晶圆厂。英特尔完成了这些晶圆并封装了芯片,并于 2018 年底开始测试。这是该芯片的第一次spin ,但 Ice Lake 需要许多新的spin 才能完全发挥作用。每次新的spin 都需要至少一些新的掩模,进一步增加了开发成本。

英特尔的下一代服务器芯片 Sapphire Rapids 在validation和verification方面也面临着类似的问题。Sapphire Rapids 设计的第一个版本于 2020 年 6 月启动。现在,在 2022 年年中,英特尔仍在修改设计和掩模组,因为他们在设计早期没有发现问题。这主要是由于validation和verification问题。Sapphire Rapids 似乎将在 2022 年晚些时候推出,但现在预计将在 2023 年初实现销量增长。

英特尔的validation和verification问题大大增加了成本并延长了时间。对英特尔来说,不得不修改掩码对成本来说并不是一个大问题,因为它们的数量很大,但延迟对其竞争力非常有影响。每个新版本都需要至少一些新的掩模,通过晶圆厂运行晶圆并封装芯片。这个过程需要几个月的时间。根据我们在Angstronomics的朋友的说法,对于 Ice Lake,它需要 Intel 6 版本才能发布,而 Sapphire Rapids 看起来需要 7版本。

相比之下,在 AMD 和 Nvidia 等行业中被认为是最好的领先设计公司只需要一小部分时间。他们都只需要一小部分时间。众所周知,Nvidia 拥有非常广泛的自定义模拟、验证和验证流程,在许多情况下甚至需要不到一年的时间。英特尔可以承受这些问题,因为它们是如此强大,即使这是导致它们落后的原因。有巨大的努力来检修和解决这个问题,我们希望英特尔能够做到,但这是一个很大程度的怀疑。

现在想象一下,如果一家非半导体公司的初创公司或全新的芯片设计团队跌倒了,他们会发生什么。这些延迟可能会扼杀一个特定的芯片项目,比如 Meta 和微软。这些延迟甚至可能扼杀整个公司或战略。随着半导体设计复兴的蓬勃发展,它不会一帆风顺。

失败的设计将有一条散落的路径。更多成熟的公司可能会有一些完全垂直的设计,但他们也会转向与博通、Marvell、英特尔、AMD 等公司的半定制交易。由于预算更加有限,初创企业的情况要艰难得多。我们认为 AI 芯片初创公司的洪流很可能是它首先出现的地方。多家知名人工智能初创公司已经裁员,而这仅仅是个开始。尽管如此,仍有许多初创公司会蓬勃发展并赚很多钱。

毫无疑问,这是一个非常高风险的游戏。

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3111内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 共筑国产汽车芯片未来,中国汽车芯片联盟全体大会即将开启

- 2 国产EDA突破,关键一步

- 3 Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 4 思尔芯第八代原型验证S8-100全系已获客户部署,双倍容量加速创新