[原创] 晶圆代工巨头押注“背面供电”

任何技术的研发都是持久而又艰辛的,尤其在给摩尔定律续命这条路上,更是步履维艰。2022年6月30日,在一片质疑和欣喜声中,三星GAA 3nm正式宣布量产,然而早在2002年,三星就已经对GAA保持关注并投入研发,20年的研发和投入换来全球首个3nm的量产。

作为接替Finfet的晶体管结构,GAA往往被认为是3nm之后的芯片制造方向,但显然这也只是芯片发展道路上的众多选择之一。面对神秘而又未知的芯片未来,研发人员天马行空的创造力,总会带来很多奇思妙想,比如各种3D堆叠、chiplet、高金属替代,又或者是本次文章的主角: 背面供电 。

芯片未来选择

何为背面供电(BSPDN),顾名思义,就是将芯片上的电源线转移到晶圆空置的背面,可以看作是IMEC开创的“埋入式电源轨”(BPR)的升级版本。虽然当前热度不及chiplet、3D堆叠,但背面供电的优势却十分明显,applied materials称,“背面供电网络”将绕过芯片的 12 个或更多布线层,以将电压降降低多达 7 倍。

电压降降低对于未来芯片来说意味着什么,为什么能让“背面供电”成为未来选择之一?想要解开这些问题,或许需要从了解芯片制造开始。

众所周知,SoC 最初只是一块裸露的高质量晶体硅,晶体管位于硅最顶部,为了形成具有计算功能的电路,需要将晶体管与金属互连,而这些互连则是在被称为“堆栈”的层中形成,当前随着晶体管数量呈指数型增长,堆栈层数也越来越多,如今可能需要 10 到 20 层堆栈才能为芯片上数十亿晶体管提供电力和数据。

按照当前传统的芯片电源互连方式,即通过晶圆正面的后道 (BEOL) 处理制成,那么为了能从SoC中获得电源和信号,就需要电线网络将电压从片外稳压器通过芯片的所有金属层传输到每个逻辑单元。简单地说,为了给晶体管供电,电子必须穿过 10 到 20 层越来越窄、越来越曲折的金属层,才能达到最后一层的局部导线。

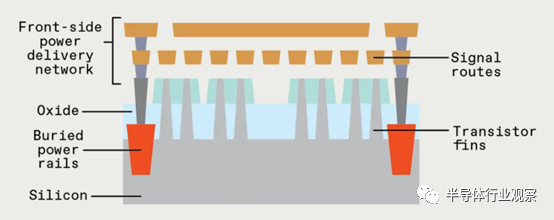

传统电源互联方式 图源:IEEE

在这电流传输过程中,问题也开始显现出来,电流每经过一层金属层,布线电阻的存在就会损耗一部分电源电压。目前在SoC 中,设计人员的预算通常能够承受稳压器和晶体管之间 10% 的压降。

但随着芯片性能要求越来越高,晶体管越来越小,所需提供电流的互连越来越紧密、越来越精细,在光刻技术从DUV走向EUV的同时,线路和过孔的进一步拓展也将导致更高的电阻和布线拥塞。在这种情况下,想要使用现有的电力传输技术扩展到3nm以上,稳压器和晶体管之间的电压降甚至有可能达到50%。

高达一半的损耗率,对于芯片设计来说,显然不可取。

站在现在看向可预见的未来,毫无疑问,此后每个工艺节点的增加幅度都是前所未有的,而设计人员所面对的将是不断增高的互连电阻和不断缩小的芯片空间。如何在特定的电线宽上去对抗日渐增加的电阻,向数十亿个晶体管提供电流,成为高性能 SoC 设计的主要瓶颈之一。

上文提到的“埋入式电源轨”技术,就是在此背景下应运而生。该技术原理是在晶体管下方而不是在晶体管上方建立电源连接,目的是创建更粗、电阻更低的轨道,并为晶体管层上方的信号承载互连腾出空间。

埋入式电源轨电源互联方式 图源:IEEE

2019年,Arm 研究人员就提出了一种使用埋入式电源轨的CPU设计方案,在设计中,Arm 工程师发现,埋入式电源轨可以建立一个比普通前端供电网络效率高 40% 的电力网络。但同时他们也发现,即使使用具有前端供电功能的埋入式电源轨,提供给晶体管的总电压也不足以维持 CPU 的高性能运行。这就意味着,仅仅使用埋入式电源轨依旧不能满足所需电流,仍然必须从晶体管上方传输电力,该设计虽然实现电压裕度了,但是工程师却不得不牺牲芯片性能来降低功耗。

为进一步改善电力输送,IMEC 开发了一种补充解决方案,将整个电力输送网络从芯片的正面移动到背面,“背面供电”技术就此诞生。

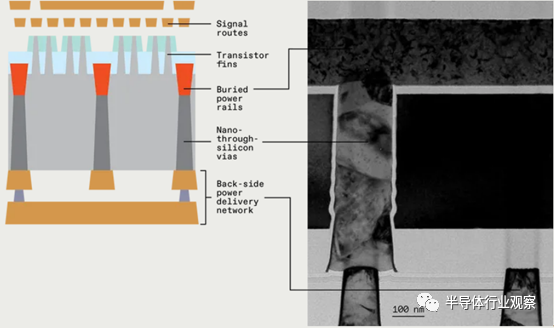

“背面供电”技术需要将晶体管下方的硅减薄至500nm或者更小,由垂直穿过硅背面的微米级通孔供电,将硅的背面连接到埋入电源轨的底部。

背面供电网络电源互联方式 图源:IEEE

IMEC在Arm模拟芯片设计中发现,只需让纳米TSV(nTSV) 彼此间隔小于 2 微米,就可以设计一个背面 PDN,其效率是具有埋入电源轨的正面 PDN 的 4 倍,是传统前端PDN 效率的 7 倍。

更重要的是,背面供电网络还能为芯片上方的信号路径留出了更多空间,能让芯片制造商将更多晶体管挤入相同的硅片区域。这点对于实打实“寸土寸金”的晶圆来说,确实吸引力够大。

两种供电方式的对比 图源:IEEE

在2021年6月 VLSI 研讨会上,IMEC表明,背面供电是向电路供电的最有效方式,在很大程度上改善了传统设计BEOL 中的电阻增加引起的电源电压压降,并发表了五篇论文展示了在开发实现背面供电网络所需的关键技术构建模块方面取得的进展,以此证明背面供电网络可作为摩尔定律的结构缩放助推器。

而在日前刚举行的IEEE VLSI 技术和电路研讨会上,IMEC还对使用nTSV降落在埋入式电源轨上的背面供电布线方案进行首次实验性演示。

IMEC CMOS 设备技术总监 Naoto Horiguchi对此表示,通过测试,证明nTSV 位于晶圆正面定义的埋入式电源轨上,不仅不会因背面处理而降低FinFET 的性能,还由于具备严格的覆盖控制,实现了200nm 的紧密间距,不占用标准单元的任何区域,确保了芯片技术进一步向 2nm 及更远的方向扩展。”

IMEC 3D 系统集成研发副总裁 Eric Beyne也指出,在2022 年的 VLSI 论文中,实现了将背面处理与 2.5D金属-绝缘体-金属电容器 (MIMCAP) 相结合,该电容器用作去耦电容器。2.5D MIMCAP 将电容密度提高了4到5倍,进一步改善了 IR 压降。他们的工作表明,背面供电可以通过新的设计选项创建一个非常动态的设计空间,帮助解决传统2D IC缩放的缺点。

除了扩展 3D-SOC 设计的可能性之外,BSPDN 还被提议用于单片单芯片逻辑和 SRAM 片上系统,帮助进一步的器件和 IC 缩放。

但要想将背面供电技术应用在批量生产中仍有很长的路要走,需要面对众多材料、制造中的挑战。毕竟,用于埋入式电源轨和nTSV 的金属材料的最佳选择对于可制造性和电效率来说至关重要。

走向背面供电的代工巨头

即便当前“背后供电”技术还未成熟,但在技术优势的吸引之下,英特尔、台积电等晶圆制造巨头自然不会错过,纷纷开始押注布局。

英特尔在去年7月的Intel Accelerated上公告了两项创新技术,一个是RibbonFET,其实就是在文章开头提到的GAA晶体管,另外一个就是背面供电技术,英特尔将其命名为PowerVia。

据了解,英特尔的PowerVia技术是业界首创的解决方案。英特尔公司逻辑技术开发部高级副总裁兼联席总经理Sanjay Natarajan 博士表示,PowerVia可以解决困扰硅架构数十年的互连瓶颈问题。

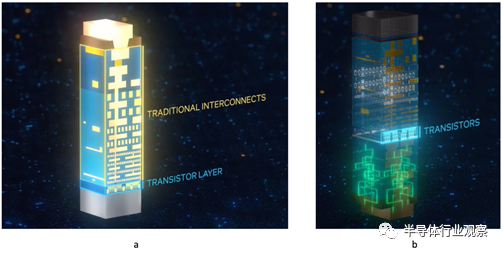

图源:英特尔

在Sanjay Natarajan 博士看来,使用 PowerVia,可以实现信号线和电源线的分离。而信号和电源则会使用英特尔的另一项创新技术连接到晶体管层,即纳米硅通孔 (TSV),这类TSV 比当今最先进的 IC 封装中使用的 TSV 小 500 倍。

英特尔 RTL 设计工程师 David Kanter 指出,“我们相信 PowerVia 具有重新调整行业的潜力,并且与 2001 年从铝到铜的转变一样具有里程碑意义”。这句话足以证明PowerVia技术的重要性。

目前,关于PowerVia技术的应用,关键的转折点或许将从2023年开始的A系列工艺节点出现。英特尔方面表示,其20A工艺(相当于2nm),从2024年中期开始,将使用RibbonFET和PowerVia这两种突破性技术,而这两项技术也将共同确保英特尔继续成为全球领先的芯片供应商。

从这方面来看,PowerVia技术或许已经成为了英特尔在晶圆代工领域逆风翻盘的“关键武器”之一。

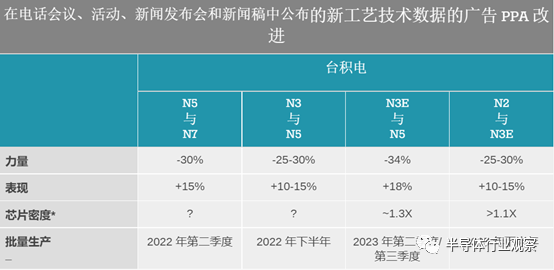

再看台积电方面,在6月初首次推出其N2(2 纳米级)工艺技术时,台积电透露了其2nm节点的两大显著优势,同英特尔一样,也是纳米片栅环 (GAA) 晶体管和背面电源轨。

不过与英特尔不同的是,台积电并不打算在其 N2 工艺技术的第一代中同时使用 GAA 晶体管和背面电源轨,第一代 N2 将仅采用GAA,而背面供电技术则会在更高版本的N2节点中实现。

虽然台积电方面并没有过多地说明不将背面供电应用在其初始 N2 节点的具体原因,但是其也曾透露,由于背面供电技术最终将增加额外的工艺步骤,在首次尝试 GAAFET 时更希望能避免这些额外的步骤。

由此可以看出,台积电对于N2 的的创新还是采取较为谨慎的态度,与N3E 节点相比,台积电第一代N2性能预计提升10% 到 15%,但在相同的速度和复杂性下,功率却下降 25% 到 30% 。

图源:anandtech

图源:台积电

从台积电透露的时间表来看,其第一个N2节点预计将于2024年或2025年推出,与英特尔20A工艺时间相差无几。不过如此谨慎的态度是否影响台积电的发展步伐,而没有背面供电技术的GAA工艺在与英特尔对撞时,又是否会处于劣势地位?

这一切,或许还需要时间给我们答案。

写在最后

虽然“背面供电”与GAA的碰撞能给芯片性能带来怎样的提升我们还未曾知道,不过可以预见的是,在未来,背面供电技术或许会成为通往先进制程不可缺少的必经之路。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3111内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根