三大闪存巨头的新“武器”

来源:内容由 半导体行业观察(ID:ic bank)编译自techinsights,谢谢。

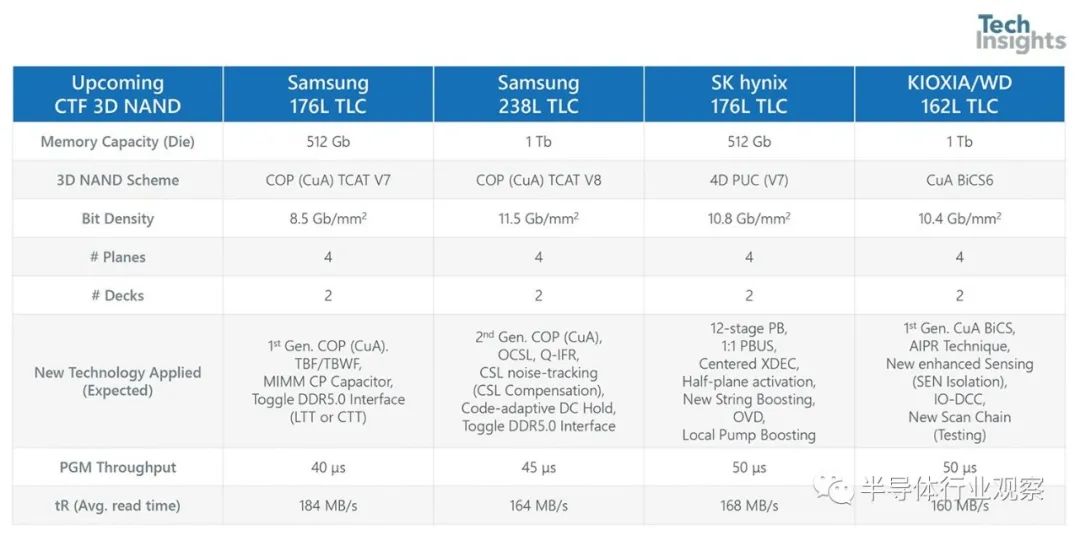

现在,三星、SK hynix、KIOIXA 和西部数据 (WD) 等其他领先的 3D NAND 厂商已经完成了风险产品阶段,并刚刚进入大批量产品阶段,SSD 应用的良率更高。162L/176L TLC 芯片具有 512Gb 或 1Tb 内存容量,可用于 UFS(移动)或 cSSD/eSSD 产品(例如 SK hynix Platinum P41 PCIe NVMe Gen4 SSD)的 TLC 或 QLC 操作。

美光去年领先于其他厂商发布了 176L 3D NAND 产品,而其他厂商似乎在 NAND 供应不足的市场气氛中平息了呼吸。关于芯片的性能,所有 162L/176L 3D NAND 芯片看起来都相当有竞争力。例如,芯片的程序吞吐量为 40 ~ 50 μs,平均读取时间 (tR) 为 160 ~ 184 MB/s。

再次,美光首先展示了 176L CTF CuA 3D NAND 芯片,195T 用于 512Gb TLC。与之前的 128L 512Gb TLC 芯片 (7.755 Gb/mm²)相比,通过大幅缩小芯片尺寸,512Gb TLC 芯片的位密度达到 10.273 Gb/mm²。

2-deck 结构 (88L+88L) 已用于垂直 NAND 串集成,仅与 Intel 除外(144L FG CuA 的 3-deck 结构)。对于三星来说,512Gb 176L TLC芯片将是第一代Cell-on-Periphery、COP (CuA)、TCAT V7 V-NAND,接下来的1Tb 238L TLC产品将是第二代COP TCAT V8 V-NAND . 虽然三星 176L TLC 芯片的位密度 (8.5 Gb/mm²) 比 SK hynix 512Gb 176L V7 4D PUC NAND (10.8 Gb/mm²) 和 KIOXIA/WD 1Tb 162L CuA BiCS6 NAND (10.4 Gb/mm²),预计三星 238L TLC 裸片将增加到 11.5 Gb/mm²。

即使是 238L,三星也将保留 2 层结构,这是三星在 3D NAND 技术方面的优势之一。162L BiCS6 3D NAND 将是铠侠/WD 第一款采用 CuA 概念的产品。

表 1. 即将推出的新型 3D TLC NAND 芯片比较;三星 176L 和 238L、SK 海力士 176L、KIOXIA/WD 162L(来源:ISSCC2021、ISSCC2022)

未来如何增加3D NAND的存储容量?

尽管业界已经超越了具有 CuA(或 PUC 或 COP 或 Xtacking)概念的 128 堆叠 WL 结构,但 3D NAND 存储设备现在面临许多挑战,例如减少单元串电流、增加工艺吞吐量、工艺不均匀性、缺陷、寄生负载增加、外围面积减少、WL 通道电容增加、RC 延迟变化、WL 上升时间和单元间干扰增加,以及读/写速度降低。

此外,3D NAND 产品也需要高带宽。为了应对和克服上述挑战,NAND 厂商已成功开发并应用了新的创新和技术,用于即将推出的 176L/238L NAND 存储设备,例如:

三星 176L TLC V7 V-NAND

-

三星第一代COP 结构

-

2步BL 强制 (TBF)、2步BL/WL 强制 (TBWF) 以最小化电池 Vt 变化

-

MIM 垂直电容(电荷泵,CP)最大限度地提高电源效率并减少 CP 面积

-

通过 LTT 或 CTT 接口切换DDR5.0

三星 238L TLC V8 V-NAND

-

三星第 2代COP 结构

-

2层集成

-

偏移消除感应锁存器 (OCSL) 方案以改善 V行程偏移

-

四组无干扰读取 (Q-IFR) 方案以减少单元耦合(V t shift @Read)

-

用于降低 CSL 噪声的 CSL 噪声跟踪(CSL 补偿)方案

-

代码自适应直流保持以减少 tCS(建立时间)和功耗

-

切换 DDR5.0 接口

SK 海力士 176L TLC V7 4D PUC

-

SK hynix的第 3代 4D PUC NAND 结构

-

12 级页面缓冲区 (PB)

-

1:1 PB 到缓存连接总线 (PBUS)

-

具有半平面激活的居中 X 解码器 (XDEC)

-

新的字符串提升(未选择的字符串提升方案)

-

自适应 WL 过载 (OVD)

-

用于可变级和频率电荷泵的本地泵升压

铠侠/WD 162L TLC BiCS6

-

铠侠/WD第一代 CuA BiCS 和第六代BiCS

-

异步独立平面读取 (AIPR) 技术

-

新的增强传感(SEN Isolation)方案

-

IO 占空比校正 (IO-DCC) 方案

-

用于逻辑电路的新扫描链(测试)

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3101内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻