铠侠,目光瞄向每单元7位3D NAND

来源:内容由 半 导体行业观察(ID:icbank) 编译自tomshardware ,谢谢

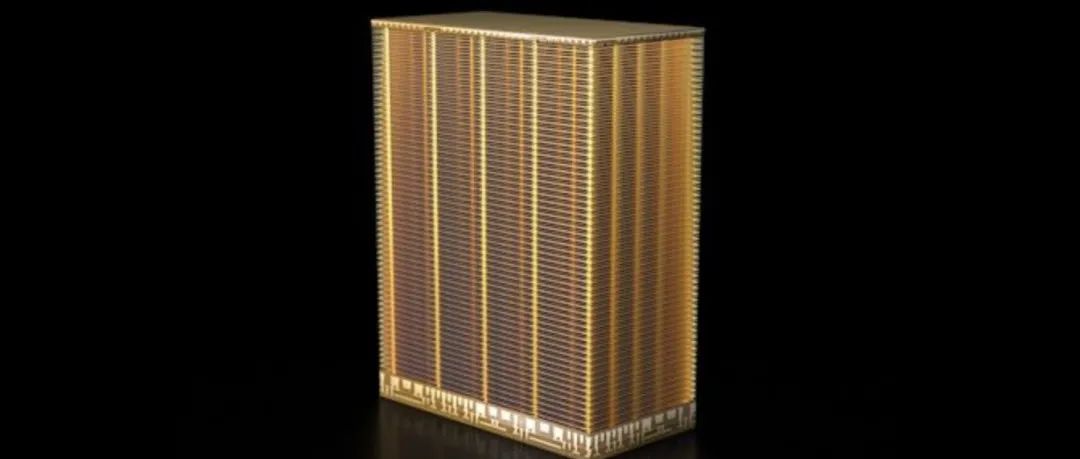

NAND 闪存制造商一直试图通过增加每个单元存储的位数来提高其存储设备的存储密度。虽然从根本上说,这是提高记录密度的最具挑战性的方法,但从成本的角度来看,它也是最有价值的方法。像 Kioxia 这样的公司一直在试验他们可以在一个单元中存储的比特数。今年,该公司表示,它已设法在每个单元中存储 7 位 (7 bpc),尽管这目前是在实验室和低温下实现。

为了存储多于一位,NAND 单元必须保持多个不同的电压电平,这具有挑战性,因为 NAND 制造商必须为这些单元找到合适的材料,然后无错误地记录和读取它们。此外,电压状态的数量随着位数的增加呈指数增长。例如,要存储 4 位,单元必须保持 16 个电压电平 (2^4),但使用 6 位,该数字会增长到 64 (2^6)。Kioxia 实现每个单元存储 7 位需要保持 128 个电压状态 (2^7)。铠侠在 2022 年国际记忆研讨会 (IMW 2022) 上展示了描述其成就的论文。

Kioxia 必须使用通过外延生长构建的单晶硅通道来存储每个单元的 7 位。单晶硅的电阻比多晶硅低,因此更容易记录此类电池。此外, PC Watch报告称,具有单晶硅的单元晶体管的亚阈值斜率更陡(与传统晶体管相比),而泄漏电流和读取噪声更低 。

这种 NAND 闪存单元现在无法在商业上实现,因此 Kioxia 的科学家们不得不在实验室中制造它们。此外,为了记录和读取它们,他们将芯片浸入液氮(液氮(77°K,-196°C)中)以稳定材料,降低电压要求,减少对隧道绝缘膜的需求,并避免由重写周期引起的单元折旧。

在实验室中构建定制晶体管只是超高密度 NAND 闪存挑战的一半。首先,研究人员必须开发和使用具有适合处理 128 种电压状态的自定义编码方案的自定义控制器。

自 2000 年代初多级单元 (MLC, 2 bpc) NAND 首次亮相以来,NAND 闪存控制器变得越来越复杂。因此,控制器的复杂性是 NAND 生产商和控制器开发人员都熟悉的东西。但能够准确处理 128 个电压电平的控制器可能与微处理器一样复杂且价格昂贵。因此,主要问题是使用昂贵且复杂的 SSD 控制器将 3D NAND 记录密度仅增加 40%(从 5 bpc 到 7 bpc)是否有意义。虽然 最好的 SSD 往往成本很高,但过于先进的控制器可能会使超高容量驱动程序变得过于昂贵,并消除它们的所有优势。

西部数据认为, 即使在 2025 年之后,即使是 PLC 3D NAND(5 bpc)也几乎没有意义。但是 Kioxia 现在展示了每个单元存储 7 位的物理可能性,甚至谈到最终保持每个单元 8 位。

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3073内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 MediaTek 发布天玑 8400 移动芯片,开启高阶智能手机全大核计算时代

- 2 探索智慧实践,洞见AI未来!星宸科技2024开发者大会暨产品发布会成功举办

- 3 国产EDA突破,关键一步

- 4 共筑国产汽车芯片未来,中国汽车芯片联盟全体大会即将开启