质疑Jeff Dean把AI用于芯片设计?谷歌解雇员工!

来源:本文由半导体行业观察编译自纽约时报。

在谷歌解雇了两名批评人工智能系统中存在偏见的研究人员后不到两年,该公司最近又解雇了一名研究人员,该研究人员质疑其发表的一篇论文,该论文涉及用于制造计算机芯片的一种特殊类型人工智能的能力。

研究人员 Satrajit Chatterjee 带领一组科学家对去年发表在科学杂志《自然》上的著名研究论文提出质疑,并表示计算机能够比人类更快、更好地设计计算机芯片的某些部分。

43 岁的 Chatterjee 博士于 3 月被解雇,此前不久,谷歌告诉Chatterjee 博士的团队,他们不会发表一篇论文来反驳《自然》杂志上的一些说法。四名知情人士说,他们被禁止在《自然》杂志上公开发言。谷歌在一份书面声明中证实,Chatterjee 博士已“因故被解雇”。

谷歌拒绝详细说明Chatterjee 博士被解雇的情况,但为他批评的研究以及不愿发表他的评估提供了全面的辩护。

谷歌研究院副总裁佐宾·加赫拉马尼在一份书面声明中表示:“我们彻底审查了《自然》的原始论文,并支持同行评审的结果。” “我们还严格调查了随后提交的技术声明,它不符合我们的出版标准。”

Chatterjee 博士的解雇是 Google Brain 小组内部和周围不和谐的最新例子,Google Brain 是一个被认为是公司未来关键的人工智能研究小组。在花费数十亿美元聘请顶级研究人员并创建新型计算机自动化之后,谷歌一直在努力应对关于其如何构建、使用和描述这些技术的各种抱怨。

最近的争议也遵循了一种熟悉的模式,即谷歌的人工智能研究人员解雇和争辩不法行为,这对于一家将未来押注于将人工智能融入其所做的一切事情的公司来说,这越来越令人担忧。谷歌母公司 Alphabet 的首席执行官桑达尔·皮查伊将人工智能比作电或火的到来,称其为人类最重要的努力之一。

十多年前,当一组研究人员构建了一个学习识别 YouTube 视频中猫的系统时,Google Brain 开始作为一个辅助项目。谷歌的高管们对机器可以自行学习技能的前景如此着迷,他们迅速扩大了实验室,为用这种新的人工智能重塑公司奠定了基础。该研究小组成为该公司最大抱负的象征。

但即使谷歌在推广这项技术的潜力,它也遇到了员工对其应用的抵制。2018 年,谷歌员工抗议与国防部签订的合同,担心该公司的人工智能最终可能会杀人。谷歌最终退出了该项目。

2020 年 12 月,谷歌解雇了 Ethical AI 团队的一位负责人 Timnit Gebru,因为她批评了该公司招聘少数族裔的方法,并推动发表一份研究论文,指出一种用于学习语言的新型人工智能系统存在缺陷。

在她被解雇之前,Gebru 博士正在寻求允许发表一篇研究论文,内容是关于基于人工智能的语言系统,包括谷歌构建的技术,最终可能如何使用他们从书籍和网站上的文本中学到的有偏见和仇恨的语言。Gebru 博士说,她对谷歌对此类投诉的回应感到愤怒,包括拒绝发表论文。

几个月后,该公司解雇了团队的另一位负责人玛格丽特·米切尔(Margaret Mitchell),后者公开谴责谷歌对格布鲁博士的处理方式。该公司表示,米切尔博士违反了其行为准则。

去年 6 月发表在《自然》杂志上的论文推广了一种称为强化学习的技术,该论文称该技术可以改进计算机芯片的设计。该技术被誉为人工智能的突破,是对现有芯片设计方法的巨大改进。谷歌表示,它使用这种技术开发了自己的人工智能计算芯片。

谷歌多年来一直致力于将机器学习技术应用于芯片设计,并在一年前发表了一篇类似的论文。大约在那个时候,谷歌询问了 Chatterjee 博士,他拥有加州大学伯克利分校的计算机科学博士学位,并曾在英特尔担任研究科学家,看看这种方法是否可以出售或授权给一家芯片设计公司,知情人士说。

但三位知情人士表示,Chatterjee 博士在一封内部电子邮件中对该论文的一些主张表示保留,并质疑该技术是否经过严格测试。

在关于这项研究的辩论仍在继续的同时,谷歌向 Nature 投了另一篇论文。知情人士说,对于提交的文件,谷歌对较早的论文进行了一些调整,并删除了两位作者的姓名,他们曾与 Chatterjee 博士密切合作,并对论文的主要主张表示担忧。

当新论文发表时,一些谷歌研究人员感到惊讶。知情人士说,他们认为它没有遵循该公司负责大部分人工智能工作的高级副总裁 Jeff Dean 在 Gebru 博士被解雇后所说的出版审批程序。

谷歌和该论文的两位主要作者之一安娜·戈尔迪 (Anna Goldie) 与计算机科学家阿扎利亚·米尔霍塞尼 (Azalia Mirhoseini) 共同撰写了这篇论文,他们表示,较早论文的更改不需要经过完整的批准程序。Google 允许 Chatterjee 博士和少数内部和外部研究人员撰写一篇挑战其某些主张的论文。

该团队将反驳论文提交给所谓的决议委员会以供出版批准。几个月后,这篇论文被拒绝了。

撰写反驳论文的研究人员表示,他们希望将这个问题上报给皮查伊先生和 Alphabet 的董事会。他们争辩说,谷歌决定不发表反驳违反了它自己的人工智能原则,包括坚持科学卓越的高标准。知情人士说,不久之后,Chatterjee 博士被告知他不再是一名谷歌员工。

Goldie 女士说,Chatterjee 博士曾要求在 2019 年管理他们的项目,但他们拒绝了。她说,当他后来批评它时,他无法证实他的投诉,并忽略了他们在回应中提供的证据。

“两年多来,Sat Chatterjee 对我和 Azalia 发起了一场虚假信息宣传活动,”Goldie 女士在一份书面声明中说。

她说,这项工作得到了最负盛名的科学出版物之一《自然》的同行评审。她补充说,谷歌已经使用他们的方法制造了新的芯片,这些芯片目前用于谷歌的计算机数据中心。

Chatterjee 博士的律师 Laurie M. Burgess 表示,令人失望的是,“Nature 论文的某些作者正试图通过诽谤和攻击 Chatterjee 博士仅仅寻求科学透明度来阻止科学讨论。” Burgess 女士还质疑 Dean 博士的领导能力,他是 Nature 论文的 20 位合著者之一。

“Jeff Dean压制所有相关实验数据的发布,而不仅仅是支持他所支持的假设的数据,这应该会给科学界和使用谷歌服务和产品的更广泛的社区带来严重的困扰,”Burgess 女士说。

Dean博士没有回应置评请求。

在与谷歌以外的学者和其他专家分享反驳论文后,争议传遍了全球专门从事芯片设计的研究人员社区。

芯片制造商英伟达表示,它使用了与谷歌类似的芯片设计方法,但一些专家不确定谷歌的研究对更大的科技行业意味着什么。

“如果这真的运作良好,那将是一件非常棒的事情,”德国德累斯顿科技大学教授 Jens Lienig 指的是谷歌论文中描述的人工智能技术。“但尚不清楚它是否有效。”

(点击“ 阅读原文 ”,可查看原文。 )

前情回顾

如何将AI应用于芯片设计?谷歌有话说!

如果这还不够糟糕的话,摩尔定律在晶体管密度和成本方面的改进正在放缓。与此同时,芯片设计成本和用于蚀刻芯片的工厂成本也在上升。为保持IT创新的飞跃,在这些方面的任何节省都将是最受欢迎的。

目前,在芯片设计领域,一个很有前途的研究前沿是利用机器学习技术来实际帮助完成设计过程中的一些任务。我们将在即将于3月10日在圣何塞举行的下一届人工智能平台活动上与Cadence Design Systems的工程总监Elias Fallon讨论这个问题。在芯片设计中使用机器学习也是谷歌研究小组的高级研究员Jeff Dean的主题之一,他帮助超大规模业者(hyperscaler)发明了许多关键技术,在本周于旧金山举行的2020年国际固态电路会议上的主题演讲中他谈到了这一点。

事实证明,谷歌对计算引擎不仅仅有一时的兴趣,它是世界上CPU和GPU的主要消费者之一,并且还是从边缘到数据中心的TPU的设计者,他们既可以进行机器学习推理又可以进行数据学习和训练。这不仅是搜索引擎巨头和公共云竞争者的学术活动,尤其是如果它打算继续推进其TPU路线图,并且决定像竞争对手亚马逊网络服务一样,开始设计自己的定制Arm服务器芯片,或者决定为其手机和其他消费设备定制Arm芯片。

出于某种偶然性,谷歌在大量不同类型的计算引擎上运行机器学习模型时所做的一些工作正在反馈到它在ASIC上自动放置和布线IP块的工作中。(当一个想法是这样的成形时,那是很美妙的……)

虽然Google在2018年5月展示的TPUv3系统的Pod可以将1,024个张量处理器(其内核数量是我们所知的两倍,时钟速度提高了约15%)组合在一起,使用谷歌自己的非常聪明的bfloat16数据格式来提供106千万亿次浮点运算,16位半精度乘法性能(32位累积)的总和。这些TPUv3芯片都使用32×32环形网格交叉耦合,因此它们可以共享数据,并且每个TPUv3内核都有自己的HBM2存储库。这个TPUv3 Pod是巨大的计算聚合,可以进行机器学习训练或推理,但是不一定像Google所需要的那么大。 (我们将在单独的故事中讨论Dean对AI硬件和模型未来的评论。)

可以说,谷歌正在使用混合架构,它们混合使用CPU和GPU(也许还有其他一些加速器)来增强学习工作负载,因此Dean和他的同行们参与的研究也将用于ASIC设计。

Dean解释说:“其中一个趋势是模型变得越来越大。”因此,整个模型并不一定适用于单个芯片。如果你有很大的模型,那么模型并行性(将模型划分为多个芯片)是很重要的,并且通过为它提供大量计算设备来获得良好性能并非易事,而且如何有效地做到这一点也并不明显。”

这并不像采用消息传递接口(MPI)那么简单,MPI用于在大规模并行超级计算机上分派工作,并将其破解到一个类似TensorFlow的机器学习框架中,因为AI iron的本质是异构的。但这可能是一种将机器学习培训工作负载分散到大量计算元素上的有趣方式,有些已经这样做了。当然,与其他超大规模业者一样,谷歌倾向于根据其他技术构建自己的框架、协议和数据存储。

设备放置—意味着在整个应用程序中,在正确的时间将正确的神经网络(或包含它的部分代码)放置在正确的设备上,以获得最大的吞吐量—当神经网络模型变得比单个CPU、GPU或TPU的内存空间和计算能力更大时,这一点尤为重要。而且问题比框架和硬件能够跟上的速度还要快。看一看:

参数的数量一直在增加,同时使用的设备的数量也在增加。实际上,使128个GPU或128个TPUv3处理器(这就是您在上表中获得512个内核的方式)协同工作是一项相当大的成就,并且与超级计算机在20多年前所能做到的最好水平相当,在那之前,使用MPI的松散耦合、大规模并行的超级计算机接管了使用实际共享内存的联邦NUMA服务器是HPC的规范。随着越来越多的设备将以某种方式捆绑在一起来处理这些模型,谷歌一直在试验使用强化学习(RL),这是机器学习的一个特殊子集,以找出在任何给定时间在哪里最好地运行神经网络模型,因为模型集成是在CPU和GPU的集合上运行的。在这种情况下,我们设定了一个初始策略来调度神经网络模型进行处理,然后将结果反馈到模型中进行进一步的调整,使其更高效地运行这些模型。

在2017年,谷歌训练了一个RL模型来完成这项工作,这是编码器和解码器的最终放置结果,而在测试系统中,将工作放在两个CPU和四个GPU上的RL模型,与人工放置的人工神经网络相比,训练运行时间减少了19.3%。Dean补充说,这种基于RL的神经网络在计算引擎上的工作“做了一些非直觉的事情”来达到这个结果,这似乎是很多机器学习应用程序的情况,尽管如此,它们在做同样的任务时工作得和人类一样好或更好。问题是,不需要大量的RL计算力就可以在设备上运行正在训练中的神经网络。在2018年,谷歌做了一项研究,展示了如何将计算图扩展到超过80000个操作(节点),去年,谷歌为超过50000个操作(节点)的数据流图创建了一种通用的设备放置方案。

Dean说:“然后我们开始考虑用它来代替把软件计算放在不同的计算设备上,开始考虑我们是否可以用它来做ASIC芯片设计中的放置和布线,因为如果你瞥一眼它们,会发现问题看起来有点相似。”“强化学习对于那些有明确规则的难题,比如国际象棋或围棋,真的很有效。本质上,我们开始问自己:我们能否获得强化学习模型来成功发挥ASIC芯片布局的作用?”

根据Dean的说法,要做到这一点有几个挑战。首先,国际象棋和围棋都有一个目标,那就是赢得比赛而不是输掉比赛。(它们是同一枚硬币的两面。)通过在ASIC上放置IP块并在它们之间进行布线,并不存在简单的输赢,而是有许多您关心的目标,比如面积、时间、拥塞、设计规则等等。更令人气馁的是,IP块放置的神经网络模型必须管理的潜在状态的数量是巨大的,如下图所示:

最后,驱动IP块放置的真正奖励函数(在EDA工具中运行)需要花费很多时间才能运行。

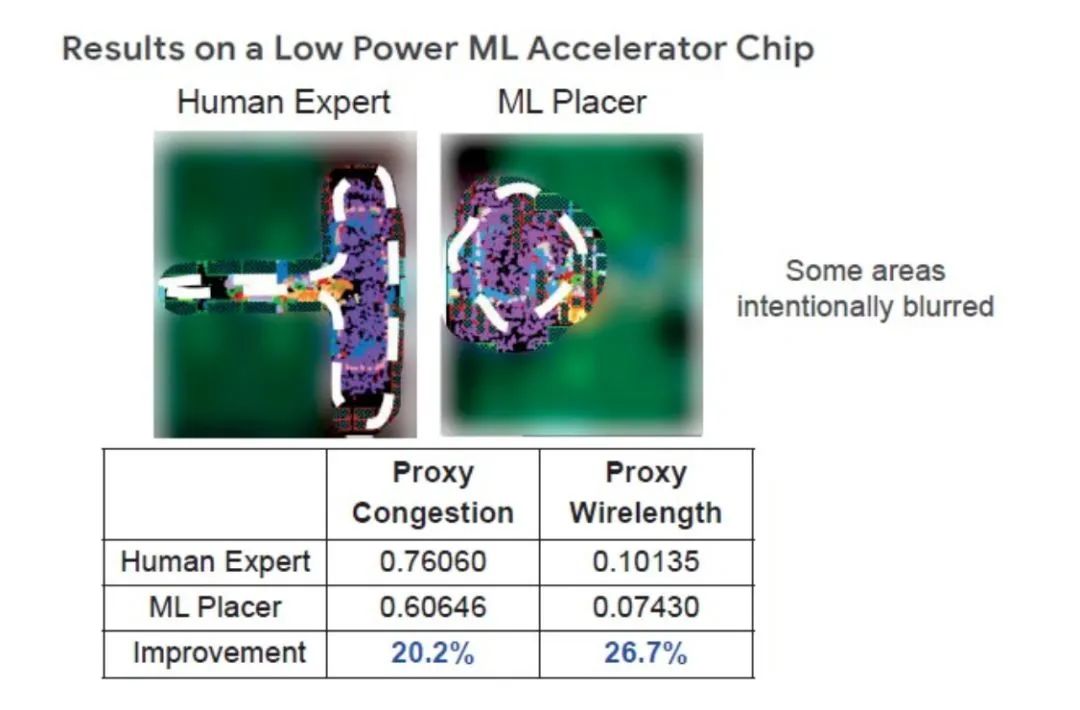

Dean解释说:“所以我们有了一个架构,我不会得到很多细节,但本质上它试图把一堆东西组成一个芯片设计,然后试着把它们放在晶圆上。”他展示了在一个低功率的机器学习加速器芯片上放置IP块的一些结果(我们认为这是谷歌为其智能手机创建的边缘TPU),一些区域故意模糊,以阻止我们学习该芯片的细节。“我们有一个人类专家团队放置了这个IP块,他们有两个代理奖励函数,对我们来说非常便宜;我们用两秒钟而不是几个小时来评估它们,这非常重要,因为强化学习是一种需要多次迭代的过程。我们有一个基于机器学习的布局系统,你可以看到它在某种程度上扩展了逻辑,而不是在这样一个矩形的区域,这使得它在拥塞和电线长度上都得到了改进。到目前为止,我们已经在所有不同的IP区块上取得了类似或超人的结果。”

无论如何,下面是RL网络的低功耗机器学习加速器与IP块放置人员的对比:

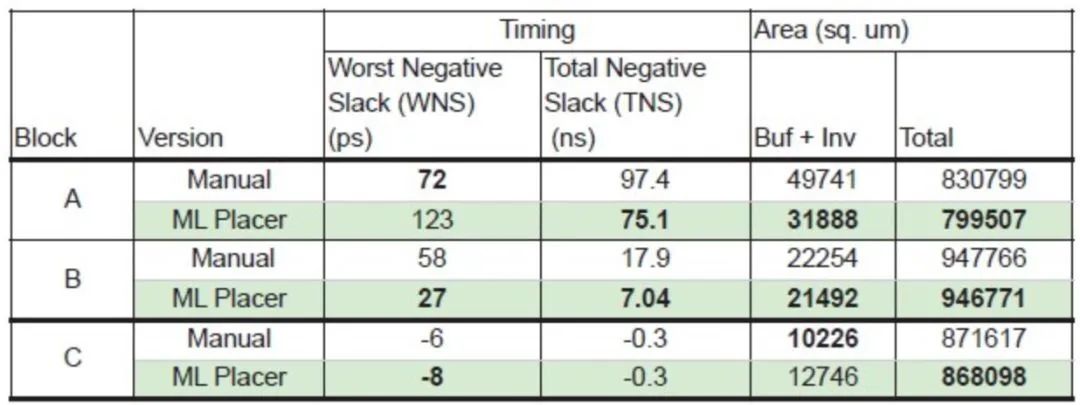

这张表显示了手工放置与布线和机器学习自动化之间的区别:

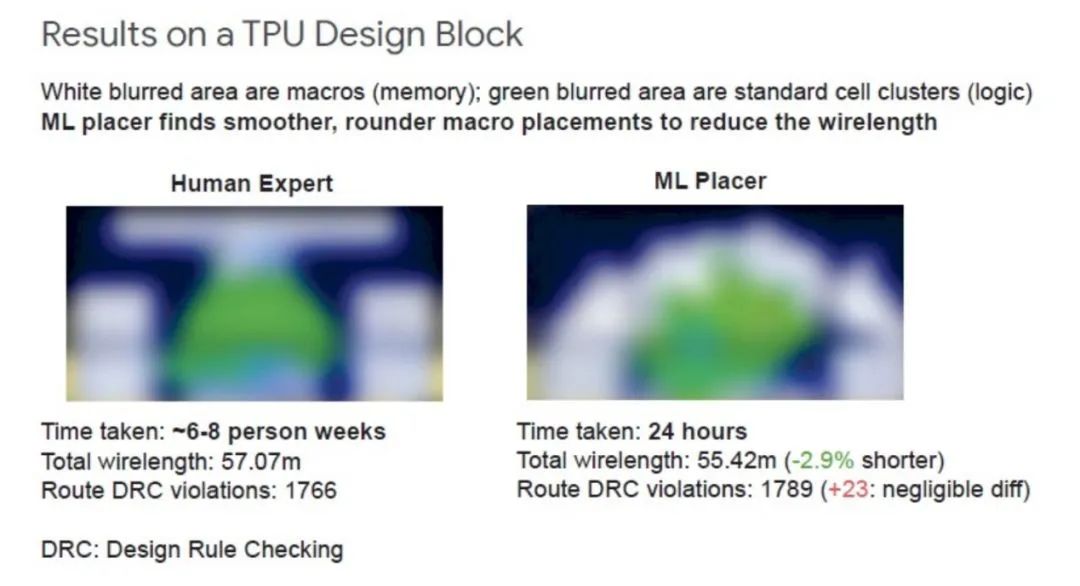

最后,下面是与人类相比,RL网络是如何处理TPU芯片上的IP块的:

与人工智能设计的Cartesian IP块相比,人工智能创建的IP块看起来是多么的有机。令人着迷。

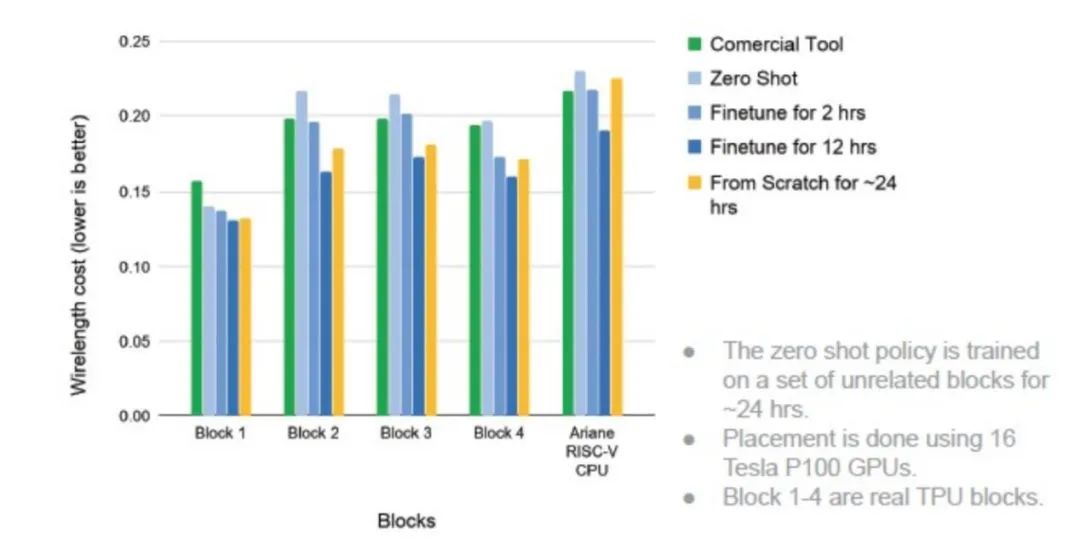

完成了这一步后,谷歌接着问了这样一个问题:我们能否培训一名总代理,能够迅速有效地放置一种从未见过的新设计?这正是你制造新芯片的关键。Google测试了这个通用模型,它使用了四个不同的IP块,分别来自于TPU架构和“Ariane”RISC-V处理器架构。该数据使人们能够使用商业工具并在模型上进行各种级别的调整:

这是关于Ariane RISC-V芯片的放置和布线的更多数据:

Dean说:“你可以看到,其他设计的经验实际上会显著改善结果,所以基本上在12个小时内,你就可以得到最深蓝色的条。”他指的是上面的第一个图表,然后继续上面的第二个图表。”,这张图显示了有线成本,如果你从零开始训练,实际上需要一段时间,系统才会有一些突破性的见解,并能够大幅降低布线成本,而预先训练的政策有一些关于芯片设计的直觉,从看到其他设计和人员很快达到那个水平。”

就像我们做模拟集成来做更好的天气预报一样,Dean说这种人工智能驱动的IP块集成芯片设计的放置和布线可以用来快速生成许多不同的布局,并进行不同的权衡。如果需要添加一些功能,AI芯片设计游戏可以快速重新设计布局,而不需要几个月的时间。

最重要的是,这种自动化设计辅助可以从根本上降低制造新芯片的成本。这些成本呈指数级上升,我们看到的数据(多亏IT行业的杰出人士和Arista Networks董事长兼首席技术官Andy Bechtolsheim),使用16纳米工艺的先进芯片设计平均成本为1.063亿美元,到10纳米为1.744亿美元,再到7纳米成本为2.978亿美元,预计5纳米芯片的订单为5.422亿美元。其中近一半的成本已经并且将继续用于软件。因此,我们知道如何确定这些成本的目标,而机器学习可以提供帮助。

问题是,芯片设计软件制造商是否会将人工智能嵌入芯片设计中,并在芯片设计中引发一场真正意义上的“寒武纪”大爆炸,然后像我们其他人在工作中必须做的那样将其数量化?看看这里会发生什么,以及谷歌所做的类似研究将如何有所帮助,将是一件有趣的事情。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3030内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根