来源:内容由半导体行业观察(ID:icbank)

编译自spectrum

,谢谢。

“蓝色巨人”的z16计算机及其核心的的高速缓存设计为平台提供了新的相关性。

IBM最近推出了名为IBM z16的大型计算机新系列,尽管这一事件并不是什么头版新闻,除了一些媒体的庆祝之外。然而,大型机在当今科技领域的重要性不断下降,并不意味着它正在消失。想想IBM对z16的实时人工智能处理欺诈交易的吹捧吧。(IBM还将z16称为“业界首个量子安全系统”。)

这些激进的说法可能会让z16走上重振大型机平台的道路。所有这些能力的核心是硅。事实上,z16的基础是IBM的Telum芯片,它本身就是去年夏天才推出的。这种芯片的架构使IBM今天正在推进的人工智能大型机成为可能。Telum最吸引人的地方在于它新颖的缓存设计方法。

缓存是每个微处理器的关键设计组件,对处理器的整体性能有着巨大的影响。缓存就像存储柜,能够存储数据,或者在处理器的门口提前缓存数据。

这在当今运行速度非常快的处理器(通常是千兆赫)中尤其重要,以至于每当系统需要等待数据时,宝贵的时钟周期就会被浪费掉。

虽然一些科技媒体认为Telum的缓存操作是“魔法”,但它实际上只是一种智能工程。

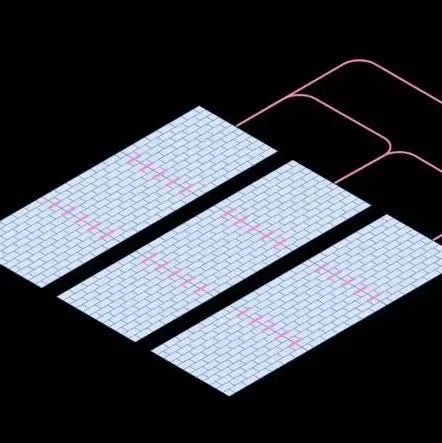

在Telum芯片之前产生的芯片使用了四层缓存:最近的一级缓存是一级(L1),下一级缓存是二级(L2),以此类推,直到你到达四级(L4)。传统上,缓存层次结构是在芯片上使用L1、L2和L3构建的,而L4不在芯片上。每个级别的大小随着您的操作而增加,并且它们离处理器引擎本身越远,延迟也越长。

使用新的Telum芯片,IBM消除了物理L3和L4缓存。他们是如何做到这一点的,这是一项工程壮举,花了五年时间才实现。

IBM 研究员ChristianJacobi说:“我们对 Telum 芯片所做的事情是,我们完全重新设计了这些缓存的工作方式,以使更多的数据比我们过去所做的更接近处理器内核。” IBM zSystems 系统架构和设计首席技术官。“为此,我们将二级缓存增加了四倍。我们现在有一个 32 MB 的二级缓存。”

这个L2缓存的大小与大多数其他服务器芯片的0.5兆字节或1兆字节的缓存形成了鲜明的对比。为了让这个大得多的L2缓存有效地工作,IBM优化了访问模式,以及处理器核心如何获得非常大的32 MB缓存(8个核心256 MB),从而具有极低的延迟。

Jacobi 说:“我们不再受控制逻辑的限制,控制逻辑可以确定数据在缓存中的实际位置,然后将请求发送到缓存的正确区域,然后缓慢地将数据移到那里。”“我们正在设计它,使我们真正只受电力传输延迟的限制,以获取数据,触发读取数组中的数据,然后将数据流回需要的地方。”

“我们试图为每个核心用户提供他们需要的东西,然后他们不需要的东西就变成了可自由支配的空间。”——Christian Jacobi。

就实际数据而言,Telum芯片的最佳延时小于3纳秒,平均延时为3.6纳秒。“我们已经优化了这个访问管道,通过它,我们为我们创造了巨大的性能优势,”Jacobi补充说。

Jacobi和他的团队看到了通过增加L2缓存的大小来消除物理L3和L4缓存的好处,但他们仍然希望获得L3和L4缓存固有的额外存储空间所带来的性能优势。为了保持这些好处,他们决定重塑和重新定义缓存之间的交互方式。

所以他们开始意识到——一个芯片有8个核,每个核都有自己的缓存——并不是每个核都一直一样忙。在每个核心的工作负载需要使用自己的私有缓存时,会发生瞬时转移。

“这次行动对我们来说是一个巨大的机会,” Jacobi解释说。“如果一个核心在其L2上非常繁忙,实际上需要超过32mb的内存,而芯片上的另一个核心使用较少的缓存,我可以使用芯片上的另一个L2作为非常繁忙的缓存的溢出位置。”

这就是为什么Jacobi和他的团队提出了虚拟L3缓存的概念。虚拟L3缓存平衡了未充分利用的L2缓存,将其作为溢出空间用于其他超额使用的L2缓存。当需要访问数据时,仍然可以从非常非常靠近核心的32mb缓存中检索数据。事实上,芯片上的溢出空间因此有效地达到最大值 32 x 8 =256 MB。如果其他核心不做任何事情,理论上它们的所有缓存都可以作为单个核心的溢出来使用——现在它的延迟仍然非常低,只有 12 纳秒。

他说:“我们试图为每个核心提供他们需要的东西,然后他们不需要的东西就会成为核心可以从中受益的自由空间。”“因为我们仍在优化,以获得非常低的延迟,所以实际上这就像一个L3,但它是由物理L2缓存组成的,而不是在芯片上自己的一块硅区域。”

虽然一些科技媒体将这种操作称为“魔法”,但它实际上只是一种智能工程。Jacobi解释说,芯片会定期测量每个缓存的繁忙程度。通过IBM内置到Telum中的启发式算法,它可以确定在最后一微秒内,它在这个缓存上非常活跃,而在另一个缓存上不太活跃。有了这些信息,芯片就会重定向流量,并使用邻近的缓存作为溢出。与此同时,它继续测量它的缓存变换对其他缓存的活跃程度。

Jacobi指出,这种架构还提供了一种干净的方法,允许集成在大型机中的专用硬件加速器(例如能够实时欺诈检测的AI加速器)访问CPU缓存中的数据。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3027内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!