来源:内容由半导体行业观察(ID:icbank)

编译自tomshardware

,谢谢。

台积电最近证实,Apple 使用的是其 InFO_LI 封装方法来构建其 M1 Ultra 处理器并启用其 UltraFusion 芯片到芯片互连。Apple 是最早使用 InFO_LI 技术的公司之一。

当苹果今年早些时候推出其 20 核 M1 Ultra 处理器时,它的

UltraFusion 2.5 TB/s 处理器间互连给观察者留下了深刻印象,这就让我们迫切想知道

它究竟使用了什么样的封装技术。由于苹果使用了台积电的芯片生产服务,因此可以合理地假设它也使用了台积电的一种封装技术。

早在 3 月,就有传言称 Apple 选择使用 TSMC 的 CoWoS-S(带有硅中介层的晶圆上芯片)基于 2.5D 中介层的封装,这几乎是许多公司使用的经过验证的技术. 显然,这是不正确的。根据代工厂在 3D IC 和异构集成国际研讨会上展示的演示文稿,Apple 使用具有本地硅互连 (LSI) 和再分配层 (RDL) 的集成扇出 (InFO)。该幻灯片由 半导体封装工程专业人士

Tom Wassick重新发布。

最终,Apple 的 UltraFusion 芯片到芯片互连使用无源硅桥,将一个 M1 Max 连接到另一个 M1 Max 处理器以构建 M1 Ultra,但有几种方法可以实现这种桥。

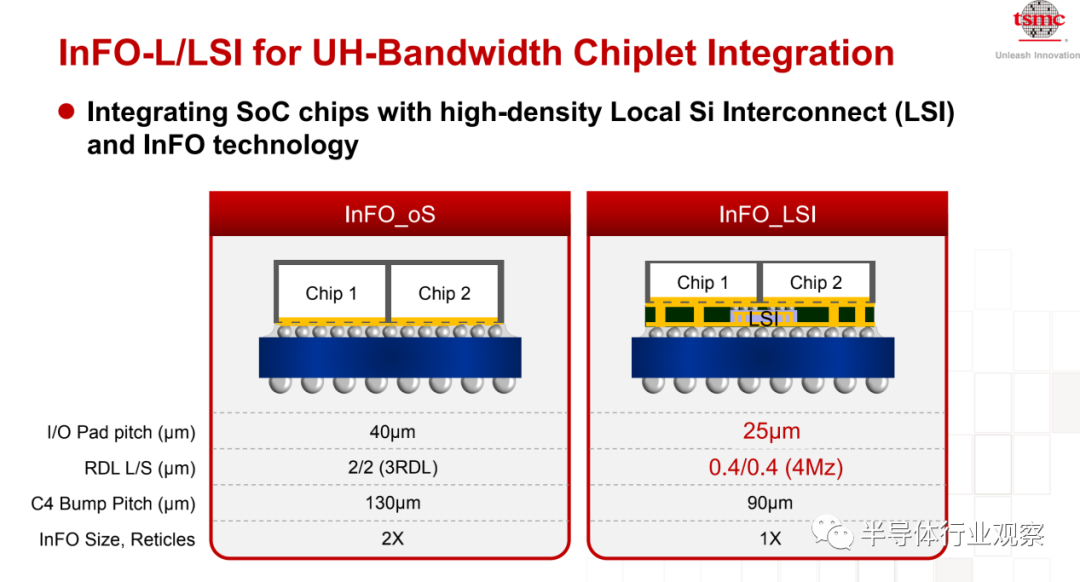

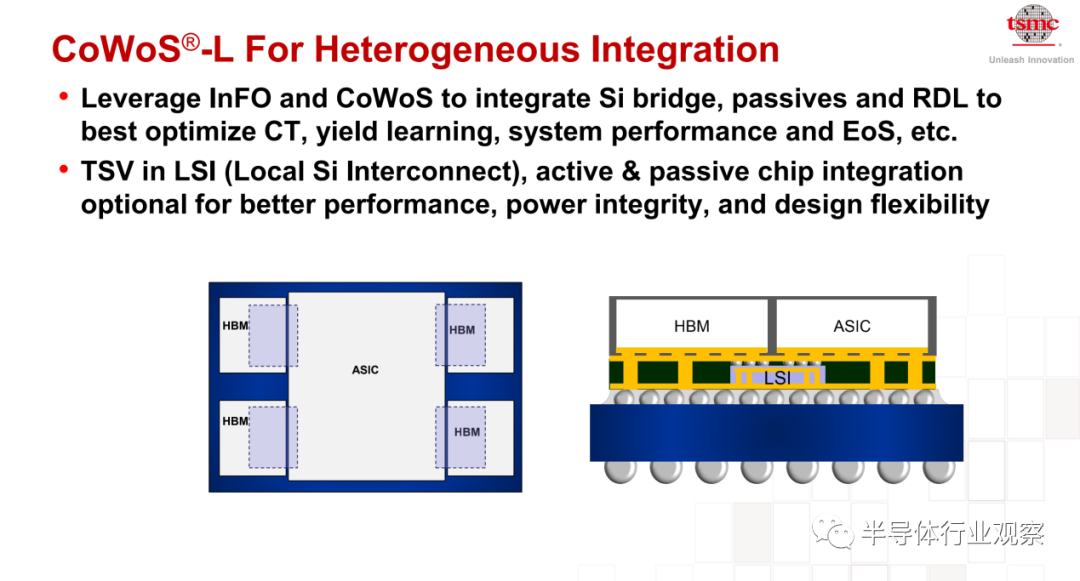

InFO_LI 在多个裸片下方使用局部硅互连,而不是使用大型且昂贵的中介层,这一概念与英特尔的嵌入式裸片互连桥 (EMIB)

非常相似。

相比之下,CoWoS-S 使用昂贵的中介层,因此除非需要非常“广泛”的互连(多芯片 + HBM 存储器集成需要),否则从成本角度来看,InFO 是一种更可取的技术。同时,由于Apple不使用

HBM内存

,也不需要集成两个或更多比interposer更大的die,InFO对于M1 Ultra来说绰绰有余。

我们认为 Apple 可能会使用 CoWoS-S 而不是 InFO_LI 的原因之一是前者已准备好用于商业用途,而后者旨在于 2021 年第一季度完成认证。苹果在第二季度或第二季度开始推出其 M1 Pro 和 M1 Max ,因此我们不确定该公司是否会在其重要设计之一中使用全新的封装技术。

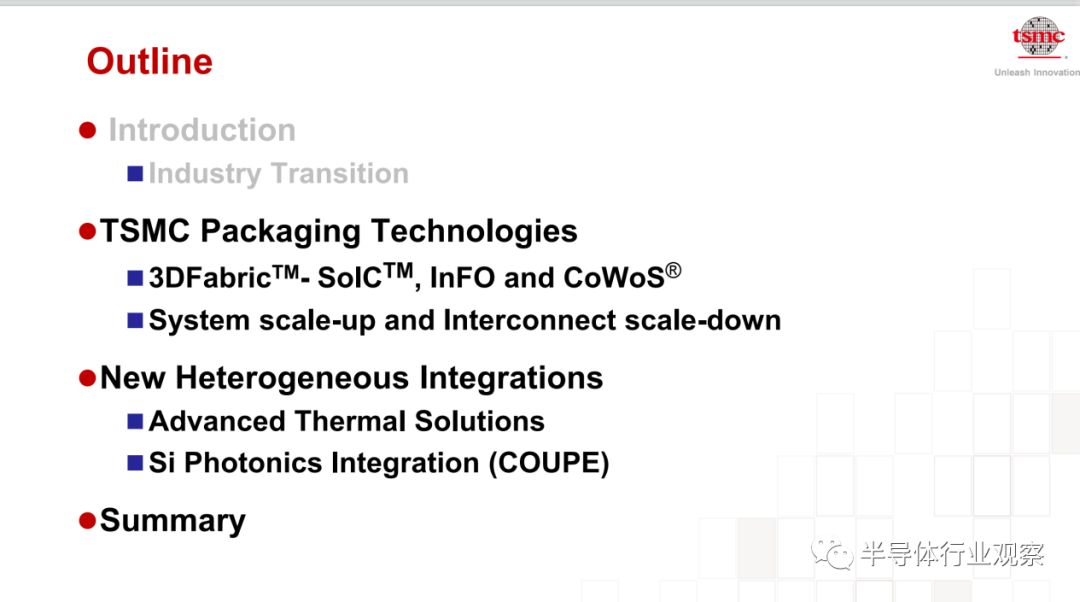

自从与苹果在手机芯片合作上一炮而红之后,关于台积电的封装的讨论就常常见诸于各大媒体。昨日,台积电研发VP余振华参加了一年一度的集成电路产业盛会Hotchips,并在上面讲述了台积电在先进封装方面的路线图,当中尤其聚焦在chiplet和3D封装方面,进行了深入阐释。为此,半导体行业观察将其摘要共享给大家,希望能够给大家带来帮助。

在具体介绍余振华的演讲之前,我们先看一下台积电公司对其的介绍。

余振华博士现任台积公司Pathfinding for System Integration副总经理。余振华博士于1994年加入台积公司,负责后段研发相关的多种业务,并成功地开发0.13微米铜制程的关键制程技术。余博士同时领先推出台积公司的晶圆级系统整合技术,包括CoWoS®、整合型扇出(InFO)封装技术和台积电系统整合芯片(SoIC™)及其相关技术。2016年以前,余振华博士于Integrated Interconnect & Packaging处担任资深处长一职。

加入台积公司之前,余振华博士是美国AT&T贝尔实验室的研究员和项目负责人。1987年至1994年间,余博士致力于次微米制程,组件及整合技术研发工作。

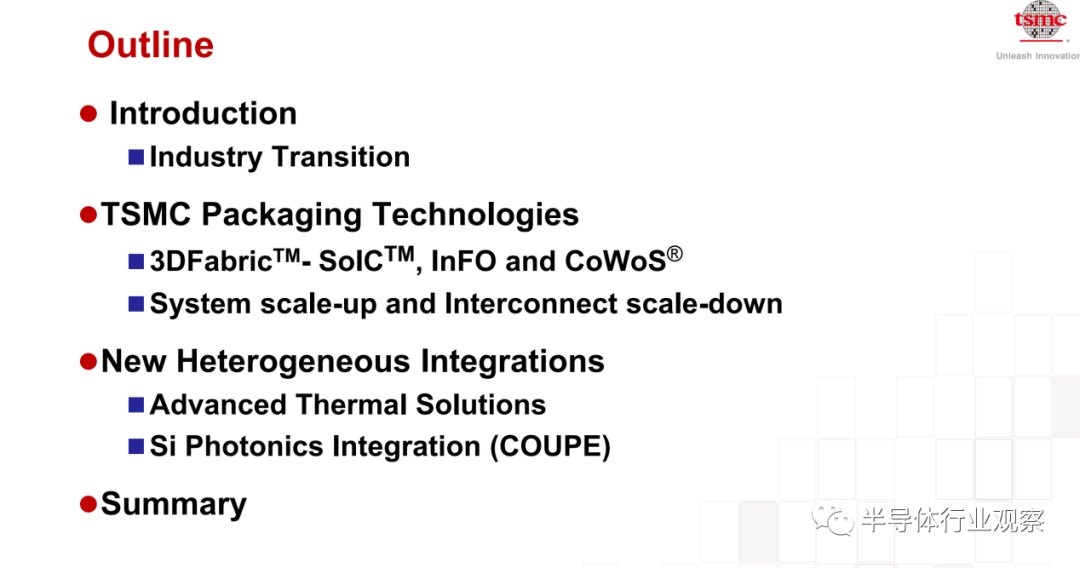

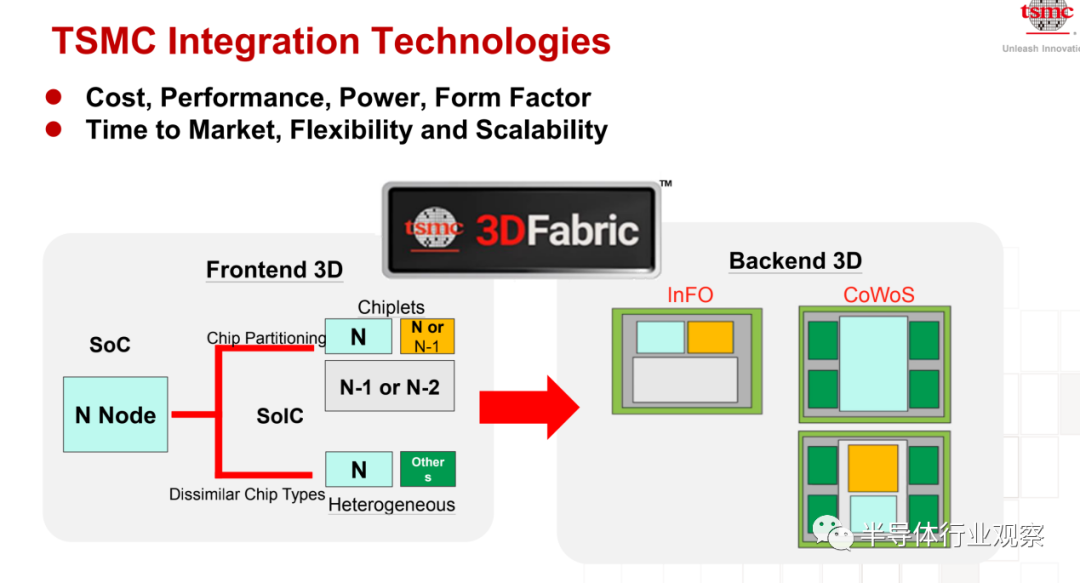

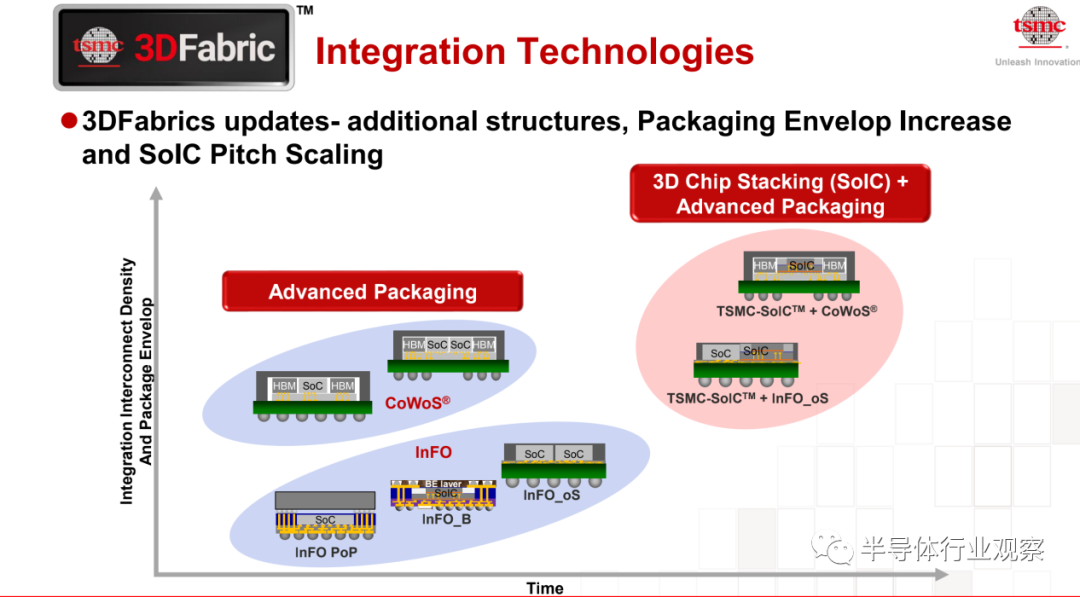

据余博士介绍,公司之所以会在封装上面关注,主要是在综合考量率成本、性能、功耗、上市时间、灵活性和可伸缩性等多个方面。如下图所示,台积电在面向前段和后段,都有其相应对的3D封装结束,而公司将其统一到一个叫作3D Fabirc的平台里。而在其中包括了其2.5D 和 3D 封装产品。

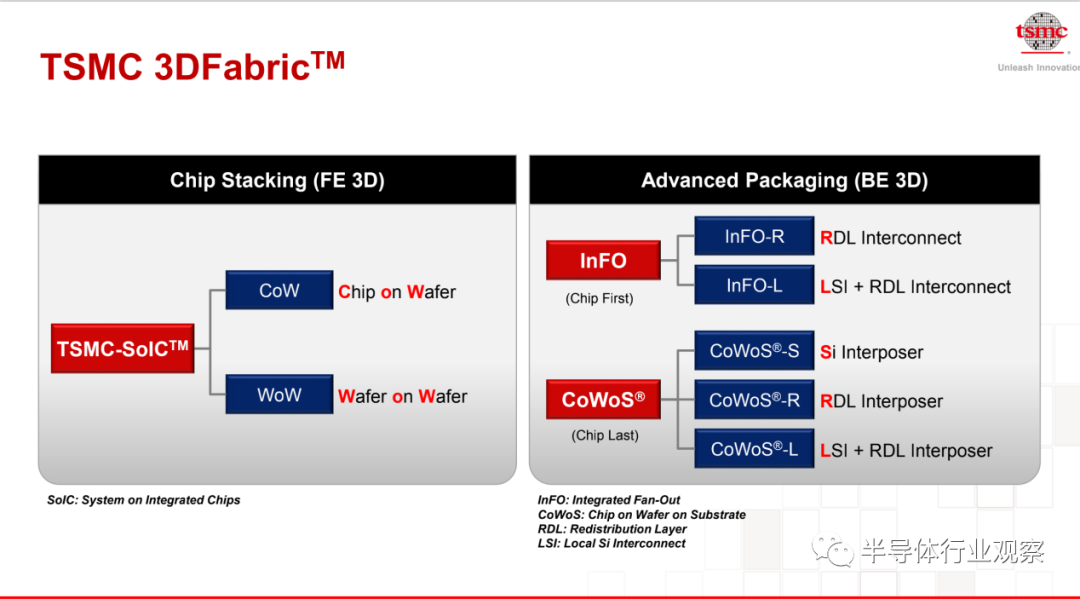

而据半导体行业观察之前的报道,其中,2.5D封装技术CoWoS可分为 CoWoS 和 InFO 系列。首先看CoWoS技术,可以分为以下几种:

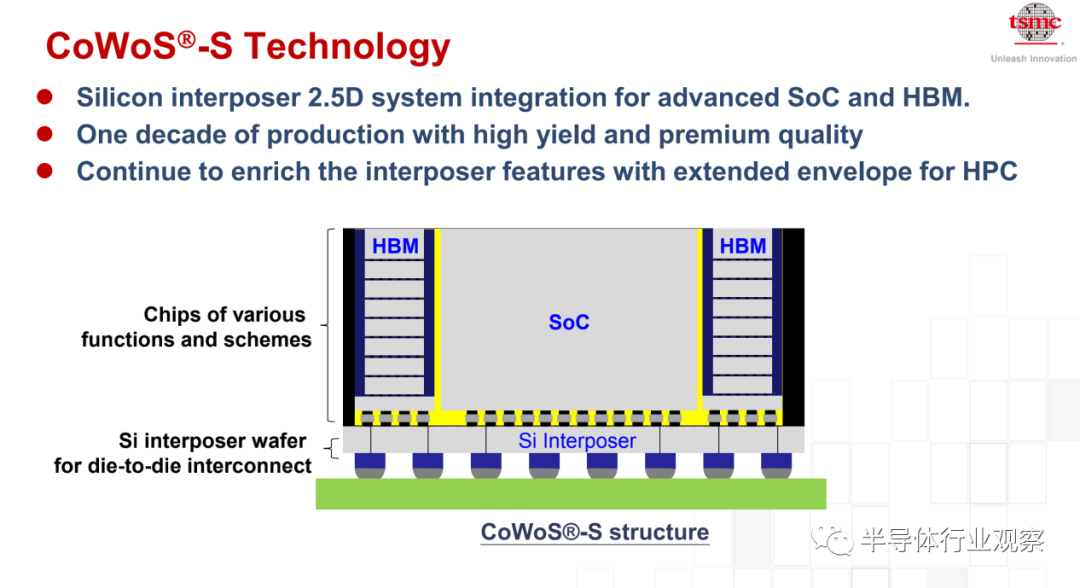

用于die到die再分布层 (redistribution layer:RDL) 连接的带有硅中介层的“传统”基板上晶圆上芯片(chip-on-wafer-on-substrate with silicon interposer )正在庆祝其大批量制造的第 10 年。

CoWoS-R 选项用有机基板中介层取代了跨越 2.5D die放置区域范围的(昂贵的)硅中介层。CoWoS-R 的折衷是 RDL 互连的线间距较小——例如,与 CoWoS-S 的亚微米间距相比,有机上的间距为 4 微米。

在硅 –S 和有机 –R 中介层选项之间,TSMC CoWoS 系列包括一个更新的产品,具有用于相邻die边缘之间(超短距离)互连的“本地”硅桥。这些硅片嵌入有机基板中,提供高密度 USR 连接(具有紧密的 L/S 间距)以及有机基板上(厚)导线和平面的互连和功率分配功能。

请注意,CoWoS 被指定为“chip last”组装流程,芯片连接到制造的中介层。

据介绍,InFO 在载体上使用(单个或多个)裸片,随后将这些裸片嵌入molding compound的重构晶圆中。随后在晶圆上制造 RDL 互连和介电层,这是“chip first”的工艺流程。单die InFO 提供了高凸点数选项,RDL 线从芯片区域向外延伸——即“扇出”拓扑。如下图所示,多die InFO 技术选项包括“InFO-PoP:package-on-package”和“InFO-oS:InFO assembly-on-substrate”。

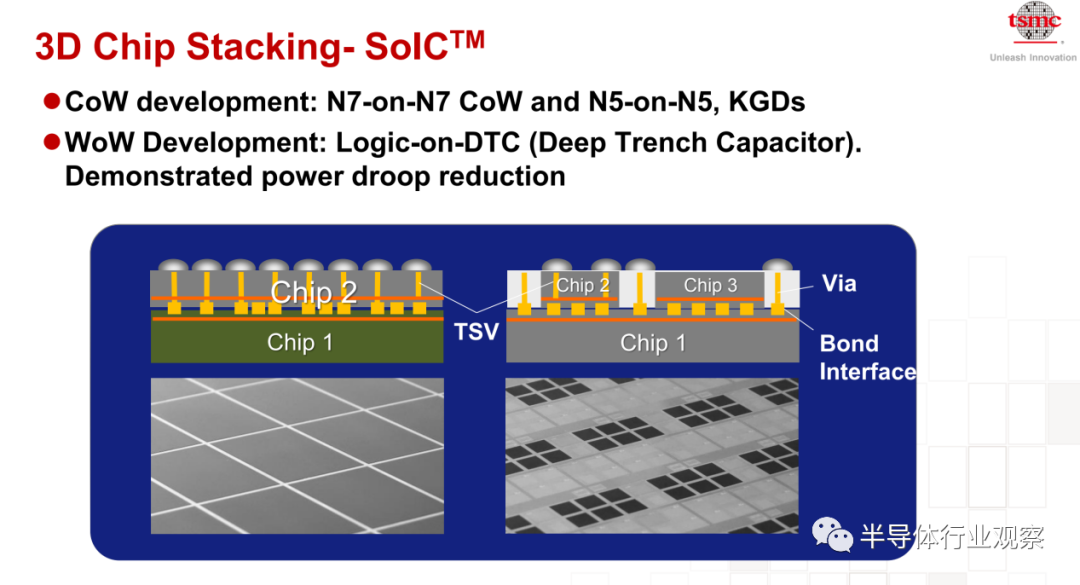

台积电的3D封装技术则是SoIC。据台积电介绍,公司的3D 封装与 SoIC 平台相关联,该平台使用堆叠芯片和直接焊盘键合,面对面或面对背方向 -表示为 SoIC 晶圆上芯片(chip on wafer)。硅通孔 (TSV) 通过 3D 堆栈中的die提供连接。

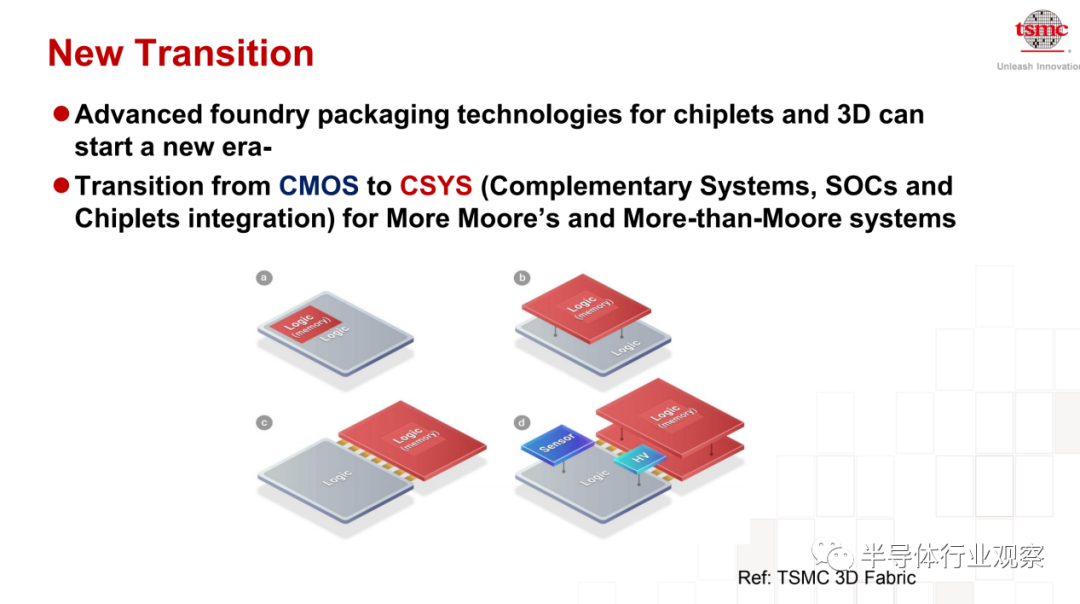

从余振华最新的介绍可以看到,在封装领域,现在正在产生一些新的变化:第一是先进晶圆厂的chiplet和3D封装技术将会开启一个新时代;第二就是为了满足More Moore和More-than-Moore的而需求,行业看到从CMOS向CSYS转变的趋势。

在接下来的介绍中,余振华对TSMC的封装技术进行了更深入的介绍。

如下图所示,他对台积电的3DFabrics进行了更新。

其中,拥有针对移动AP的InFO_B (Bottom Only)技术。

根据半导体行业观察之前的介绍,InFO_PoP 其顶部连接了一个 DRAM 模块,在 DRAM 和 RDL 互连层之间有过孔。TSMC 正在更改此 InFO_PoP 产品,以使 (LPDDR DRAM) 封装组装能够在外部合同制造商/OSAT 上完成,InFO_B 表示一个选项,如下所示。

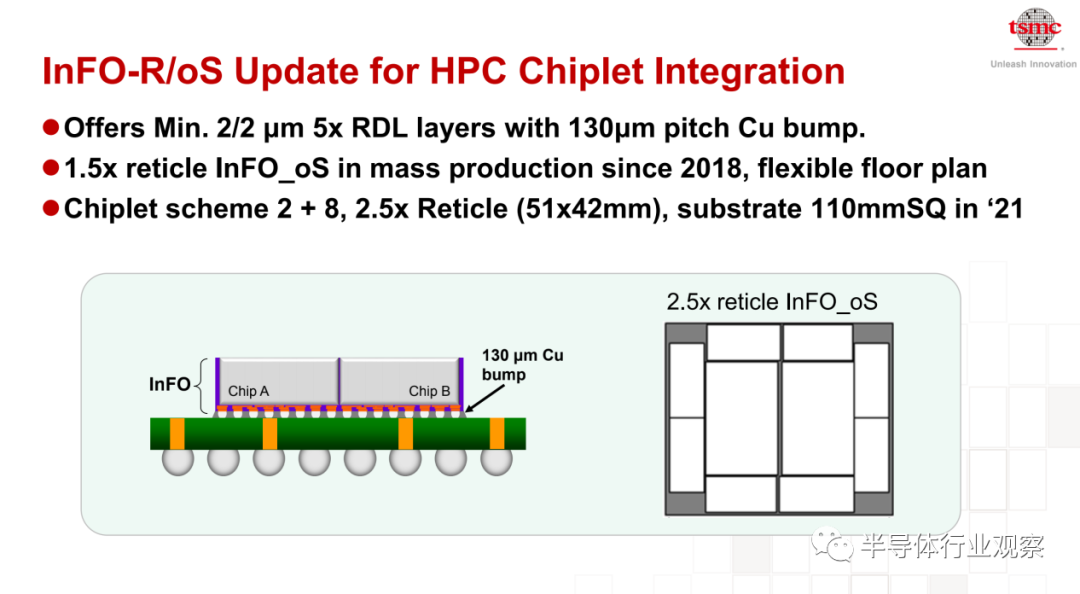

同时,还有针对HPC的chiplet集成技术InFO-R/oS的更新。

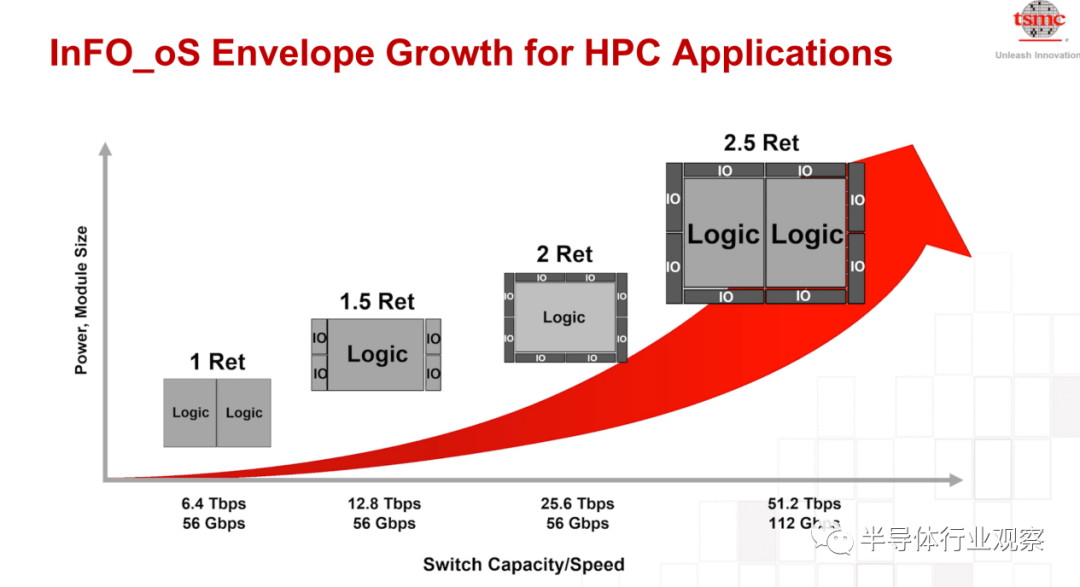

如下图所示,针对不同的需求,台积电能提供拥有不同特性的InFO_oS技术。如图所示,这些逻辑芯片被 SerDes 小芯片这样的 I/O包围,以支持高速/高基数网络交换机。

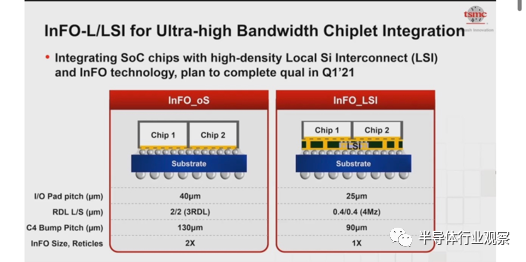

接下来,余振华还介绍了超高带宽的chiplet集成InFO-L/LSI。

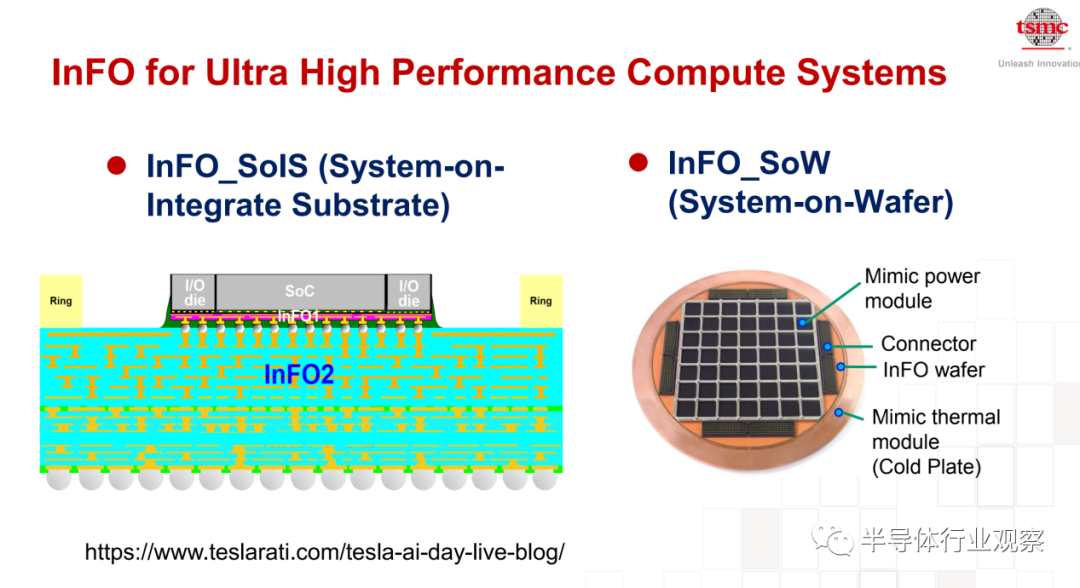

如图所示,面向超高性能的计算系统,台积电也提供了InFO技术支持。值得一提的是,在这个图中,台积电方面还提供了tesla的一个参考链接,可以确定在tesla最新的AI芯片上,采用了台积电的这个封装技术。相信这也将成为未来更多高性能芯片的选择。

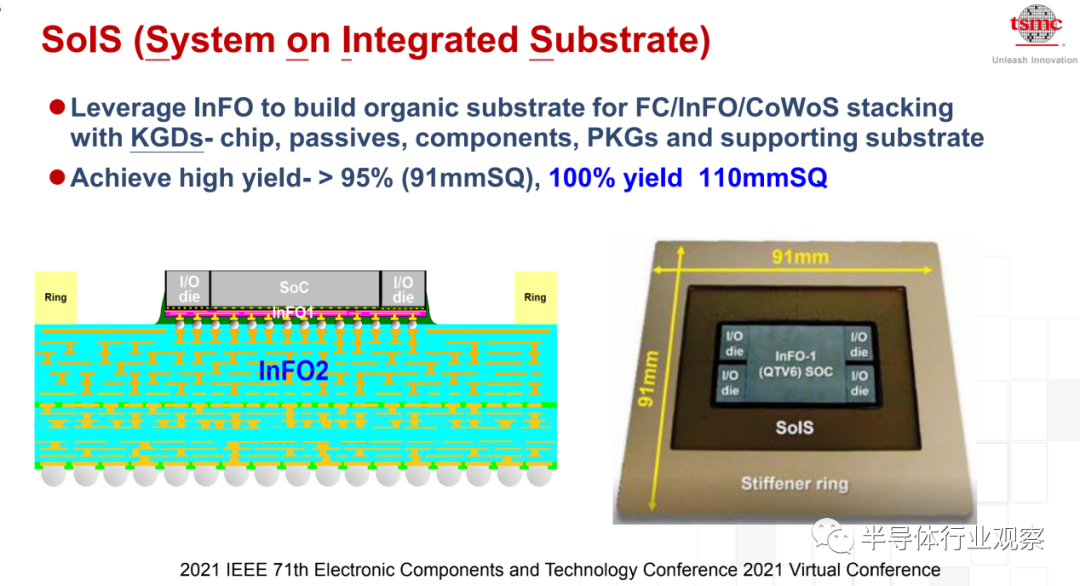

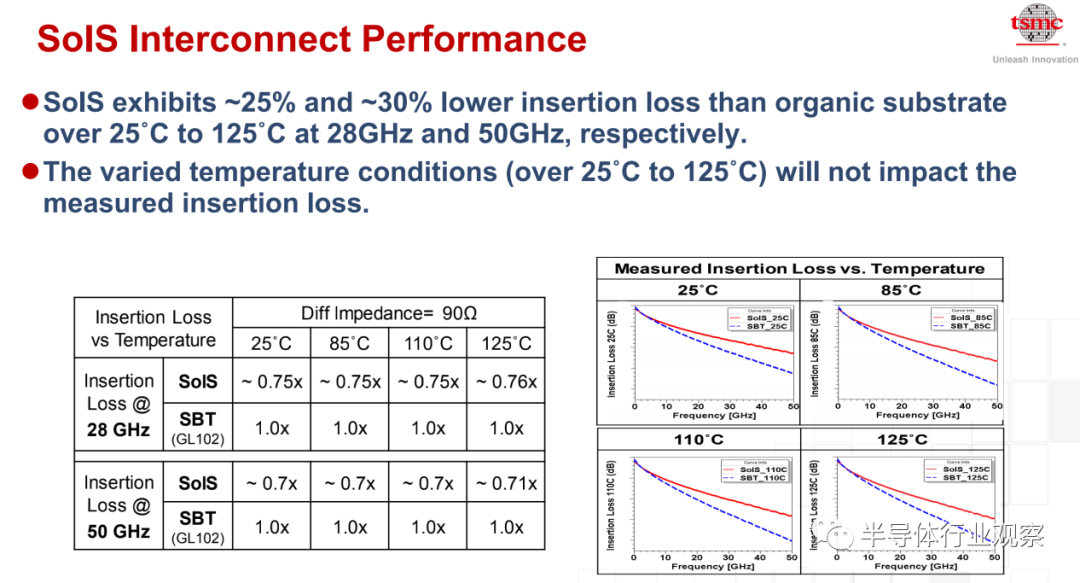

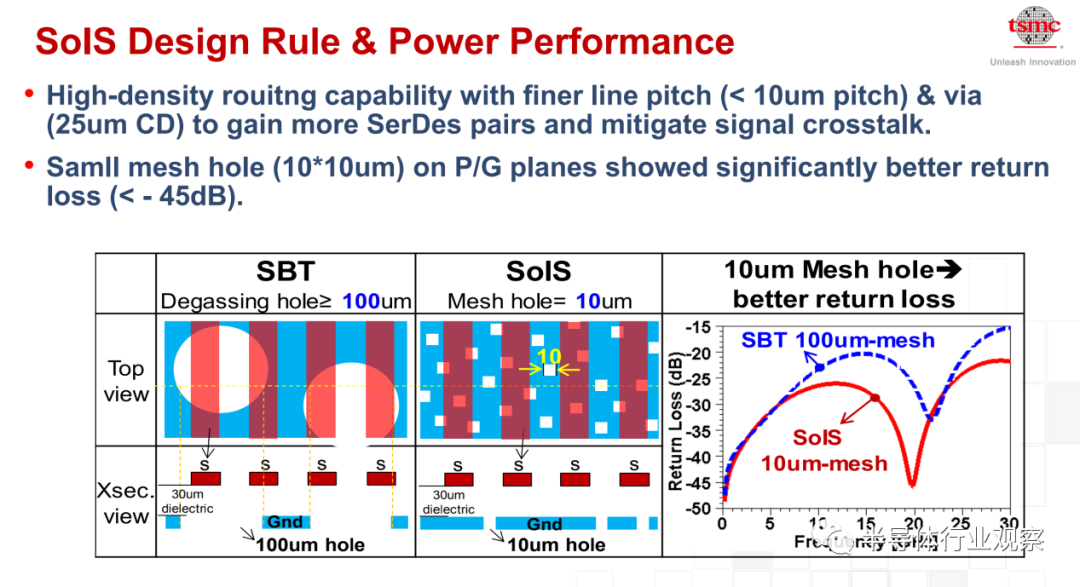

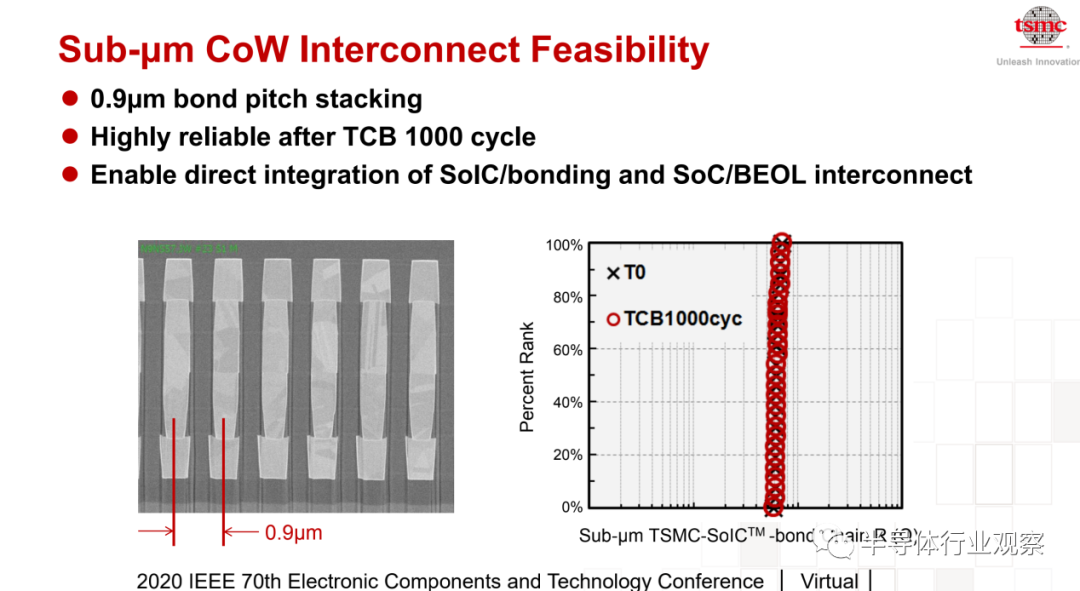

余振华同时还披露了SoIS的设计规则和功耗性能等多方面的信息。

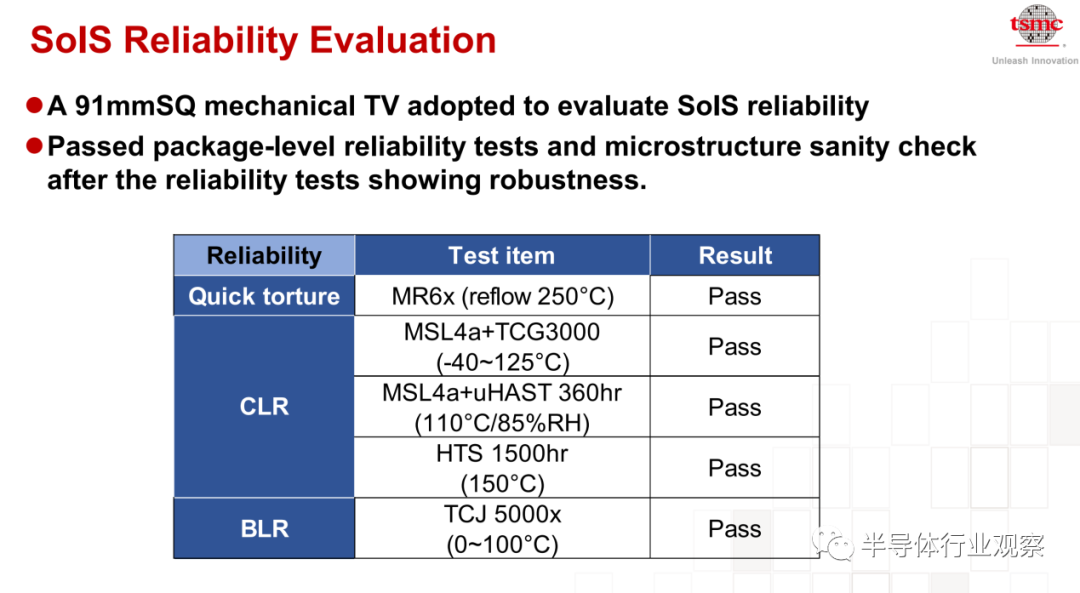

当然,在可靠性方面,SoIS的表现也不会让人失望。

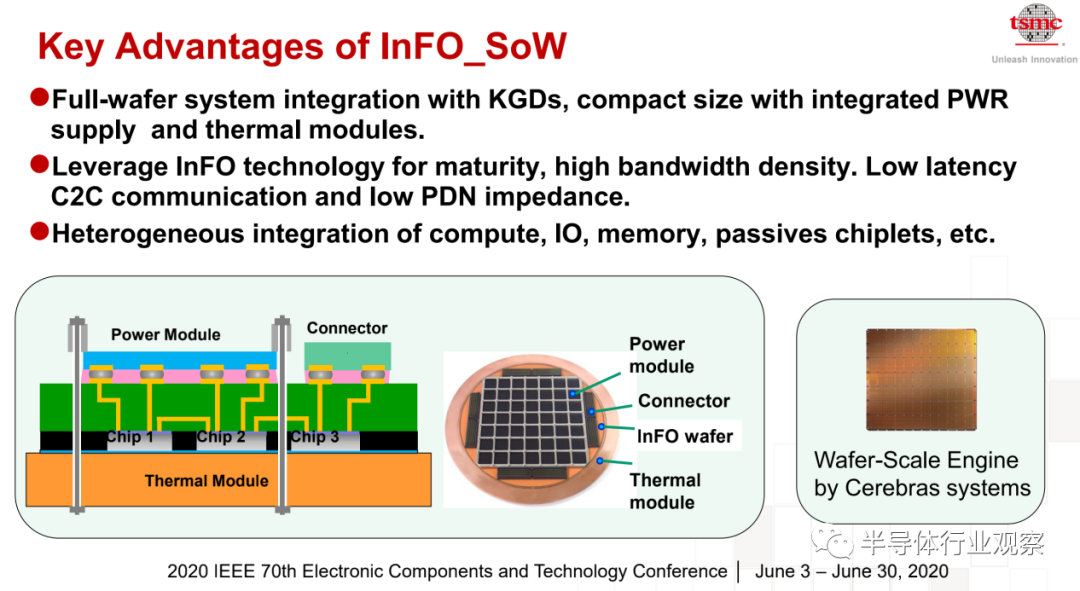

在介绍完SoIS之后,余振华介绍了台积电 InFO_SoW技术的关键优势。具体如下图所示。值得一提的是,Cerebras在其用单晶圆制造的WSE上,使用的正式这个封装技术。

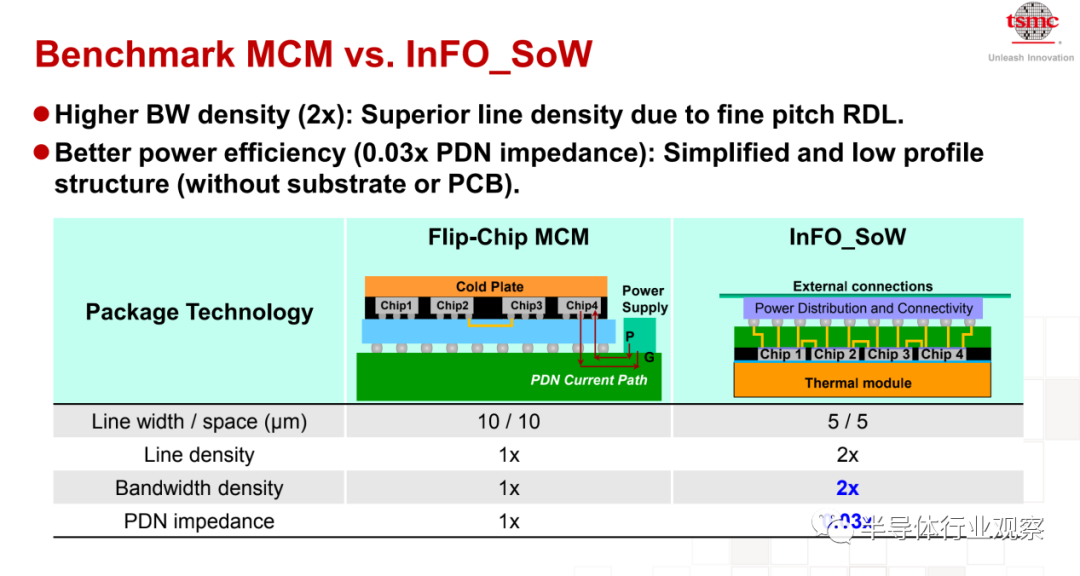

将其与MCM相比,InFO_SoW在线密度、带宽密度方面等多个方面都有明显的优势。

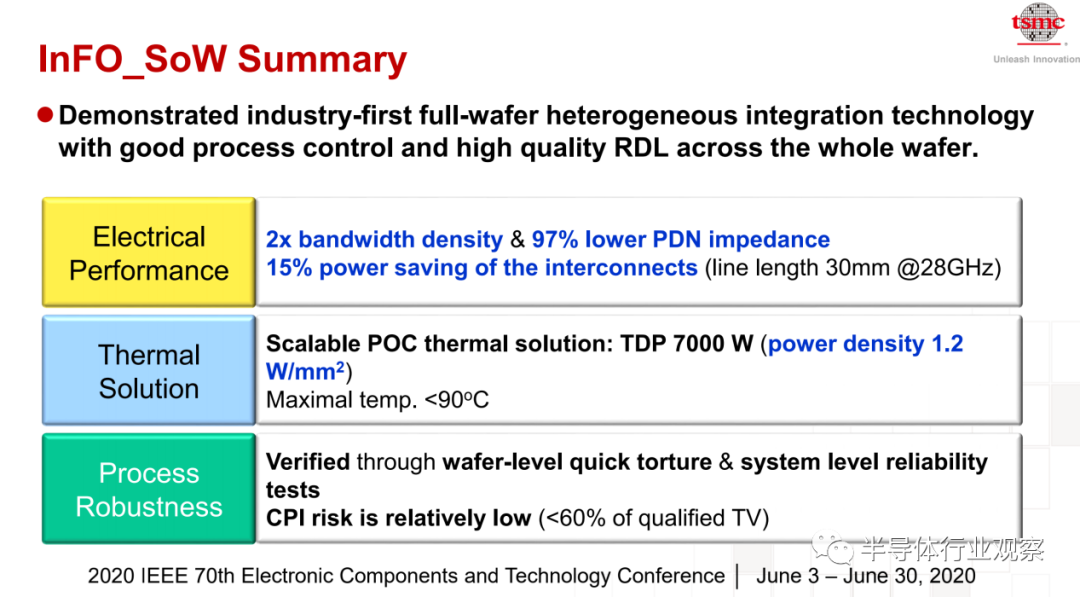

从电气特性上看,如下图所示,InFO_SoW也不遑多让。

从余振华的总结可以看到,这个技术在未来会有极大的发展空间。

接下来,余振华谈到了CoWoS-S封装技术。如下图所示,这是一个已将量产超过十年的技术,且拥有极高的良率和质量,能够为先进的SoC和HBM集成提供非常好的支持。

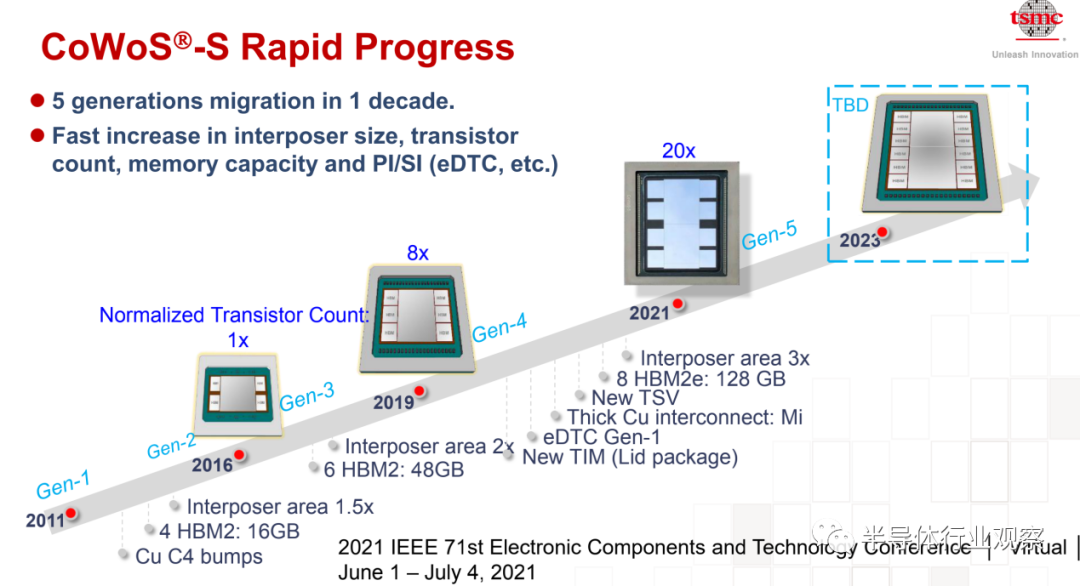

如下图所示,到2023年,公司将推出第五代的CoWoS-S技术。从相关规格可以看到,这个技术的每项参数都是在迅速增长。

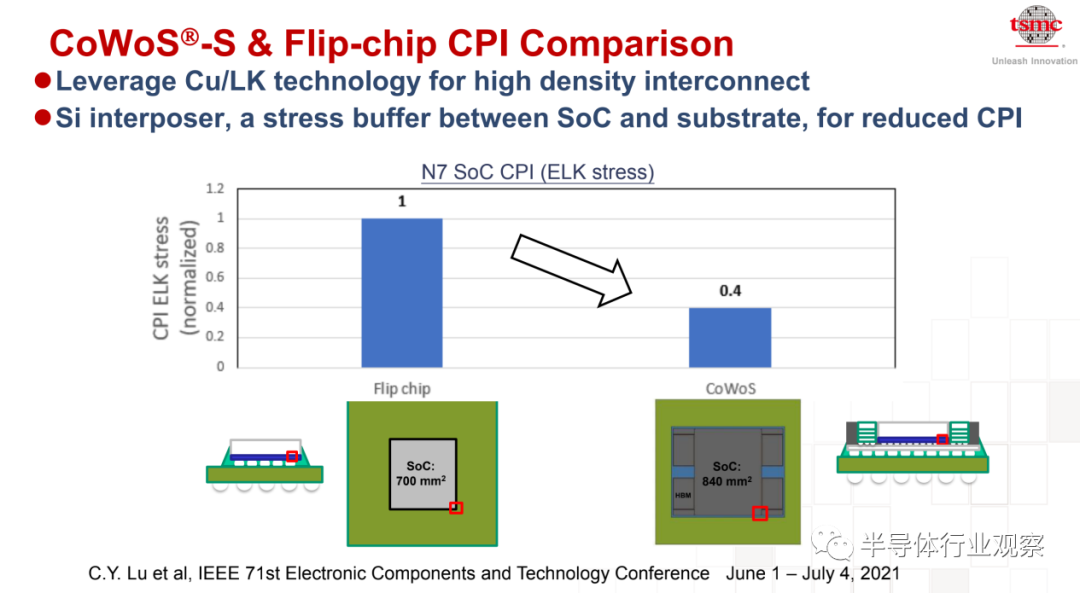

在与 Flip-chip 技术相比时,CoWoS-S的优势也是明显。

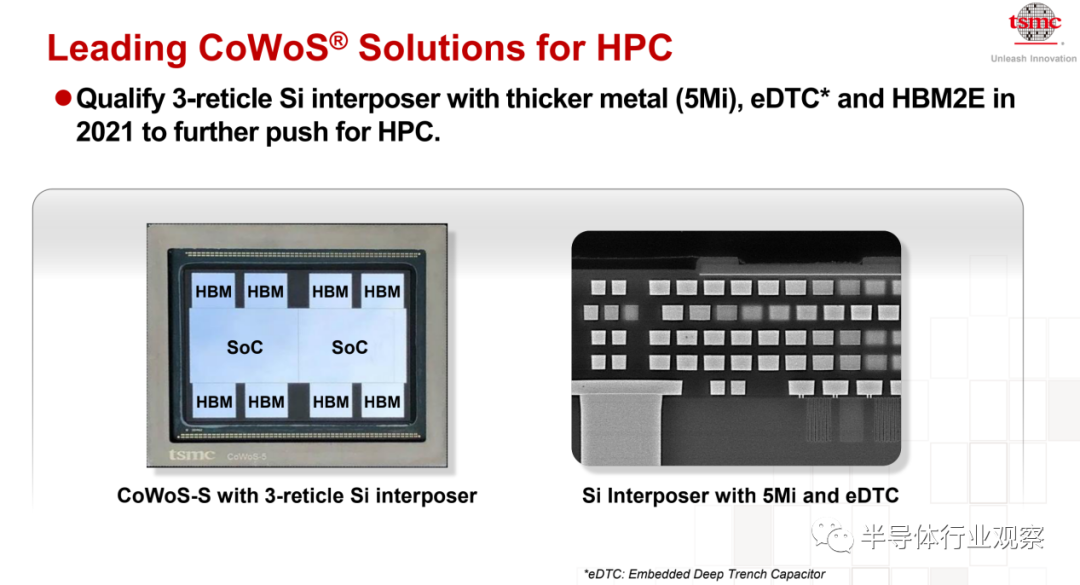

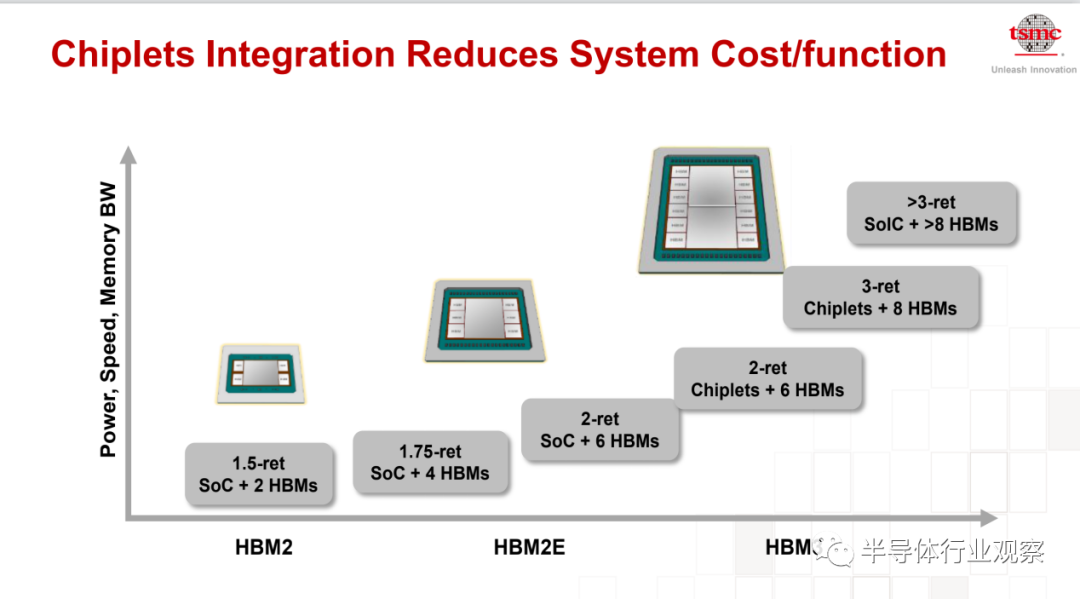

在面向HPC的应用方面,CoWoS解决方案也表现尤其出色。

余振华接着说,基于以上封装,并采用了chiplet集成之后,能够大幅降低系统的成本。

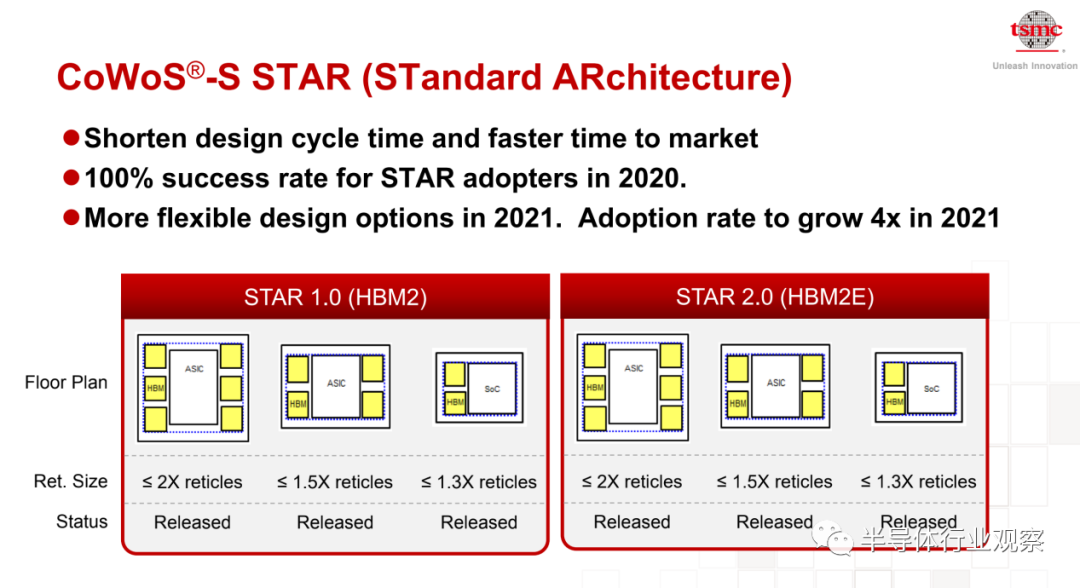

CoWoS-S STAR则是台积电封装宝库里面的另一武器。如图所示,这个封装技术能够缩短设计时间,加速客户产品上市。这是一个在2020年被客户采用的技术,而到了2021年,台积电则能为客户提供更多选择。

据半导体行业观察之前的报道,这个设计的实现是将单个 SoC 与多个高带宽存储器 (HBM) die堆栈集成。逻辑芯片和 HBM2E(第二代)堆栈之间的数据总线宽度非常大,即 1024 位。

通过 RDL 将 HBM堆栈连接到 SoC 的路由和信号完整性挑战是相当大的。TSMC 正在为系统公司提供多种标准 CoWoS-S 设计配置,以加快工程开发和电气分析进度。下图说明了一些不同的 CoWoS-S 选项,范围从 2 到 6 个 HBM2E 堆栈。

面向异构集成,台积电则提供了CoWoS-L封装技术。

在介绍完2.5D之后,余振华接着介绍台积电的3D芯片堆栈——SoIC。

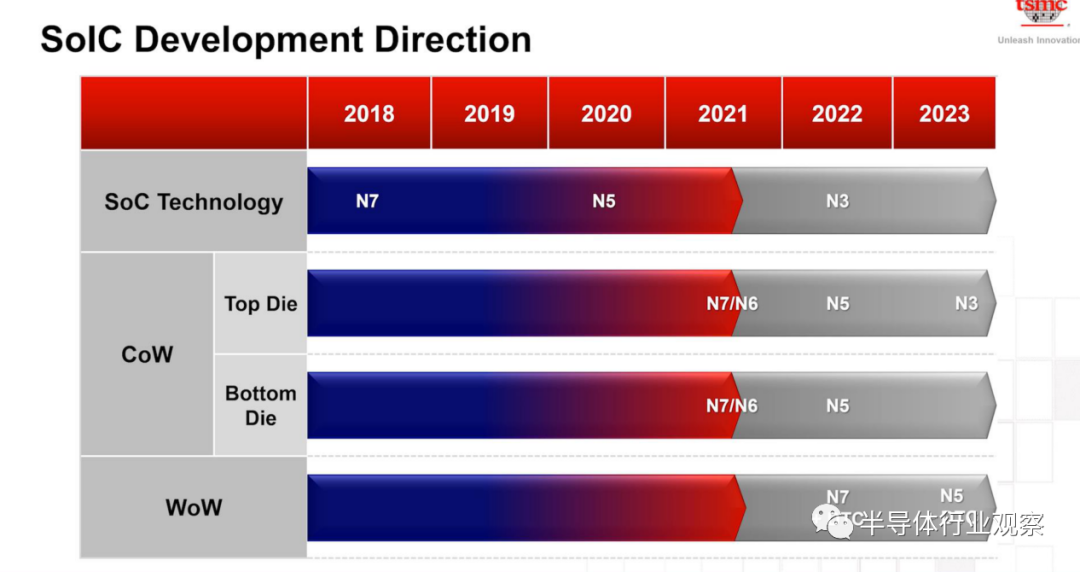

如下图所示,余振华披露了台积电SoIC的研发方向。

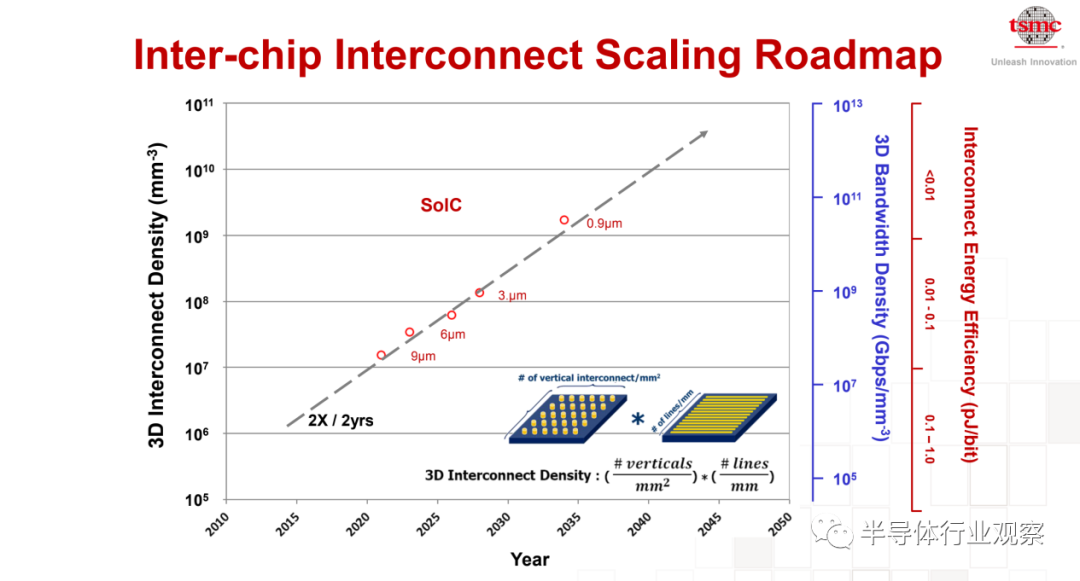

同时,余振华还透露了台积电Inter-chip互联的路线图。

在介绍完了一些之前其实也披露了不少的封装技术外,余振华还介绍了台积电的全新异构集成技术。

在介绍完了一些之前其实也披露了不少的封装技术外,余振华还介绍了台积电的全新异构集成技术。当中包括了先进的热解决方案和硅光集成。

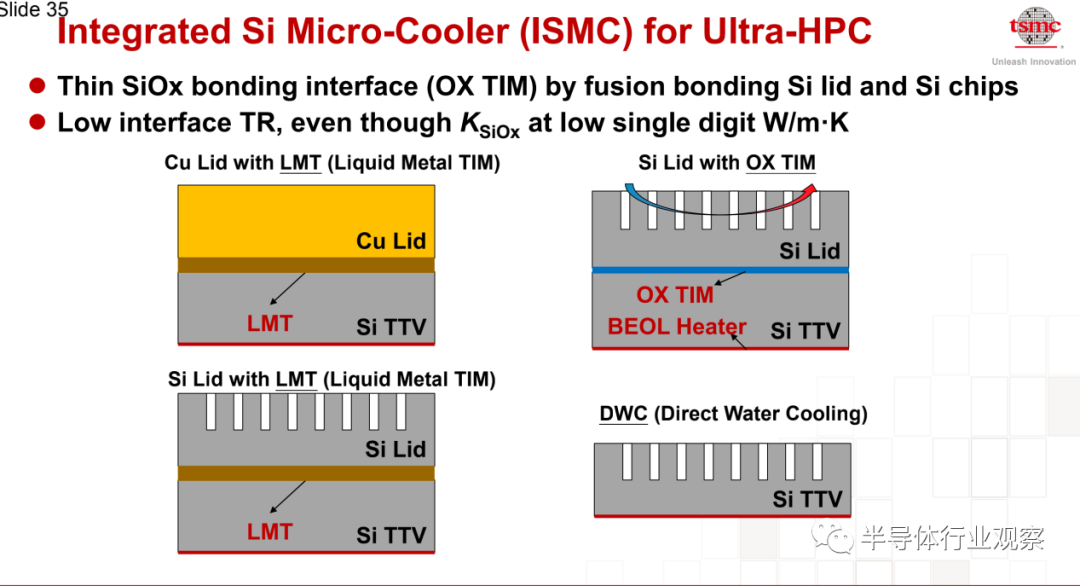

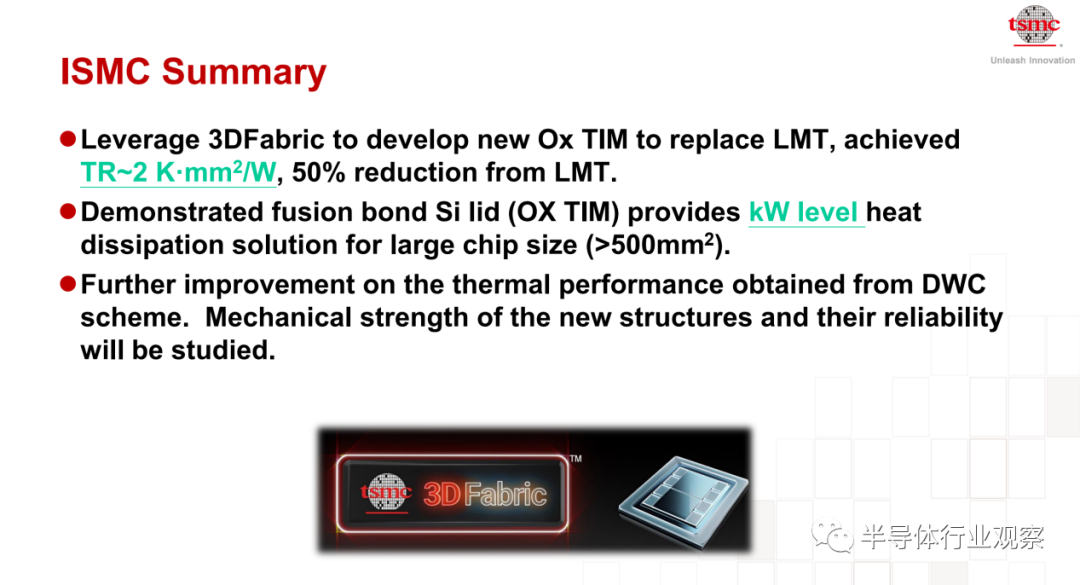

首先看热解决方面,如上图所示,据半导体行业观察之前报道,热界面材料 (hermal interface material:TIM) 薄膜通常包含在高级封装中,以帮助降低从有源die到周围环境的总热阻。(对于非常高功率的器件,通常应用两层 TIM 材料层——die和封装盖之间的内层以及封装和散热器之间的一层。)

对应于更大封装配置的功耗增加,台积电先进封装研发团队正在寻求新的内部 TIM 材料选项。

而面向Ultra-HPC,台积电则提供了Integrated Si Micro-Cooler (ISMC)选项。

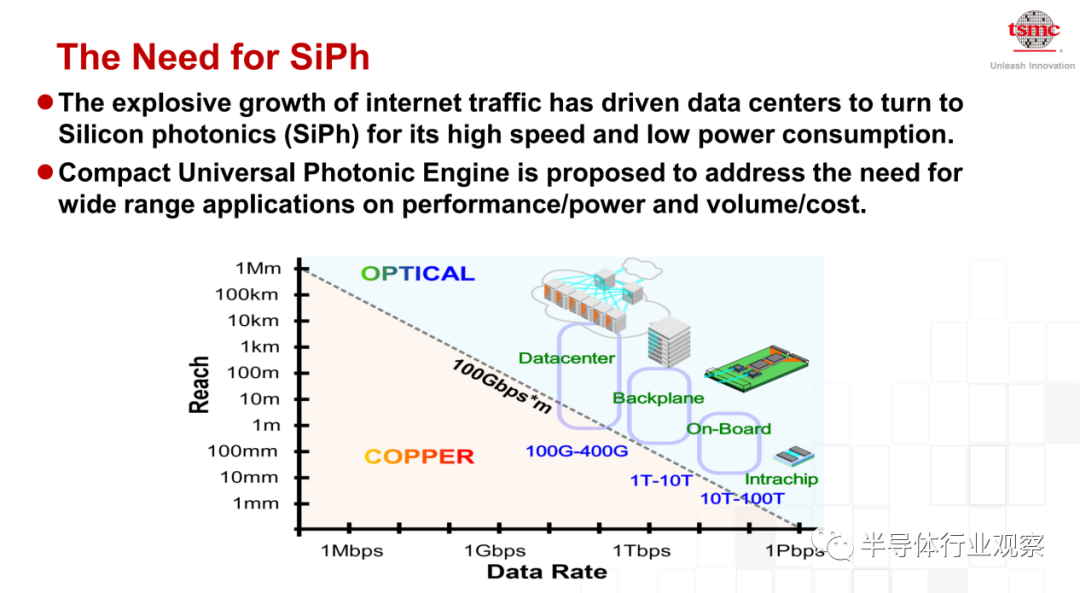

余振华接着说,如下图所示,市场对SiPh有很迫切的需求。

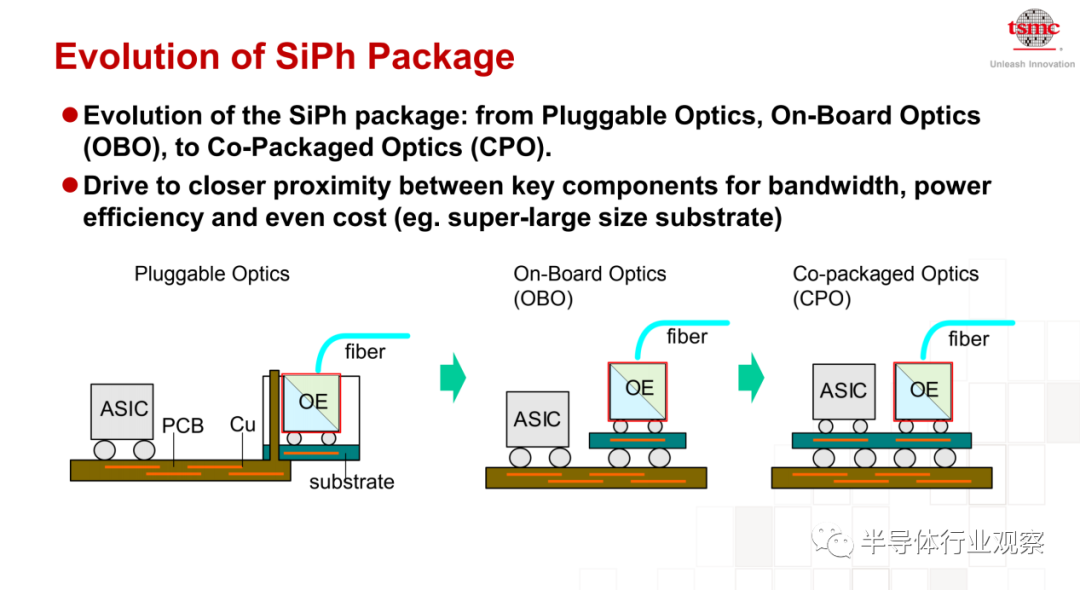

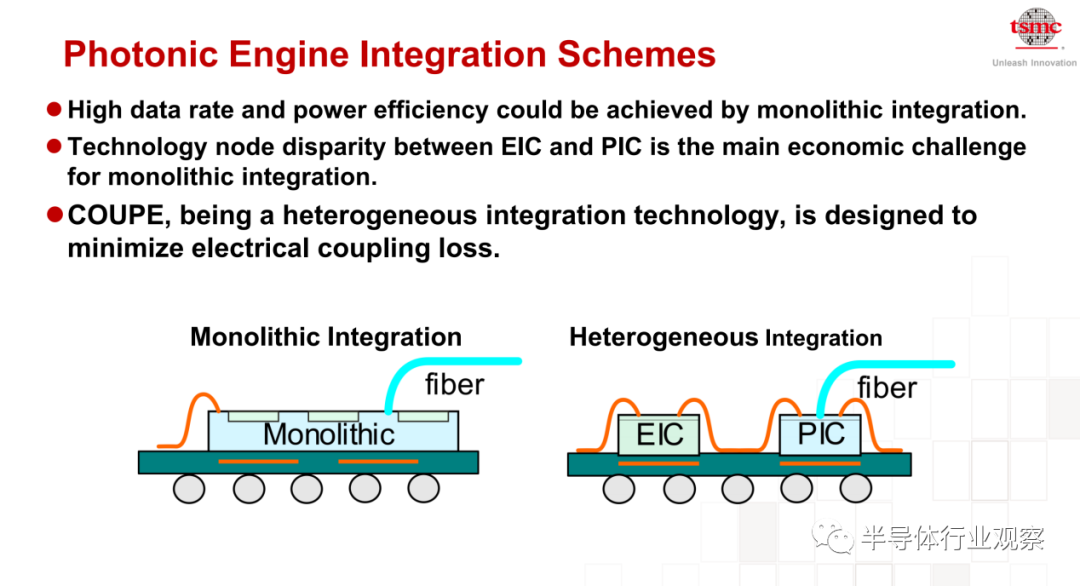

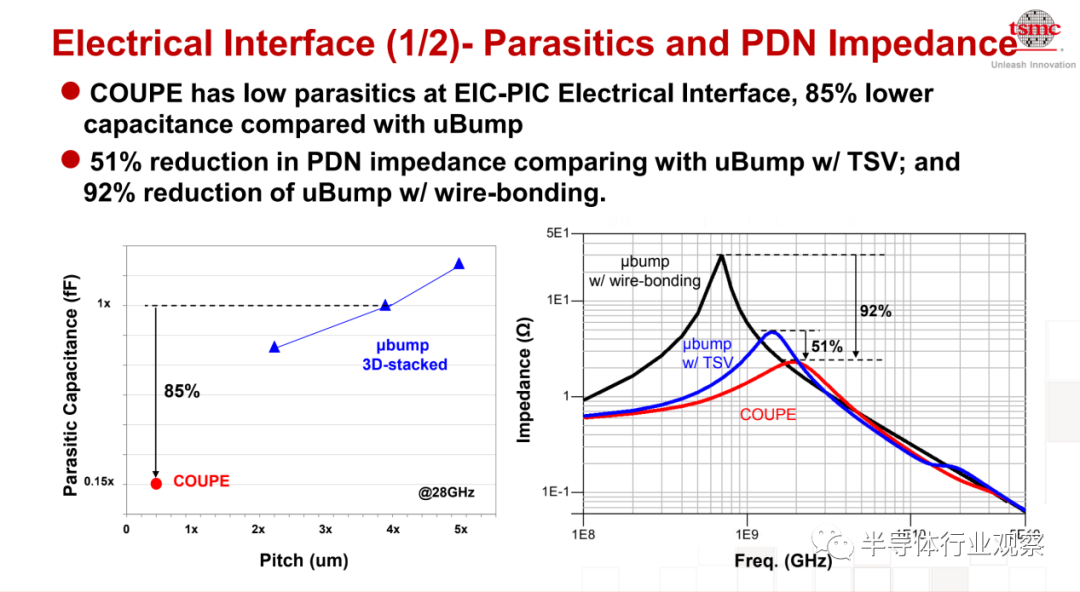

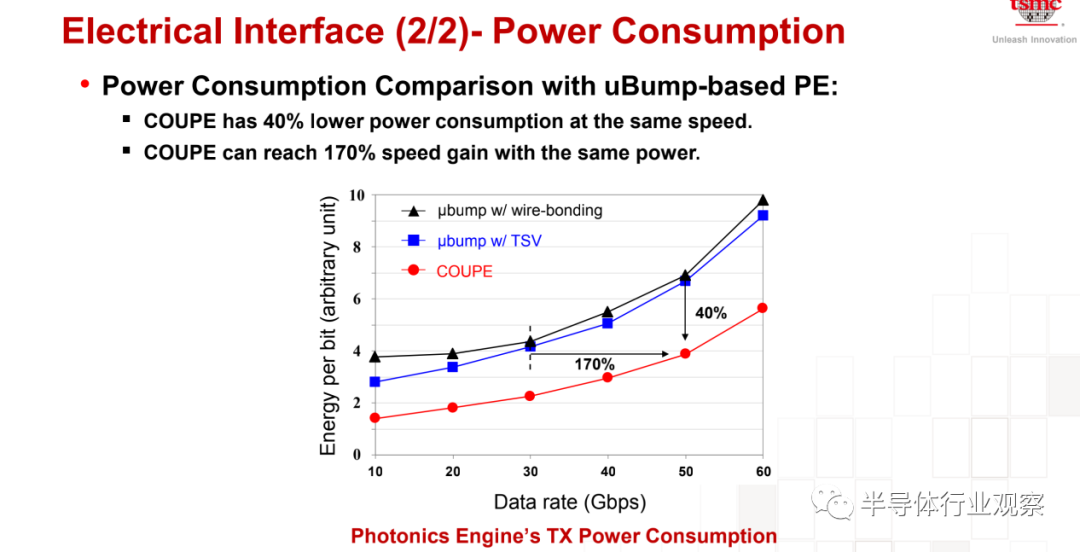

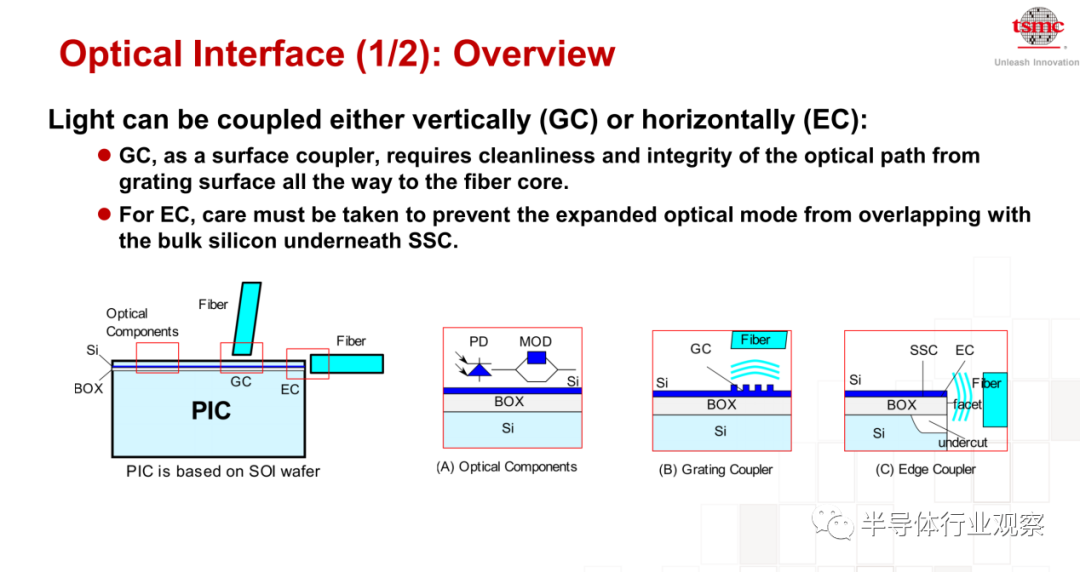

其中,异构集成技术COUPE,则成为当中的一个选择。如下图所示,这个技术在多方面都有领先的表现。

余振华最后总结道,包括3D Fabric在内的台积电封装技术将在未来发挥重要作用。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3024内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!