这种半导体将是芯片未来的关键

2022-04-03

14:00:26

来源: 半导体行业观察

来源:本文由半导体行业观察编译自allaboutcircuit。

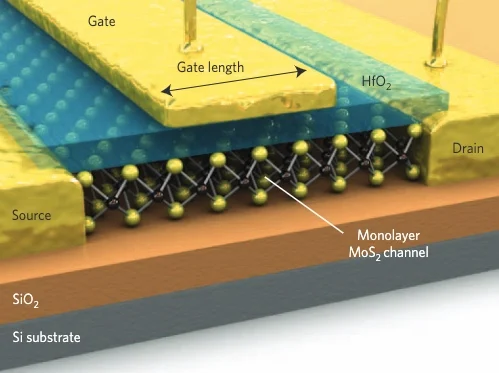

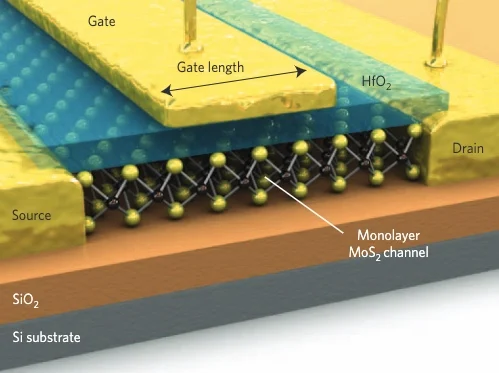

“找到与半导体良好的金属接触是一个与半导体本身一样古老的问题,”斯坦福大学的研究员 Aravindh Kumar 说。“随着每一种新的半导体被发现(在我们的案例中,原子级薄的半导体,如二硫化钼 (MoS

2

),寻找良好接触的问题再次浮出水面。”

Kumar 和他的同事研究人员 Katie Neilson 和 Kirstin Schauble 面临的问题是寻找接触电阻 (RC) 几乎为零的金属触点。当这些材料集成到电路、LED 或太阳能电池中时,替代方案将浪费金属-半导体结处的电压和功率。

为了应对这一挑战,这些斯坦福大学的研究人员最近开发了一种在单层二维半导体上制造合金金属触点的新技术。二维半导体上改进的金属-半导体接触电阻,结合过渡金属二硫化物 (TMD) 的光学特性,可能为下一代逻辑和存储技术铺平道路。

据研究人员称,二维半导体有望解决大尺寸晶体管中的通道控制问题:减小器件尺寸也会减小通道长度。界面缺陷(由于晶体管栅极沟道的小尺寸)导致载流子迁移率下降。

研究人员表示,MoS

2

等过渡金属二硫化物 (TMD) 是亚 10nm 沟道晶体管的首选材料,因为它们在极薄的厚度下具有高迁移率。

我们小组之前的一项研究表明,镍 (Ni) 和钯 (Pd) 等高熔点金属 在沉积在单层 MoS

2

上时会造成损坏。作为一种精致的三原子厚材料,这会严重降低其电子性能。因此,我们和其他小组尝试了低熔点金属,例如铟(In)和锡(Sn),看看它们是否会减少对MoS

2

的损害。拉曼光谱表明它们实际上对单层 MoS

2

造成的损伤可以忽略不计。In 和 Sn 非常容易氧化,因此我们用金 (Au) 盖住这些低熔点金属触点,发现这些触点的性能非常好。

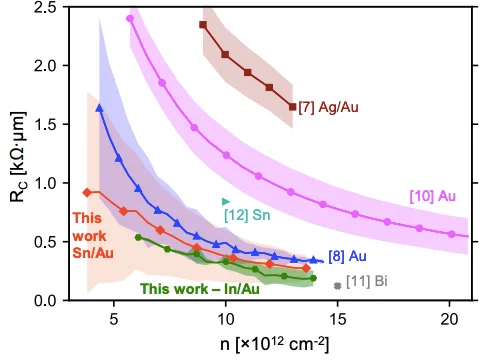

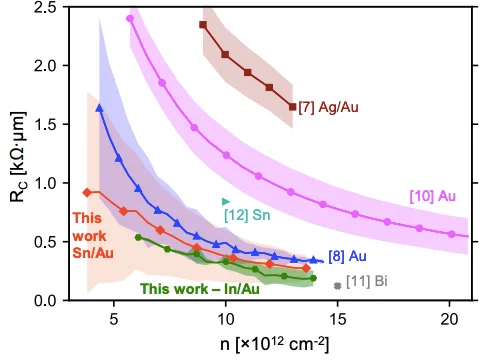

为了防止浪费电压和功率,研究人员寻找了几乎没有接触电阻 (RC) 的金属触点。目前,市场上RC最少的最著名触点是银/金(Ag/Au)、金(Au)和锡(Sn)。

斯坦福大学的研究人员成功地制造了 In/Au 和 Sn/Au 合金触点,其接触电阻分别低至 190 ohm.µm 和 270 ohm.µm。

与单层MoS

2

的最佳报告接触之间的 RC 比较

“我会说我们偶然想到了这种合金化技术,”该团队解释说。“然后,我们专注于合金化方面,因为这将确保这些触点的热稳定性和化学稳定性。例如,In/Au 合金的熔点将高于纯 In,这使得它们对于晶体管制造中的任何后续加工都更加工业友好。”

据该团队称,这项研究最具挑战性的方面是让这些二维半导体晶体管可靠且可重复地工作。研究人员指出:“我们不只是为一次性的‘英雄’设备——即表现非常好的单个晶体管而产生。” “相反,我们希望展示整个芯片的接触电阻在统计上相关的改进。因此,虽然我们在最初的实验中拥有出色的产品,但成品率或成功率很低。”

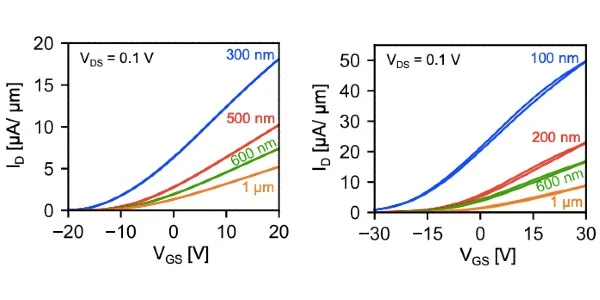

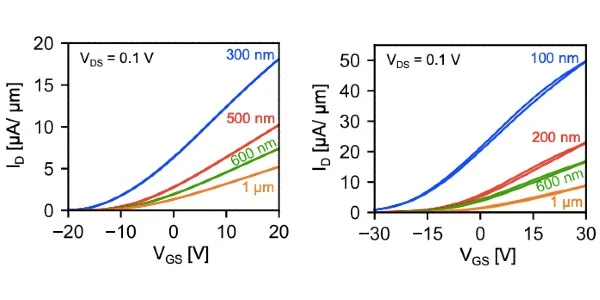

Sn/Au(左)和 In/Au(右)的I

D

与V

GS

的关系

例如,研究人员假设,如果他们最初制造 100 个产品,那么其中只有两三个会表现良好。经过数月的反复试验,该团队试图确定设备制造过程和测试方法,以确保他们创造出可重现的芯片范围内的结果。

在团队研究的早期阶段,他们只能在只有一到三个原子厚的二维通道的晶体管上实现良好的电气性能。由于 2D TMD 本质上是原子级薄,因此它们在低温下生长以避免熔化通常用于芯片互连的金属——这与晶体硅形成鲜明对比。

虽然研究人员承认硅“仍然是高性能逻辑晶体管的黄金标准”,但他们对 2D TMD 晶体管的未来表示乐观,这可能有助于在基极上堆叠逻辑和存储器层硅 CMOS 层。

有许多迹象表明,摩尔定律的未来将由 3D 集成芯片形式的堆叠晶体管驱动,这可以缓解内存带宽问题或“内存墙”。3D 集成芯片也可能彻底改变设计和布线方法。

2D 半导体可能是创建此类 3D 集成芯片的关键解决方案,因为它们可以在低温下轻松生长,同时保持电气特性完好无损。由于高电阻触点一直是采用二维半导体的障碍,因此这项研究对于大规模制造良好的工业级二维半导体可能具有开创性。

研究人员详细说明,“如果或当高质量、低温生长可以扩展到 12 英寸晶圆时,TMD 将在堆叠在硅逻辑顶部的存储器和计算层中发挥作用。它们还可以作为嵌入式 DRAM、SRAM 高速缓存中的访问晶体管或 3D 闪存晶体管。”

他们补充说:“与硅晶体管相比,前两个示例受益于更低的关态电流,因为单层 TMD 的能带隙比硅大。”

2019年,台积电宣布将开始生产SiGe作为其5nm工艺的PMOS沟道材料。锗的研究始于 2000 年代初,这项研究花了将近 20 年的时间才到达生产单位。2D 半导体研究始于 2011 年左右,自那时以来取得了巨大进展。

根据斯坦福大学的研究人员的说法,从 Ge 时间线推断,2D TMD 最早可能会在 2030 年出现在消费电子产品中是公平的。但是,仍然存在一些开放的挑战,例如提高通道移动性和探索 P 型通道候选者。在这些问题得到解决之前,其他新型二维半导体材料将面临激烈的竞争。

该团队表示,摩尔定律的延续依赖于新材料、设备架构和解决方案。“因为原子级薄的二维材料(如 MoS 2)是扩展摩尔定律的候选材料之一,因此必须优化它们的触点,以使其成为硅的合适替代品或补充品,”他们断言。“降低接触电阻的解决方案,例如我们提出的合金触点,可以实现更高的电流和更好的节能效果。”

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2999内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie