Intel发布全新FPGA,瞄准挖矿等应用

来源:内容来自半导体行业观察(ID:icbank)综合,谢谢。

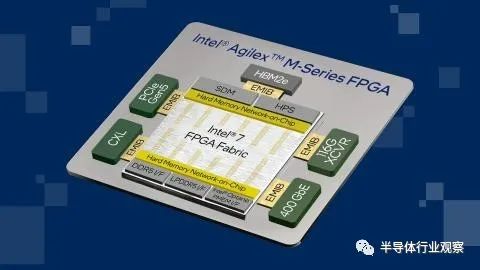

英特尔 Agilex M 系列 FPGA介绍

随着当今世界数据的指数级增长,再加上从集中式计算和数据存储集群向更加分布式的架构转变,该架构可以在任何地方处理数据——在云中、边缘以及两者之间的所有点——现场可编程门阵列 (FPGA) 在从数据中心到网络再到边缘的现代应用中发挥着越来越重要的作用。

FPGA 的灵活性、功率效率、大规模并行架构和巨大的输入/输出 (I/O) 带宽使 FPGA 在加速从高性能计算 (HPC) 到存储和网络的各种任务方面具有吸引力。其中许多应用对内存提出了巨大的要求,包括容量、带宽、延迟和功率效率。

为了处理这些高需求的应用,英特尔® Agilex™ M 系列 FPGA 的产品震撼亮相,该产品基于Intel 7 工艺技术,业界最高内存带宽的 FPGA,采用封装 HBM DRAM。英特尔 Agilex M 系列整合了多项新的功能创新和特性,为行业提供了满足网络、云和嵌入式边缘应用程序的更雄心勃勃的性能和能力目标所需的高速网络、计算和内存加速。

新功能包 括:

-

业界最高的 FPGA 内存带宽。

-

在支持 HBM 的 FPGA 中实现业界最高的 DSP 计算密度。

-

与具有竞争力的 7nmFPGA 相比,每瓦结构性能提高 2 倍以上。

英特尔 Agilex M 系列 FPGA 是英特尔 Agilex 器件系列中首批提供封装 HBM2e 内存的成员,并包括适用于 DDR4、DDR5 和 LPDDR5 等其他最先进内存技术的硬化控制器。两个硬化内存片上网络 (NoC) 功能为 FPGA 架构提供了对封装内 HBM2e 和板载内存资源的高带宽、资源高效访问。

此外,英特尔 Agilex M 系列 FPGA 提供一流的收发器数据速率,这对于系统处理当今巨大的数据负载至关重要。凭借对PCI Express (PCIe) Gen5、Compute Express Link、400G 以太网和高达 116 Gbps 的串行收发器的支持,英特尔 Agilex M 系列设备支持从数据中心到边缘的最苛刻应用的吞吐量要求。

受益于 Intel Agilex M 系列 FPGA 的市场包括但不限于测试和测量(任意波形发生器、5G/6G 蜂窝网络测试、GHz 射频测试);数据中心(HPC、云计算、加密货币挖掘);无线和有线(高数据速率 (800G+) 传输、光传输网络 (OTN)、网络功能虚拟化 (NFV)、5G 基带)以及航空航天和国防(雷达、电子战)。

使用 Agilex M 系列 FPGA 应对最大的内存和计算挑战

据介绍,M系列中的“M”表示“内存”。更多更快的内存无疑是英特尔Agilex M 系列 FPGA 的一项显着且重要的优势。几乎无一例外,高级应用程序需要从快速到更快再到最快的内存层次结构,同时允许设计团队在内存带宽和延迟与内存容量之间进行权衡。英特尔 Agilex M 系列 FPGA 具有广泛而灵活的内存层次结构,包括超低延迟、超高带宽、片上 SRAM;HBM2e(高带宽内存)DRAM堆栈形式的更高容量、高带宽、封装内存;支持快速、大容量的外部同步 DRAM (SDRAM),包括 DDR4、DDR5 和 LPDDR5;和超大容量、非易失性英特尔® 傲腾™ 持久内存。

所有英特尔 Agilex FPGA,包括 M 系列的成员,都包括 MLAB 和M20K 块形式的快速片上 SRAM。这些 SRAM 集成到 FPGA 的可编程逻辑结构中,紧邻与这些存储器交换数据的逻辑。一些英特尔 AgilexM 系列 FPGA 还包含 HBM2e 内存堆栈形式的封装 HBM,由硬化内存控制器管理。

英特尔 Agilex M 系列 FPGA 通过合并两个 HBM2e DRAM 堆栈进一步推动了 HBM 封装。英特尔 Agilex M 系列 FPGA 中的两个封装内 HBM2e DRAM 堆栈提供最大 32 GB 和每个 HBM2e 堆栈高达 410 GB/秒的内存带宽,总封装内 HBM2e 内存带宽高达 820 GB /第二。与上一代英特尔 Stratix 10 MX FPGA 相比,带宽增加了 60%,这使设计人员能够在更具挑战性的系统设计中使用英特尔 Agilex M 系列 FPGA。

对于需要额外高速 DRAM 容量的应用,英特尔 Agilex M 系列 FPGA 还通过集成、硬化、高效的内存控制器支持外部 DDR5 和 LPDDR5 SDRAM。英特尔 Agilex M 系列 FPGA 与英特尔 傲腾 持久内存为系统设计人员在构建系统特定的内存层次结构时提供了额外的灵活性和更大的内存容量。

DDR5 和 LPDDR5 SDRAM 是目前最快的主流SDRAM DIMM。英特尔 Agilex M 系列 FPGA中的每个独立内存控制器都可以以 5600 MTransfers/秒的速度运行 DDR5 SDRAM,数据宽度高达每通道 40 位(加上 ECC 位)。当 HBM2e 和DDR5 内存带宽相结合时,带有 8 个连接的 DDR5SDRAM DIMM 的 Intel Agilex M 系列FPGA 可提供 1.099 TBytes/秒的理论最大内存带宽。

在 FPGA 的可编程逻辑结构与 HBM2e 和 DDR5 存储器之间传输 1TB/秒的数据可能具有挑战性。这一潜在瓶颈推动了英特尔 Agilex M 系列 FPGA 的另一项创新的开发:双核硬化片上内存网络 (NoC)。该内存 NoC 充当将封装内 HBM2e DRAM、外部 DDR5 SDRAM 和 FPGA 的高速外部 I/O 连接到 FPGA 架构的高速公路。双内存 NoC 的总峰值带宽为 7.52 TBytes/秒——这是一个真正巨大的片上带宽,不会消耗 FPGA 的片上可编程逻辑资源——这大大降低了内存瓶颈的可能性。

众所周知,将数据平稳地移入和移出该存储器层次结构以及整个 FPGA 对于满足激进的系统级性能目标至关重要,但设计人员能够访问其他可以在外部系统和外部系统之间移动数据的高带宽资源同样也很重要。英特尔 Agilex M 系列 FPGA 包含多达 72 个高速 SERDES 收发器,其中包括多达 8 个收发器,每个收发器都可以使用 PAM4 调制以 116 Gbps 的速度在 FPGA 和系统的其余部分之间以非常高的速度交换数据数据速率。Intel Agilex M 系列 SERDES 收发器支持当今各种新兴的行业标准高速串行协议,包括 400G 以太网,并且可以直接连接到高级 CPU,包括使用 PCIe Gen 5 和 CXL 的最新 Intel® Xeon CPU接口协议。

最后,一旦数据进入 FPGA,通常必须通过各种计算算法对其进行处理。英特尔 Agilex M 系列 FPGA 中的可编程逻辑架构速度极快,可以以高数据速率实现各种计算算法。此外,这种可编程逻辑结构包含多达 12,300 个精度可调的浮点 DSP 模块,能够提供 18.5 单精度 TFLOPS 或88.6 INT8 TOPS,以处理更重的计算负载。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2974内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 ISSCC 2020年论文解析:硅光与电路集成

- 2 蓝牙技术联盟宣布2025蓝牙亚洲大会重磅回归

- 3 宇都通讯:深耕UWB技术,助力低空经济新发展

- 4 江波龙全球最小尺寸eMMC,为AI穿戴设备“减负”