来源:内容由半导体行业观察(ID:icbank)

编译自semiwiki

,谢谢。

<iframe allowfullscreen="" class="video_iframe rich_pages" data-cover="http%3A%2F%2Fmmbiz.qpic.cn%2Fmmbiz_jpg%2FghsnibD4zwPsqqxwnAH4Q7ia3lJOkYNPVbsFAIOibmXk1r6CF7QQEeY8oYibnjuCjGbNRibIrvxFNk2MXNavM57ZkJA%2F0%3Fwx_fmt%3Djpeg" data-mpvid="wxv_2294525277844078595" data-ratio="1.7777777777777777" data-src="https://mp.weixin.qq.com/mp/readtemplate?t=pages/video_player_tmpl&action=mpvideo&auto=0&vid=wxv_2294525277844078595" data-vidtype="2" data-w="1280" frameborder="0">

</iframe>

英特尔最近发布了一段出色的视频,提供了 MOS 晶体管技术的深刻年表。 晶体管创新的演变是一个五分钟的视听冒险,展现跨越 50 年的摩尔定律。下面总结了一些亮点,并附有一些屏幕截图——完整的视频绝对值得观看。

演讲者是拥有 16 年以上英特尔经验的资深人士Marisa Ahmed,她是技术领导营销团队的成员。Marissa 负责制定技术营销策略和活动,以支持英特尔的工艺、封装和制造能力。

上图建立了 MOS 场效应晶体管的基线,大约在 1971 年。

(请注意以下晶体管横截面提供的附加补充信息——例如,释放的晶体管总数;用于工艺生成的金属层数;光刻图案的曝光波长;晶圆尺寸;以及相关的英特尔产品系列。)

Polycide和Salicide:1979-81

随着器件栅极长度的 Dennard 缩放,多晶硅栅极材料的薄层电阻率正在增加。同样,晶体管漏极/源极串联电阻(Rs,Rd)也在增加。由于 S/D 结深度的缩放,金属层的接触电阻 (Rc) 也在增加。为了解决这些有问题的寄生效应,出现了一种制造硅化物的工艺创新。在高温下沉积难熔金属(例如钛)并与暴露的硅合金化。(Salicide 是“自对准硅化物”的复合术语——沉积的金属不会与相邻的介电材料发生反应。)

在从 LoCoS(local oxidation of silicon) 到浅STI(shallow trench isolation)的过渡过程中,器件电隔离和表面形貌发生了重大变化。

LoCoS 是一种工艺方法,其中通过在器件区域上图案化硬掩模并将场暴露于氧化环境来形成器件之间的场氧化物隔离。氧气会从高温环境中扩散通过生长场氧化层到达氧化物-衬底界面处的硅晶体。由此产生的氧化物轮廓是锥形(“鸟嘴”)表面形貌,更适合器件之间的金属穿越。

为了促进进一步的缩放,引入了一种用于场氧化物分离的新工艺。STI 利用了各向异性干法蚀刻技术(具有接近垂直的侧壁)的重大改进以及介电材料的化学气相沉积。

1990 年代后期的一个分水岭(非器件)工艺改进是从铝金属化过渡到铜。Dennard 缩放继续实现更大的器件电流和更低的器件电容。这个时代的标志是从以栅极扇出负载为主的电路延迟过渡到从驱动栅极输出到扇出的 R*C 互连延迟的显着贡献。对具有改进的电阻率和电迁移鲁棒性的互连的需求需要从 Al 到 Cu 的过渡。

在这种材料转变的同时,需要对互连图案进行重大转变。作为主要互连的铝涉及相当简单的沉积、光刻和减材去除工艺流程。由于与铜的干法蚀刻相关的化学困难 - 例如腐蚀性气体,几乎没有挥发性铜基反应产物要泵出 - 需要一种镶嵌图案化方法。沉积围绕金属的电介质,在电介质中蚀刻沟槽(以及下方的层间电介质用于通孔),然后通过电镀将铜沉积在沟槽中。

除了添加镶嵌工艺取代了减材铝蚀刻方法,因此也有必要发展化学机械抛光(CMP) 工艺步骤。将沉积有 Cu 的晶片表面面朝下放置在抛光垫上,该抛光垫以低速旋转。较高 RPM 的旋转活塞在晶片上提供适当的向下力 (Newtons/cm**2),并将浆液引入到垫上。浆液由化学溶液和细砂粒组成。该化学品旨在选择性地与要去除的材料(在这种情况下为铜)发生反应,而机械抛光会去除反应的结果。产生了极其平坦的表面形貌。如上图以及随后的图所示,CMP 使可用于互连缩放电路密度的金属层数量急需增加。

器件发展遇到了栅极氧化物厚度持续缩放的问题。输入栅极电场对器件沟道的影响需要缩放栅极氧化层电容:Cg ~ ((K*E0)/t),其中 K 为相对介电常数,t 为栅极氧化层厚度。随着栅极氧化物变得更薄,通过器件输入的栅极隧穿电流增加。为了在不降低厚度的情况下等效地增加 Cg,替代性的高 K介电材料替代了 SiO2 作为栅极氧化物。

缩放传统的多晶硅栅极材料会导致更高的电阻率以及对多晶硅晶粒尺寸、分布和杂质浓度的不均匀性的更大敏感性。引入了替代金属栅极工艺步骤,取代了多晶硅作为栅极材料。(有关这个相当困难的步骤的更多信息,请继续搜索高 K 金属栅极“HKMG 先栅极与后栅极”工艺;上图中的术语替换是指后栅极流程。)

英特尔在 22nm 工艺节点上积极采用新的晶体管拓扑结构——FinFET(也称为“三栅极 FET”),令业界大吃一惊。

当器件“关闭”时,传统的平面 S/D 通道拓扑在源极和漏极之间的(子通道)泄漏电流问题越来越严重。为了减少亚阈值泄漏,需要一种器件拓扑结构,其中栅极输入对通道提供更大的静电控制。垂直通道“鳍”具有穿过侧壁和顶部的输入栅极。在上图中,单个栅极输入穿过三个并联的硅鳍片——通道电流流过垂直鳍片。鳍片的厚度足够小,因此栅极输入电场控制可显着降低亚阈值泄漏,从而为笔记本电脑和移动电子设备提供更长的电池寿命。

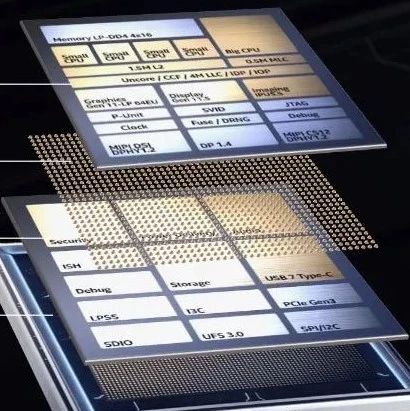

Gate-All Around (GAA) Ribbon FET:2024 年 Intel 20A

为了进一步改善对通道的静电栅极控制,晶体管拓扑结构的另一项重大发展正在出现以取代 FinFET。环栅配置涉及电隔离硅通道的垂直堆叠。栅极电介质和栅极输入利用原子层沉积 (ALD) 工艺流程围绕堆栈中的所有通道表面。

英特尔将于 2024 年发布其 GAA Ribbon FET 20A 工艺。

这一演变得益于整个行业的研发团队的创新理念和辛勤工作,他们拥有从材料科学到化学到光学光刻到物理沉积/蚀刻工艺步骤的专业知识。令人难以置信的是,这一进展绝对不会很快停止。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2969内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!