来源:内容由半导体行业观察(ID:icbank)

综合自semiconductor-digest

,谢谢。

据外媒semiconductor-digest报道,过去几个月发生了一系列有趣的事件,首先是在 7 月的英特尔加速活动上宣布亚马逊将成为英特尔代工服务 (IFS) 的首批客户之一,特别是在封装方面。

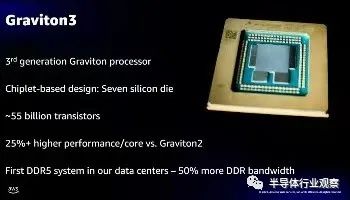

11 月 30 日至 12 月 3 日,亚马逊举行了他们的AWS re:Invent聚会,他们在会上推出了 Graviton3 数据中心处理器。与早期的 Graviton 和 Graviton2 器件不同,Graviton3 采用小芯片路线,具有 7 个裸片和总共 550 亿个晶体管。

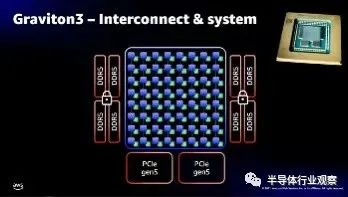

核心处理器芯片侧面的芯片是DDR5内存控制器,底部是 PCI-Express 5.0 控制器芯片。据称采用的是台积电5nm工艺,运行频率为2.6GHz,功耗为100W,略低于Graviton2的110W。似乎有 500 亿个晶体管位于处理器芯片中。

该处理器有 64 个内核与一个运行在 >2 GHz 且带宽超过 2 TB/s 的网格缝合在一起。32 MB 的缓存内存分布在网格中,与核心缓存一起,芯片上的缓存增加到 100 MB。DDR 控制器为 DDR4800,提供超过 300 GB/s 的内存带宽。

鉴于 Graviton3 封装的外观以及 Amazon/Intel IFS 封装声明,我怀疑这些小芯片是否与英特尔的 EMIB(嵌入式多芯片互连桥接)技术相关联。二加二可以得到 22,但在英特尔的最后一个季度电话会议中,我们有评论说,自 3 月以来,他们已经出货了第一批 IFS 封装单元以获取收入。Graviton3 部件现在可用于预览新的 Amazon EC2 C7g 实例,因此它们显然存在于 AWS 服务器中。

对我来说,最后一个确认链接是互连凸块间距据报道为 55 µm;这就是EMIB使用的。

所以,二加二仍然可以得到 22,但在我看来,Graviton3 至少有可能使用 EMIB 将这些小芯片连接在一起,而 AWS 是 IFS 的第一个收入客户。

低成本异构多芯片封装(multi-chip packaging:MCP)的发展推动了重大的系统级产品创新,进而出现了三类MCP产品:

2.5D解决方案已获得了可观的研发投资,以支持更大的封装尺寸和更大的互连重新分布密度(即,线+间距,金属层数)。多个较小裸片的集成提供了芯片和封装组装的良率和成本的权衡。

2.5D MCP中集成的功能已经变得越来越多样化,例如,CPU,GPU,内存(尤其是HBM堆栈),FPGA,网络交换机,I / O收发器,用于特定应用的硬件加速器。当前的研发工作将继续扩大这种系统级封装组成的广度。下一个“大事”很可能是光电转换元件的集成,从而实现中短距离的基于光子的数据传输效率通道。

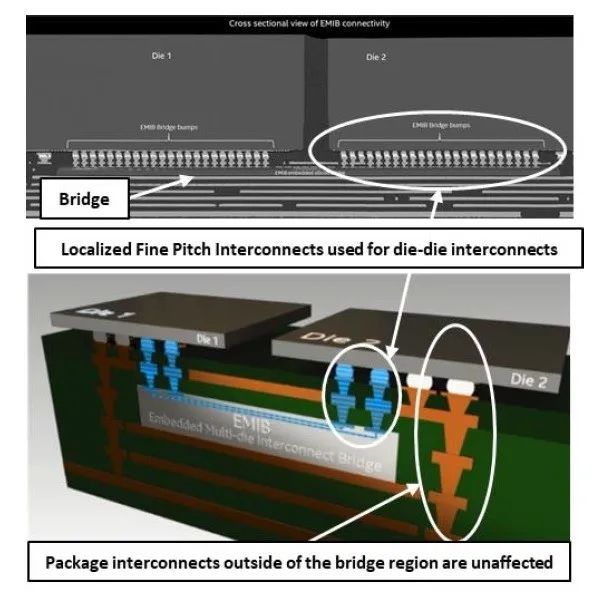

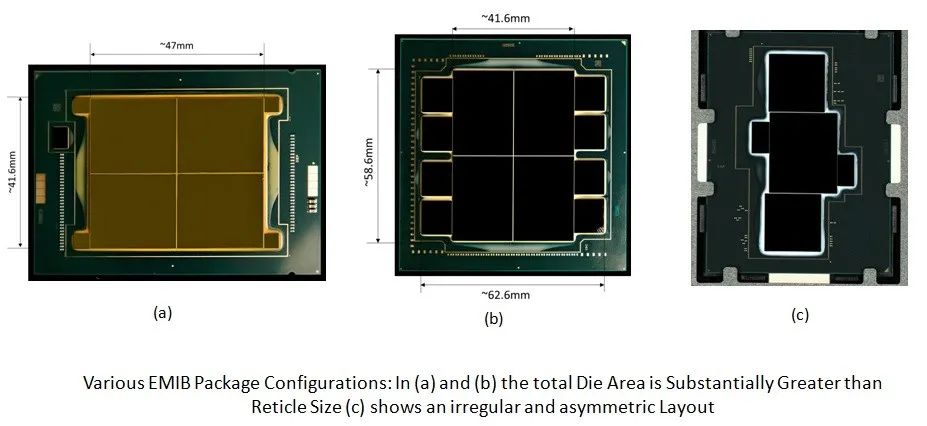

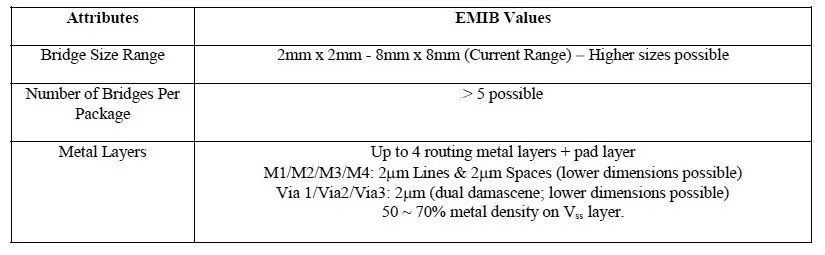

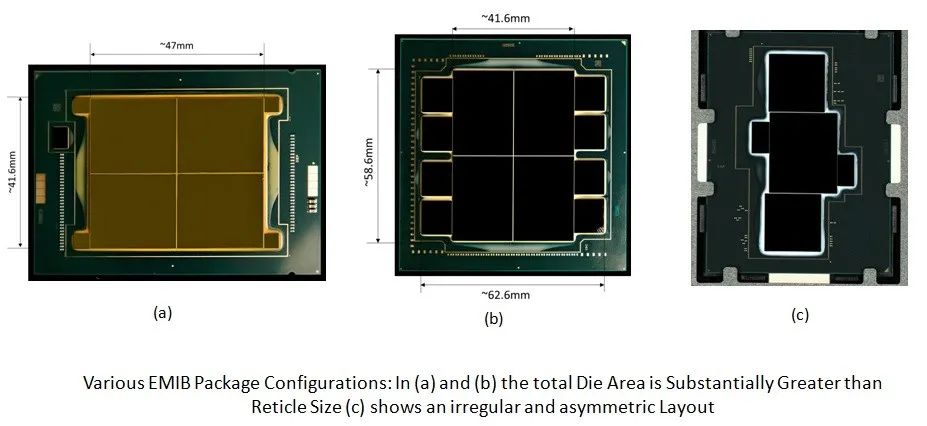

支持2.5D MCP产品增长的一个关键方面是封装中裸片之间的内部连接技术。如上所述,一种替代方法是在硅中介层上制造导线,该中介层的尺寸等于整个封装的尺寸。近期的发展使内插器(interposers )的裸片放置和互连能力超过了最大标线片尺寸(reticle size)的1倍。另一种方法是制造用于导线的小硅桥,该桥跨接在相邻de的边缘中,并嵌入有机封装中。

英特尔的嵌入式多芯片互连桥(Embedded Multi-Die Interconnect Bridge:EMIB)是2.5D MCP桥互连技术的一个示例。在先前的SemiWiki文章中已对此进行了简要描述。

随着最近对Intel Foundry Services的重新引入,我认为应该更深入地研究该技术,因为它无疑将成为ICF客户系统实施的基本组成部分。

在与封装和测试技术开发部门的英特尔研究员Ravi Mahajan进行的最启发性的讨论中,我有机会了解了更多有关EMIB功能和潜力的信息。本文总结了我们讨论的重点。

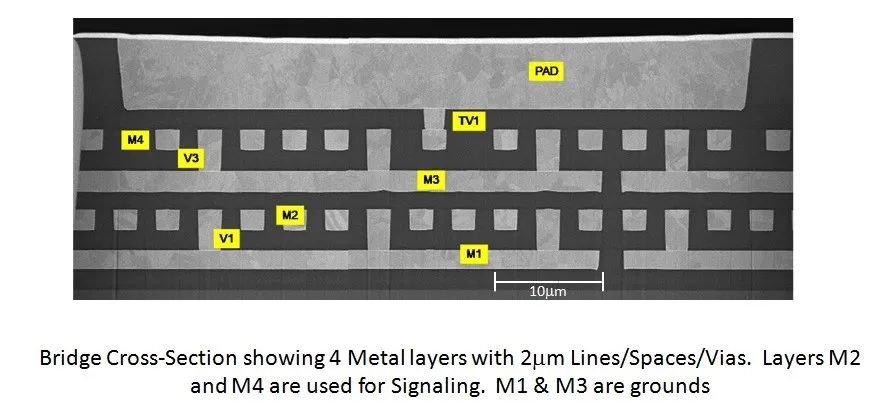

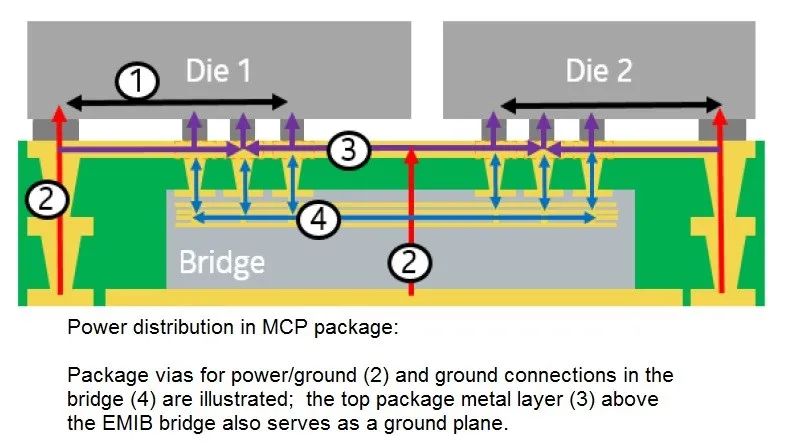

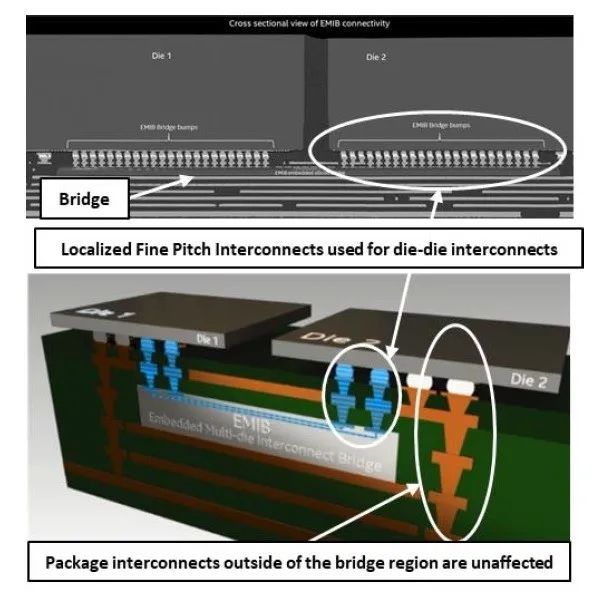

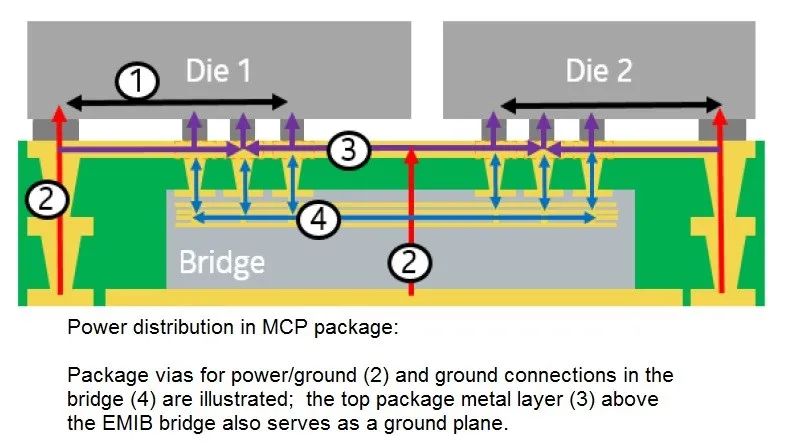

上图显示了设计在有机封装中的典型EMIB桥的横截面。桥接硅位于封装腔中,如下图所示制作。顶部封装金属层提供了一个参考平面,并带有穿过该平面的通孔,用于连接die和桥。

Ravi表示:“ EMIB工艺建立在标准封装构造流程的基础上,并附加了创建EMIB腔的步骤。桥位于空腔中,并用粘合剂固定在适当的位置。添加最后的介电层和金属堆积层,然后进行通孔钻孔和电镀。”

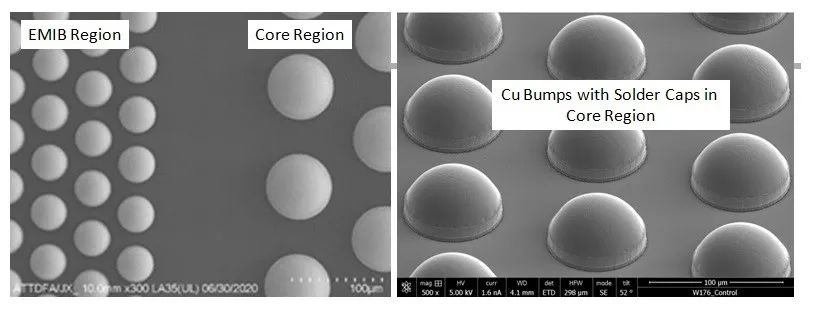

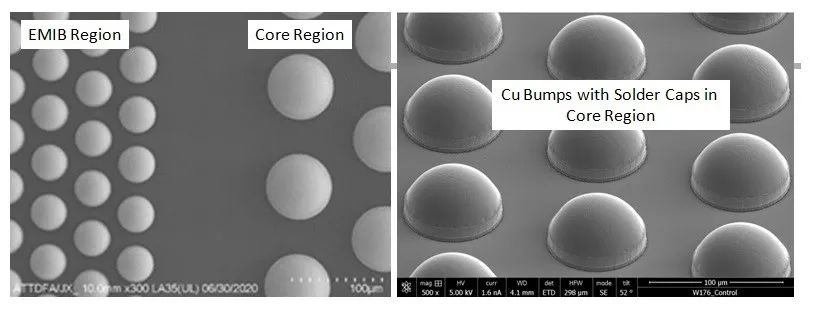

请注意,在上方的横截面图中,粗孔和细孔分别对应于每个die上存在的两个不同的凸点间距,如下所示。

粗大的凸块用于die到封装的走线层连接,而细间距则与EMIB连接相关联-短期内更多关于目标EMIB连接密度的信息。

Ravi补充说:“进行了大量的工程设计,以定义精细和粗糙的凸点轮廓,这些轮廓将支持管芯附着和通过连接处理。具体而言,这包括重点关注凸块高度控制和焊料量。我们已经与bumping 供应商合作,以实现这种dual pitch和profile configuration。此外,MCP封装中的每个裸片都单独连接-裸片上的凸点将经受多个回流周期。注意与凸块结合的助焊剂材料。还已经开发了在整个凸块区域中提供无空隙的环氧树脂底部填充剂的方法。材料,凸块和附着过程都是在大规模生产中进行的。”

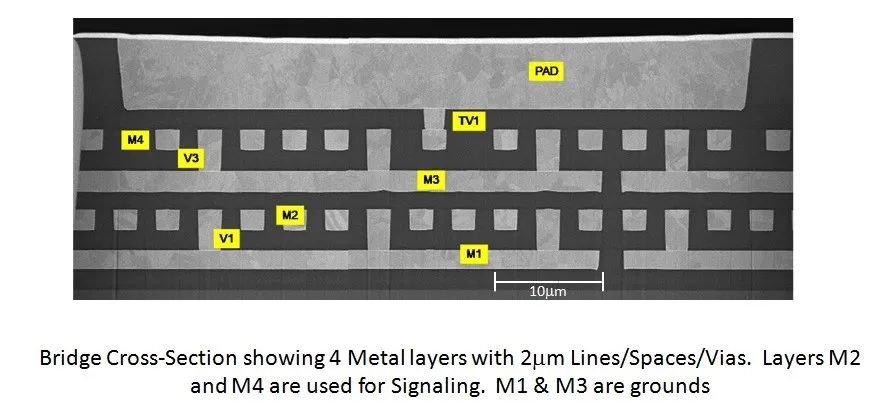

下面显示了一个只做桥的示例。此特定设计实现以下功能:

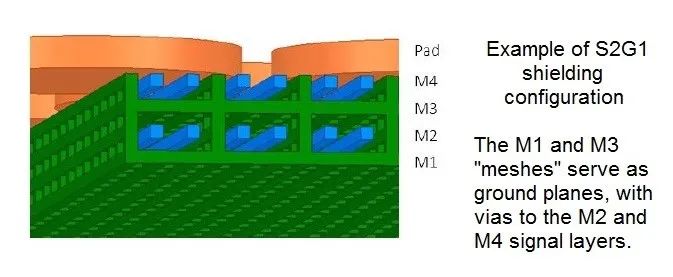

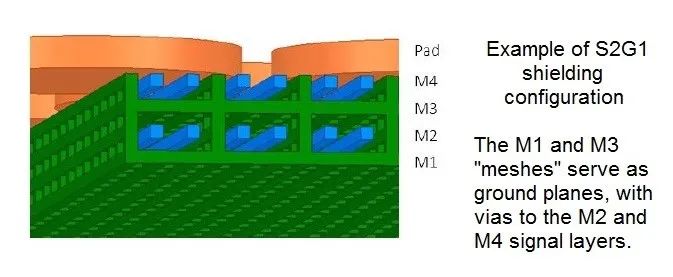

确切地说,如下图所示,备用EMIB层上的金属平面被实现为网格。

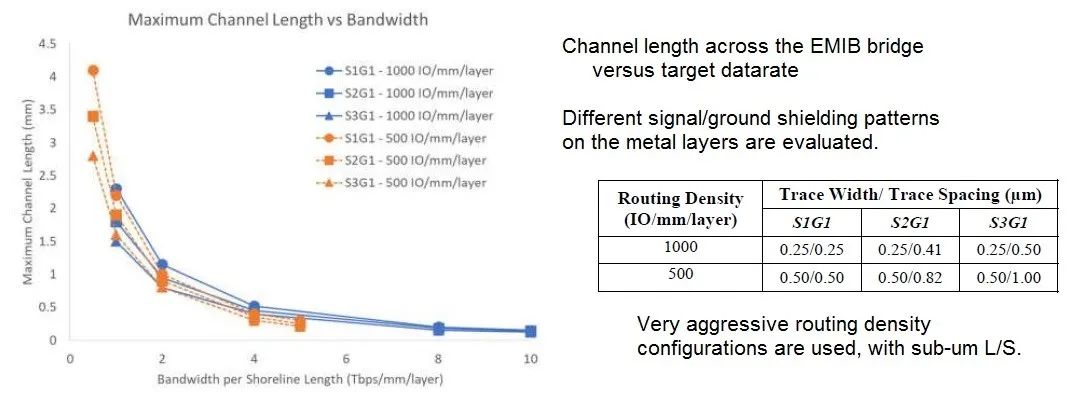

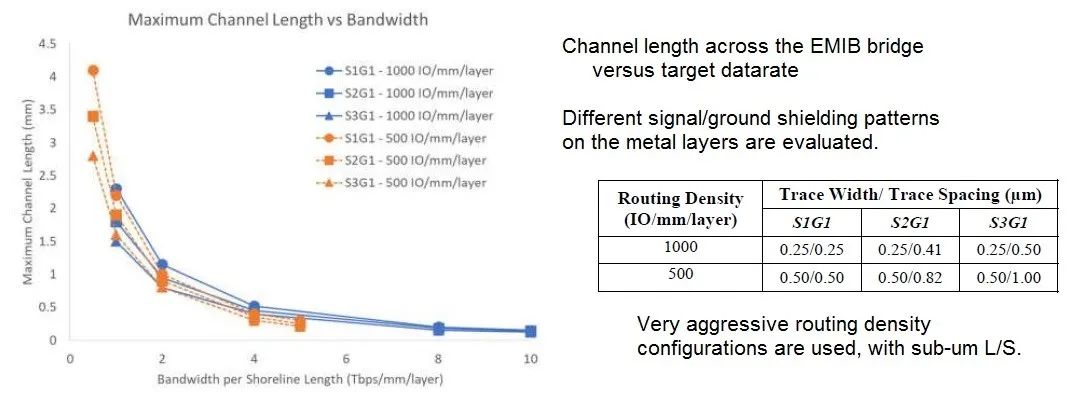

Ravi说:“ EMIB互连的设计是多个目标之间的复杂权衡–互连密度(每毫米边缘的导线数,每毫米的凸点** 2),功率限制和信号带宽。对于每个裸片,这意味着驱动器尺寸和接收器灵敏度。为了节省功率,通常使用无端接的接收器(即,仅容性负载,无电阻端接)。为了解决这些目标,EMIB设计考虑因素包括线和空间尺寸,凸块间距,沟道长度,金属厚度以及金属层之间的介电材料。电信号屏蔽(例如S1G1,S2G1,S3G1)的设计也至关重要。”

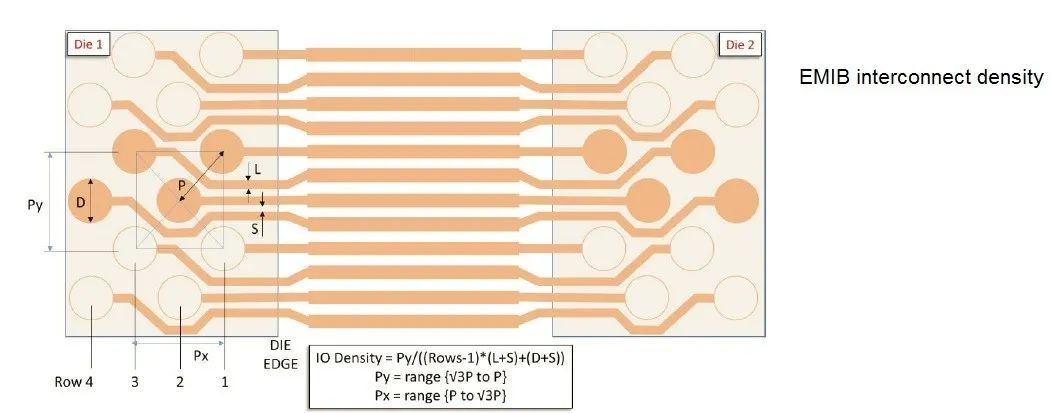

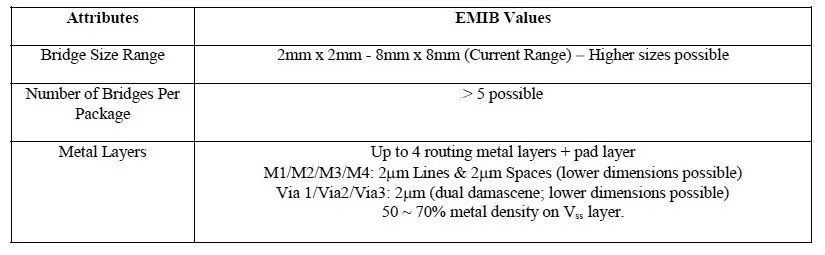

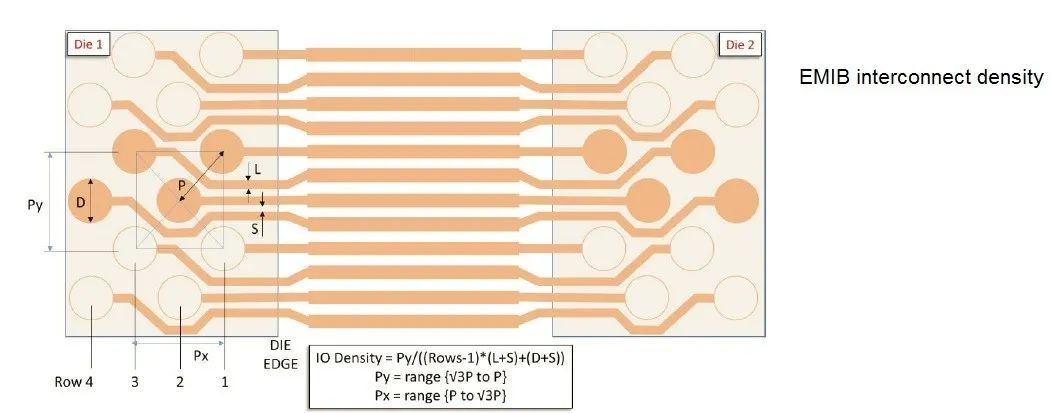

下图显示了互连密度设计的布局图,包括电桥信号如何到达相邻die上的多行细间距凸点。下表说明了可用尺寸和间距的范围。

下图显示了各种桥定位选项。请注意,桥的放置具有很大的灵活性-例如,水平和垂直方向,相对于模具边缘的不对称位置。

英特尔针对EMIB互连发布了详细的电气分析,评估了各种信号接地屏蔽组合和导线长度的插入损耗和串扰。

上图突出显示了封装中的配电路径(power distribution paths )。请注意,EMIB桥的占位面积小,这意味着I / O信号和电源完整性特性的平衡不会受到影响,这与全硅中介层不同,在硅中介层中,所有信号和电源过孔都必须首先穿过中介层。如前所述,EMIB上方的顶层封装层也用作接地层。

下图显示了电分析结果的示例,描述了针对各种信号屏蔽模式的目标累积海滩前带宽的最大EMIB信号长度。在此示例中,采用了激进的L / S线距设计。使用的电气模型:

由于EMIB设计权衡的复杂性,Ravi表示:“英特尔将与代工客户在产品需求方面紧密合作,并将EMIB设计作为一项服务进行开发。我们将与客户一起在die引出线和凸点图案上进行合作,并提供可满足其数据速率目标的EMIB硅实施方案。”

EMIB技术仍然是英特尔的研发重点。Ravi强调说:“我们将继续致力于提供更大的互连边缘密度,包括更紧密的凸块间距和更积极的线/空间EMIB金属间距(小于1um)。将有源电路集成到EMIB中当然也是可行的。”

支持高级MCP技术的EMIB桥接方法具有一些独特的优势:

•现有有机包装技术的扩展

•支持大芯片数和大封装配置

•比全尺寸硅中介层的成本更低

•使用简单的驱动器/接收器电路,支持相邻芯片之间的高数据速率信令

•通过为该链接定制桥来分别优化每个冲模-骰子链接的能力

EMIB链路具有高能效,低金属R * C延迟,最小延迟和高信号完整性。

•芯片凸块和封装组装过程中的额外复杂性

•封装,die和EMIB桥之间的热膨胀系数(CTE)系数不同

EMIB硅在封装组装之前变薄(t <75um),因此不会显着改变封装和管芯以及凸点和底部填充界面之间的热机械应力。总体可靠性可与传统有机包装媲美。

英特尔代工厂服务的封装团队提供的支持将帮助寻求高级MCP解决方案的客户实现其信令数据速率,功耗和成本目标。

毫无疑问,MCP封装采用率的增长将继续加速。(DARPA CHIPS计划还将使人们对MCP设计产生更大的兴趣。)

原文链接:

https://www.semiconductor-digest.com/amazon-aws-is-intel-foundry-services-first-emib-packaging-customer/

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2948内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!