OpenHBI:小芯片互联的理想接口标准

作者:新思科技高级产品营销经理Manuel Mota

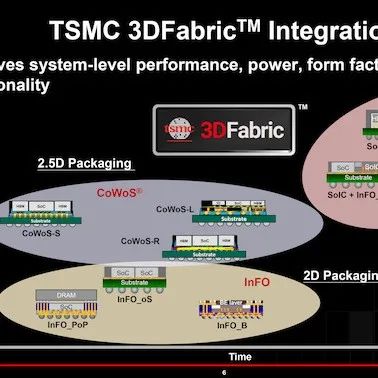

小芯片(Chiplet)已经成为当今大厂角逐的一大方向,对于小芯片来说,需要一种芯片到芯片的互连/接口技术,现在已有多种Die-to-Die接口可以满足这类需求。其中,基于SerDes的或并行的Die-to-Die接口在数据速率、引脚数量和成本等方面都有其独特的优势。但在设计用于诸如数据中心、人工智能 (AI) 训练或推理、服务器和网络等高性能计算 (HPC) 应用的高端Muiti-die SoC时,为了让不同的供应商开发的Multi-Die SoC实现互操作,业界正着力于建立Multi-Die的互连标准,以维护一个成功的生态系统。

在众多Die-to-Die互联标准中,OpenHBI已成为提供最高边缘密度的标准,非常适用于必须在两个Chiplet之间传输极高带宽的HPC应用。

为何使用并行 Die-to-Die 接口?

Die-to-Die接口标准应运而生

什么是 OpenHBI?

-

整合多个OpenHBI兼容的Die-to-Die接口,实现互操作性 -

利用JEDEC HBM3 IO类型和电气特性 -

可与支持HBM存储器和OpenHBI标准的双模HBM主机控制器互操作 -

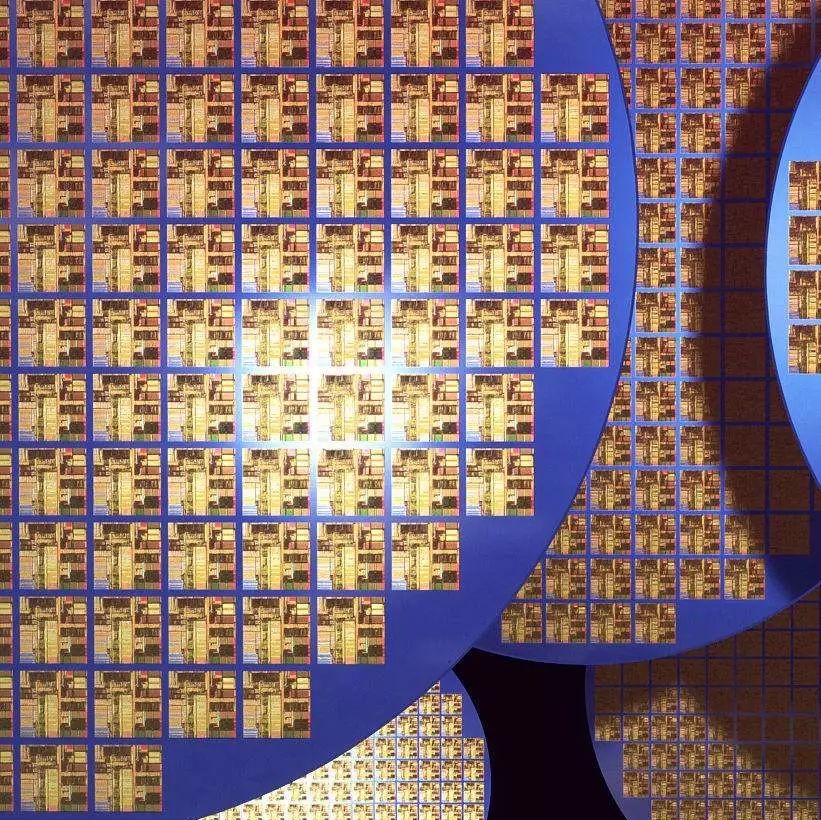

支持硅中介层和晶圆级集成扇出或同等技术 -

实现对称Die-to-Die接口 -

实现目标速度:每引脚 8Gbps,正迈向12-16Gbps -

在最高数据传输速率时提供长达3mm的互连距离 -

实现小于等于0.5pJ/bit的功耗目标 -

提供大于1.5T位/毫米(包括发射器和接收器)的线性(边缘)带宽密度 -

定义 PHY 和逻辑 PHY 抽象层,轻松适配上层 -

支持正常的和旋转的Chiplet方向 -

可以调整带宽和边缘(DW 数量)以匹配各种用例 -

支持小芯片 (Chiplet) 配置和测试 (CCT) 接口 -

支持通道修复,提高制造良率

-

带有APB/TDR接口的配置端口,用于访问内部控制和状态寄存器 (CSR)

-

可配置PHY,支持多种DWORD数量,以适应具体用例

-

裸片测试(已知良好Chiplet)和封装后测试的综合可测试性,包括关键模块 BIST、各种环回模式、模式生成和匹配能力,以及生成重建的眼图,作为 pass/fail 测试。

新思科技IP助力小芯片的互联

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2946内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻